# ON "PASCAL", CODE GENERATION, AND THE CDC 6000 COMPUTER

· BY

# **NIKLAUS WIRTH**

**STAN-CS-72-257 FEBRUARY 1972**

# COMPUTER SCIENCE DEPARTMENT School of Humanities and Sciences STANFORD UNIVERSITY

O. r "PAS" A Code Generation, and the CDC 6000 Computer

by Niklaus Wirth

# Abstract:

"FREE AL" is a general purpose programming language with characteristics similar to ALGOL 60, but with an enriched set of program—and data structuring facilities. It has been implemented on the CDC 6000 computer. This paper discusses selected topics of code generation, in particles of the selection of instruction sequences to represent, simple operations on arithmetic, Boolean, and powerset operands.

Methods to -implement recursive procedures are briefly described, and it is hinted that the more sophisticated solutions are not necessarily also the best. The CDC 6000 architecture appears as a frequent source of pitfelles and nuisances, and its main trouble spots are scrutinized and discussed.

The preparation of this paper was made possible by support from the National Science Foundation, Grant number GJ-992, IBM Corporation, and Xerox Corporation.

On "PASCAL", Code Generation, and the CDC 6000 Computer

# 1. <u>Introduction</u>

This set of notes has a dual purpose. It is on the one hand directed to the <u>user of the PASCAL compiler</u> system who would like to gain some insight into the machine code which is generated for various basic operations. It is even recommended that he study these notes carefully, because their understanding may prevent him from certain pitfalls which are inherent in the use of the CDC 6000 computer [1].

On the other hand the notes-may be of interest to <u>compiler writers</u> in general, because they point out some problems and dilemmas and our choices of solutions. It becomes apparent that the choice of the code to be generated is crucial for a good compiler system, and that it is far **from** trivial as is usually believed.

The true purpose of a higher-level language is that it allows a programmer to conceive his algorithms in terms of some convenient abstractions. For instance, he is given the opportunity to think in terms of familiar notions of numbers, of relations, and of repetitions, instead of having to express his program in terms of bitstrings, arithmetic instructions, and transfers of control. However, these abstractions are only truly useful, if he can assume that his implementation observes all the properties which are commonly attributed to these abstractions, or else if it automatically issues a warning. As an example, when dealing with numbers in a high-level language, one should like to assume all the common axioms of arithmetic to hold. Of course this is not possible, since computers can only represent finite ranges of values. So one expects to receive a warning, if an operation

has trespassed the limits imposed by the implementation and an operation generates a result not in accord with the rules governing the abstraction. So the system is expected to provide an error indication, e.g. if an overflow occurs in an addition, if a value is being assigned which lies outside the specified range of values of variables, or if an array index is used which lies outside the defined limits.

Unfortunately, such potential warnings require the execution of additional instructions, which in general is costly. As far as range checking is concerned, they can be requested to be generated by the compiler for run-time execution by enabling so-called options. (The A-option generates assignment range checks, the X-option index checks.) They are relatively costly, but may speed up the finding of logical mistakes a great deal.

As far as irregularities of the arithmetic are concerned, one has become used to receive these warning signals automatically from the hardware, particularly because they are easily generated by the hardware, whereas a solution to detect overflow by software is usually beyond any reasonably economical feasibility. Unfortunately, the CDC computer fails to satisfy even the most modest expectations in this respect, and the effort to provide a system with security in the above sense was therefore a series of constant frustrations. Equally disappointing are some of the "features" of its floating-point arithmetic instructions.

One can go only a relatively short distance in trying to correct mistakes of the hardware by means of software; otherwise a system becomes ridiculously inefficient and will not be used by conscientious programmers who are willing to take the peculiarities of a hardware into account and guarantee safety of their algorithms by analytical

rather than experimental means. And this would have been against the intentions of PASCAL. So all that can reasonably be done is to elucidate the shortcomings and limitations of the hardware that are still transparent through the "software cover", and to make the programmer fully aware of them. And this is the purpose of this note.

It concerns itself with the simple operations of integer and real arithmetic, with Boolean operations and with powersets. The reader is supposed to be familiar with the CDC COMPASS notation. The operands are usually assumed to have been brought into the Xl and X2 registers. (If they were loaded into other registers, a corresponding renumbering is necessary which is, however, irrelevant to the operation itself). Registers Xl-X5 are used as a stack for intermediate results, whereas XO is used exclusively as local work register.

Section 6 deals with the topic of implementing recursive procedures and the addressing of local variables. Although the general techniques are well-known, analysis of possible solutions and their experimental comparison yielded some noteworthy results. It is shown that attempts to make full use of available hardware features such as base registers may not necessarily lead to an optimal performance. Again, the instruction set of the CDC computer is hardly optimal to implement mechanisms for recursive procedures. Conspicuously absent is a subroutine jump instruction which leaves the code invariant (reentrant).

# 2. Integer Arithmetic

Data of type integer or of subranges thereof are represented by fixed-point binary numbers. Addition and subtraction are represented by the

instructions. Other operations are implemented by short sequences of instructions, as outlined below.

# 2.1 Multiplication

Due to a recent change of the hardware, fixed-point multiplication can be performed by a single

instruction. It should, however, be noted that this instruction is essentially a floating-point instruction, and yields incorrect answers for fixed-point operands with  $|x| \geq 2^{48}$ . This can be regarded as an overflow condition which is, alas, neither trapped nor indicated by the computer. A "safe code", checking against all imposed limits of operands and result, is quite elaborate and uneconomical by any standards, and was therefore not implemented.

If one of the operands is a constant C being representable as either

1.

$$c = 2^n$$

(2, 4, 8, 16...)

2.  $c = 2^m + 2^n$  (3, 5, 6, 9, 10, 12.1)

3.  $c = 2^m - 2^n$  (7, 14, 15...)

then the compiler generates the following code for the multiplication of Xl by c:

Again, overflow conditions are simply ignored. Case 3 yields only correct results, if  $|X1*2^m| < 2^{59}$ .

# 2.2 Division (div)

Integer division is represented by the instruction sequence

and suffers from the same basic shortcoming as multiplication: an operand  $|x| \ge 2^{48}$  yields an incorrect result.

If the divisor is a constant  $c=2^n$ , the **compiler** again produces an "optimized" code, performing division by shifting. Unfortunately, a single right shift instruction is unsatisfactory, because it may generate a "negative" zero as result. Negative zeroes, however, must not be allowed to occur, since comparisons may yield wrong answers if applied to them. Thus, the optimized division is implemented as

Note that the unconditional generation and addition of a zero can be

accomplished with a code that is not only shorter than a conditional jump, such as

but also avoids the insertion of padding instructions (NOPs) for word boundary alignment.

The  $\underline{\text{D-option}}$  provides an additional security measure against division by zero. It causes the compiler to insert a

jump instruction preceding every division instruction. (This applies to the Modulus operation as well.) It is particularly recommended in the case of integer division, where the actual divide instruction generates a "floating-point infinity" value, which is incorrectly treated by the subsequent conversion instructions and thereby represents a senseless result.

# 2.3 $\underline{Modulus}$ ( $\underline{mod}$ )

The modulus or remainder operation is defined as

$$x \mod y = x - (x \underline{div} y) * y$$

As it involves integer multiplication and division operations, it suffers again from the same deficiencies of the 6000 arithmetic. Its corresponding code is:

PXDxl**P**X6 x2**N**X6 **X**6 xo/x6 FX6 B7,X6 UX6 B7,X6 LX6 DX6 X6\*X2 **X1-**X6 IXl

# 2.4 Sign inversion

The use of  $one^\intercal s$  complement representation for negative numbers makes again the most obvious choice of code

BX1 -X1

unsatisfactory, because it might generate a "negative zero". So we use

BXO XO-XO XO-X1

# 2.5 Comparisons

Since the computer does not offer a compare instruction, subtraction has to be used; this has primarily the disadvantage of generating wrong results in the case of overflow. The cases of testing for equality and inequality are handled correctly, because the one's complement addition generates an end-around-carry in the case of "negative overflow", thus maintaining a result indicating inequality. Note that the Boolean subtraction

#### BX1 X1-X2

cannot be used, because a comparison of xl and x2 = -xl would yield a zero result, thus indicating equality.

Whereas equality testing is "safe" with the

# IX1 X1-X2

instruction ignoring overflows, this is not the case for the tests of ordering (xl < x2) by subtraction and subsequent inspection of the sign bit. The reason is that if overflow occurs, i.e.,  $|xl-x2| > 2^{59}$ , then the sign bit will be the opposite of the true sign. This situation is quite hopeless, since overflow is in no simple way detectable on this machine. In order to obtain a (sign) bit representing the relation

x < y for any values x, y, the following algorithm can be used:

- 1. Compare the signs of the two operands.

- 2. If they are different, then the result is obvious.

- 3. If they are equal, the subtraction x-y can be performed without danger of overflow, and x-y < 0 is the result.

A minimal instruction sequence to perform these operations and avoiding the use of undesirable jump instructions is

BX0 X1-X2 compare sign bits

IX2 X1-X2

BX1 XO\*X1 if unequal, choose sign of X1

BX2 -X0\*X2 if equal, choose sign of X1-X2

BX1 x1+x2

Now the sign bit of Xl is 1, if Xl <X2 , and 0 otherwise. Still, the effort to perform a faultless comparison is formidably cumbersome, and the PASCAL compiler does not generate it. The programmer is left with the responsibility to verify that for every comparison of x and y ,  $|x-y| < 2^{59}$ .

# 2.6 Taking the absolute value (ABS)

The code used to take an absolute value is designed to avoid jump instructions, not only because they are long and slow, but because they usually introduce NOP instructions for alignment.

Bxo Xl .

AXO 59 generate 60 sign bits

BX1 X0-X1

# 2.7 Testing for even or odd (ODD)

Since one's complement representation is used for negative numbers, the least significant bit of the operand must be compared with its sign bit:

BXO X1 LXO 59 BX1 X1-XO

This leaves the sign-bit of Xl equal to 1 , if Xl was odd, and 0 otherwise.

The compiler "optimizes" in the case of ODD(x) with x being of a subrange type with only non-negative values. It then generates the single instruction

LX1 59

# 2.8 Summary

The foregoing explanations reveal that the absence of any overflow indication makes analytical verifications necessary that guarantee the non-occurrence of these conditions. An effective aid in experimental testing is the A-option, causing interval check instructions to be generated with every assignment to a variable that is declared to be of a subrange'type. The A-option is activated by the "comment"

and causes the code for an assignment to a variable

to become:

SX7 \* location identification for error trap

SX1 a

1x0 X6-X1

SX1 b

TX1 X1-X6

BX0 X1+X0

NG X0,error jump to error routine

SA6 V

It should be noticed that unfortunately the attractive and shorter code sequence

sx7 \*

sx0 x6-a

SX1 x6-b-1

BX0 -X1+X0

NG X0, error

SA6 v

cannot be used, because the instructions

SXi Xj+K

perform an 18-bit arithmetic ignoring the leading 42 bits of the register Xj which -- of course -- is not in the spirit of a check.

This ignoring rather than checking of the leading bits in 18-bit arithmetic is the reason why the so-called "increment" instructions cannot be used by the PASCAL compiler, except in the following special circumstance: if a variable x is declared of a subrange whose limits are both less than  $2^{17}$  in absolute value, then the assignment statement

x := x + k

is compiled as

SAl x SX6 Xl+k SA6 x

# 3. Floating-point Arithmetic

The PASCAL compiler uses the canplete set of F-instructions for arithmetic with values of type "real". Comparison is performed by subtraction due to the lack of a compare instruction. This is possible without handicap since the occurrence of overflow generates a <a href="signed">signed</a> "infinity" -value, but no immediate trap. Sign inversion is represented by

BXO XO-XO generate zero XX1 XO-X1

and the absolute value function by

BXO X1 AXO 59 BX1 XO-X1

Arithmetic with the F-instruction possesses some peculiar properties which will briefly be reviewed, and has for instance the consequence that x-y=0 does not necessarily imply x=y, if the difference is computed by an Finstruction. The trouble arises from the fact that F-arithmetic truncates without rounding, and F-addition truncates without post-normalization. Every addition is therefore compiled into two instructions:

$\begin{array}{ccc} \text{FXl} & \text{Xl} + \text{X2} & \text{add/subtract} \\ \text{Nxl} & \text{Xl} & \text{post-normalize} \end{array}$

If the two values

$a = 1720 \ 40...00B = 1.0$

$b = 1717 \, 17 \dots \, .77B = 1.0 - 2^{-48}$

are compared by subtraction

FXO X1-X2 a-b

the result is

where the slash marks the separation between the lower and the upper half of the 96-bit accumulator. The result is 0 although the two operands were different.

Notice that subtracting  $0.5 \text{ from } \underline{\text{both}}$  a and b , and then computing their difference, yields

i.e., a difference which is <u>not</u> zero. Thus the result does not only depend on the true result, but also on the values of the operands.

This unpleasant, property of the CDC F-arithmetic stems from the fact that automatic post-normalization is absent.

# 3.1 Rounding

It was at one time hoped that this defect could be avoided by letting the PASCAL compiler automatically generate R-instructions, which include a certain kind of rounding. However, R-arithmetic turned out to feature some even stranger properties, so that it was decided not to use R-instructions. In order to point these features cut, a brief review over R-arithmetic is necessary:

The R-instructions differ from the F-instructions only insofar as a 1-bit is appended to normalized operands before the arithmetic operation is performed. Thus for instance the subtraction of  $b = 1.0-2^{-48}$  from a = 1.0 yields

which of course is still zero.

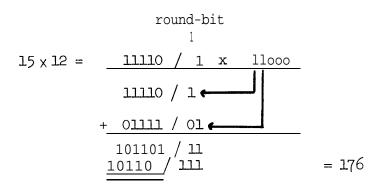

The principal defect with "CDC-rounding", however, is that its effect is unpredictably either the addition of 1/2 or 1/4 in the last position, because rounding takes place <u>before</u> instead of after normalization (which must again be performed by a separate instruction). The following example illustrates this, which is shown on hand of a five-bit number representation:

In the first case, the pre-rounding results in correct rounding of the not exactly representable 33 to 34 , whereas in the second case pre-rounding has no effect.

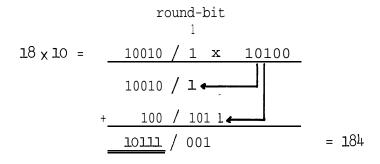

The same phenomenon can be observed in the cases of multiplication and division. The following example again uses a five-bit number representation:

In the first case, the rounding effect is nil, leaving the inexactly representable value 180 be an unrounded 176; in the latter case the rounding effect transforms 180 into the value 184. (Suitable adjustment of exponents is not shown here.)

A method introducing proper rounding instead of "CDC-rounding" relies on the use of the D-instruction set [2]. Whereas the F-instructions yield the high-order 48 bits of the 96-bit accumulator, the D-instructions yield the low-order 48 bits with a suitably adjusted exponent, thereby allowing access to a double precision result.

Notice that it is an ingeniously efficient method to compute a double precision result by

- computing the DP-result and dispose of the low half (F-instruction), then

- computing the same again and dispose of the high half (D-instruction).

This computer allows it to be done in no other way!

The PASCAL compiler will generate the following code for **floating-** point operations, depending on the choice of the <u>R-option</u>:

| R-option     | OFF                  | ON                                                          |

|--------------|----------------------|-------------------------------------------------------------|

| х <u>+</u> у | FXl x1+_x2<br>NXl Xl | FXO x1+ x2<br>Nxo X0<br>DX1 x1+ x2<br>RX1 X1 + X0<br>NX1 X1 |

| х * у        | FX1 X1 * x2          | FXO x1* x2<br>DX1 x1* x2<br>RX1 x1+ XO                      |

| х / у        | FXl Xl/x2            | RX1 <b>X1</b> / x2                                          |

Examples of addition/ subtraction:

1.

$$\frac{1.0 - 2^{-48}}{1.0 - 2} = \frac{1720 + 0... + 00 / 00... + 0}{1717 + 77... + 077 / 00... + 0}$$

$$\frac{1720 - 37... + 00... + 0}{1720 - 37... + 00... + 0}$$

$$= 1640 + 40... + 00$$

after addition of high and low

2. Take a = 1.0 and  $b = 2^{-48}$ , then subtract a-b:

F-subtraction yields

$$a = 1720 \quad 40... \quad ...00 \ / \ 00... \quad ... 0$$

$b = 1720 \quad 00... \quad ...00 \ / \ 40... \quad ... 0$

$1720 \quad 37... \quad ...77 \ / \ 40... \quad ...$

which, after normalization, is

$$1717 \quad 77... \quad ...76 = 1.0-2^{-47}$$

R-subtraction inserts a 1-bit after the slash in the first operand, and thus yields the result

The combined use of F and D instructions yields the true result, because the normalization instruction left shifts the high order result to

whereafter a "rounded" -addition is used to add the correction

yielding

$$1717 \quad 77... \quad ...77 = 1.0-2^{-148}$$

# 3.2 Conversion from fixed to floating-point (integer to real)

Wherever a real operand is permissible, PASCAL allows the specification of an operand of type integer as well. However, the compiler is theh forced to generate the necessary representation conversion instructions, which are not only time-consuming, but potentially hazardous. It is therefore recommended to avoid "mixed-mode" arithmetic expressions wherever possible. The generated conversion instructions are

The result of this conversion is wrong, whenever the integer operand in Xl is larger or equal to  $2^{48}$  in absolute value, since the exponent bits are simply <u>ignored</u> by the **P** instruction. A test to verify that the operand is within bounds could be compiled as

but is easily seen to be more costly than the conversion itself.

# 3.3 Conversion from floating to fixed-point (real to integer)

PASCAL does not provide for any implicit real to integer conversion. However, the standard function TRUNC(x) allows to truncate the fractional part of a real number. The used code is:

The result of this conversion is again wrong, if  $|x| \ge 2^{48}$ .

# 4. <u>Boolean Operations</u>

The standard type Boolean is defined in PASCAL as

Since the values of all scalar types are mapped onto the integers  $0,1,2,\ldots$ , the values <u>false</u> and <u>true</u> are represented by the numbers 0 and 1 respectively.

The operations  $\ \ \, \Lambda \ \,$  and  $\ \ \,$  are implemented by the Boolean AND and OR instruction, namely

Negation is performed by

If a relation has to be assigned to a Boolean variable, e.g.

$$b := x < y$$

then a sequence of instructions is necessary to obtain a 0 or 1 value. Again every effort is made to avoid the use of jumps. The following code is used in the above assignment; leaving a Boolean value in Xl .

Analogous code is generated for the relations > ,  $\leq$  , and  $\geq$  . But unfortunately the equality relations cannot be reasonably implemented without a jump; in the assignment

$$b := x = y$$

the following instructions are generated:

Boolean comparisons, although occurring rather infrequently, are treated as special cases, because a simpler and shorter code is applicable:

$$\begin{array}{cccc} p < q & & BX1 & -X1*X2 \\ \\ p \leq q & & BX1 & -X2*X1 \\ & & MX0 & 59 \\ & & BX1 & -X0-X1 \end{array} \right\} \text{ negation} \\ \\ p \neq q & & BX1 & X1-X2 \end{array}$$

The remaining three relations are compiled analogously.

#### 5. Powerset Operations

PASCAL 6000 restricts powerset types to be built only on base sets with less than 59 components. This allows a powerset value S to be represented by one "word", in which the i-th bit indicates the presence (1) or absence (0) of the element i in S.

# 5.1 Generation of the Singleton Set [i]

Assume that i is loaded into register Xl, then

SB7 X1 SX1 1 LX1 B7,X1

Notice that the numbering of bits starts with 0 at the low order end. This choice was made in order to be able to load powerset constants with small valued components (less than 18) by a single SXi instruction.

# 5.2 Set Intersection, Union, and Difference

These three operations are implemented by a single instruction

intersection BXl x1\*x2

union BXl x1+x2

difference BXl -X2\*Xl

#### 5.3 Set Membership (in)

The relation i  $\underline{\text{in}}$  S is implemented by shifting the bit representing i into the sign position which can be tested:

SB7 X1 i AX1 B7,X2 S LX1 59

If the expression i is in the form of a constant c , then the compiler generates of course only the single instruction

LX1 59-c

# 5.4 Set Comparison

Sets can be compared for equality and inclusion. <u>Equality</u> is tested by a Boolean subtraction

BXO X1-X2

and a subsequent zero test. Note that the peculiar property of the zero test to recognize a word with either 60 zero-bits or 60 one-bits as a zero is responsible for the restriction that powersets may contain at most 59 instead of 60 elements. If sets with 60 components were allowed, then a full set and an empty set would not be distinguishable by a single subtraction followed by a zero-test.

$\underline{\text{Inclusion}} \ \text{expressed as } x \leq y \ \text{and meaning} \ x \subseteq y \ \text{, is implemented}$  by the single instruction

BXO -X1\*X2

which is followed by a zero-test instruction. The same instruction is used for the relation x > y, whereas strict inclusion  $(x \subset y)$  is not implemented.

# Some Exercises Addressed to the CDC 6000 Expert

1. Is the following code to represent the function trunc(X1) acceptable? If not, why?

BXO XO-XO

PXO XO

FX1 X1+XO

UX1 B7,X1

NZ B7, overflow

2. Is the following code for Xl mod X2 acceptable? If so, prove it.

PX1Xl Px2x2NX6 x2fx6 **X1/X**6 Bxo ΧO x6+x0 FX6 DX6 X6\*X2FX6 x1**-**x6 х6 UXl

3. Why can the instructions

BXO X1-X2 ZR X0, equal

not be used to represent a comparison Xl = X2 ? Prove that

1x0 X1-X2 ZR X0, equal

always yields the correct action.

# 6. Irnplementation of Recursive Procedures

The language PASCAL has been carefully designed so that dynamic storage allocation is not required, with the following two exceptions:

- Variables local to procedures may be allocated storage only when the procedure is called, and

- 2. Components of class variables are allocated storage by calling the standard procedure "alloc". An area of store is allocated to the entire class variable as soon as the procedure is called to which the class is local.

In this section we will briefly review the well-known techniques for handling recursive procedure calls and of allocating storage to their local quantities, and discuss the code selected to represent the procedure call mechanism.

Due to the first-in last-out nature of the hierarchy of activated procedures a stack may be used to allocate local variables. This is of great advantage, since storage retrieval is trivial in the case of stacks, resulting in low storage management overhead. We consider the set of local variables of each activated procedure as a record (often called "data segment") in the stack. Since their lengths may all be different, the most convenient method to thread the way back through such a stack is by constructing a chain of pointers linking the records. Every record then contains a "header" containing

- 1. the link to the previous record, and

- 2. the (frozen) program status (counter) of the calling procedure.

Variables are addressed relative to the origin of the record of which they are a part. The origin address is unknown at compile-time,

and must be determined at run-time. This can be done by descending through the link chain, until the desired record is reached. But how is the desired record recognized'? The most straight-forward method which interprets the scope rules of an ALGOL block structure correctly is probably the following:

## Method I:

- 1. Define the level of an object to be 1 greater than the level of the procedure to which it is local. The level of the main program is 0.

- 2. Indicate the level of each record (equal to the level of its components) in its heading.

- Whenever an object on level i has to be accessed, the record containing it is found by descending down the chain of links until the first occurrence of a level indicator with value i is found.

This accessing method has the obvious drawback of inefficiency (and of not being applicable in the case of parametric procedures). A slight modification, however, improves efficiency and generalizes to parametric procedures.

#### Method II:

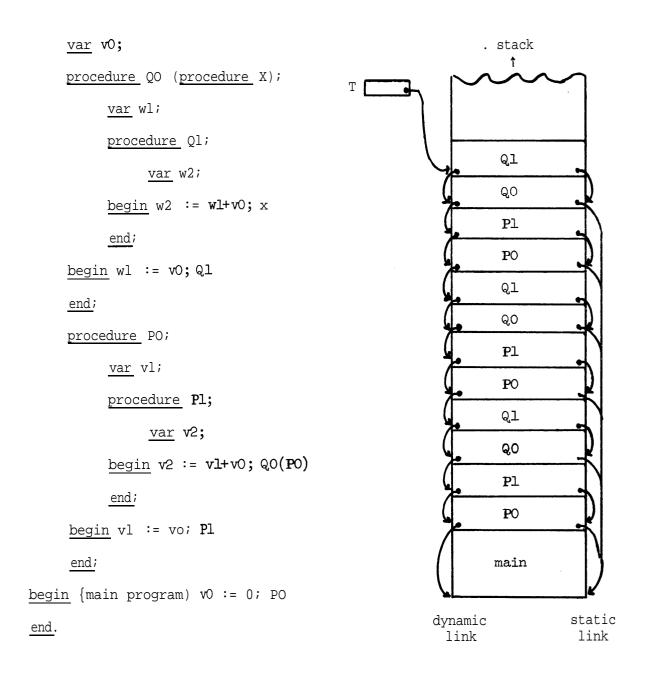

Instead of indicating levels explicitly in the record headings, a second link chain is constructed commecting each record A with its static ancestor, i.e., with the record B of the procedure in which A was declared locally. In order to distinguish the two link chains, the former is called the "dynamic link" and the latter the "static link". An example of a state of computation is shown below for a given -- admittedly not very realistic -- program.

#### Method III:

Although the use of a high-speed index register to represent the origin of the link chains improves access speed significantly, the process of descending down the static chain to the record (data segment) with the desired level is relatively time-consuming. An ingenious device to reduce access time was introduced by Dijkstra [4] and is now widely used in compilers for block-structured languages. The device

is an array of base addresses, called the Display D , which is at any time a copy of the static chain. If an object at level i is to be accessed, the origin address of its data segment is quickly obtained as D<sub>i</sub> . The method is particularly attractive for computers with a set of high-speed index registers which can be used as the Display. The price for this increase in access speed -- apart from the reservation of registers -- is the setting and updating of the Display each time a procedure is called and terminated. To be more specific, the necessary actions are as follows:

- 1. if an actual procedure of level i is called,  $\mathbf{D_i}$  has to be set;

- 2. if control is returned from a procedure at level i to one at level j , (j $\geq$ i) , D<sub>i</sub> ...D<sub>j</sub> have to be reassigned;

- if a formal procedure at level i is called **from** a procedure at level j ,  $D_i$  . . .  $D_k$  have to be reassigned, where k is the level on which the static link emerging **from** the calling and the called procedures merge. Since k is not known at the time the procedure declaration is compiled, k can be chosen as zero without significant loss in efficiency.

This scheme was used in the implementation of PASCAL 6000. It is described in Reference 4. Registers Bl...B5 are used as the Display, B5 is the origin of the link chains, and B6 is the pointer to the top of the stack. The compiled instructions are the following:

Procedure call of P:

Procedure entry:

Procedure exit:

Notice that global variables in the main program are assigned absolute addresses. Since  $BO \equiv 0$  , they can be considered as based on BO .

In the first half of 1971, Prof. C. A. R. Hoare and his collaborators modified and bootstrapped the PASCAL compiler for the ICL 1966 computer [6]. One of the more significant alterations concerned the elimination of the Display, due to the fact that the ICL computer has no set of index registers that are available for a Display, and since the use of a Display was not considered to be an advantage, in this case. During a visit of Prof. Hoare in July 1971, he suggested that maybe even with a register set available for the Display, the benefits gained should be investigated. His suggestion was certainly valid, since variables either global or local to the most recently called procedure could be accessed with the same speed even without a Display. Thus the gain from a Display is limited to faster access of objects at intermediate levels, while the price is the updating at every call regardless of whether such objects are accessed or not. A superficial look at the PASCAL compiler itself showed that accesses to such intermediate level objects were indeed relatively rare, and it was decided to generate a version that would not use a Display (Method II). This version still uses the address register B5 as origin of the link chains (and base address of the most local data segment) and B6 as pointer to the top of the stack. The generated code is:

Procedure call P

L

```

* X6 := base of environment of P

SX7 L

EQ P

```

Procedure entry:

Procedure exit:

Fetching an object x at level j from code at level i:

- 1) j = 0: SAL BO+x

- j = i: SAl B5+x

A comparison of the codes generated by the two compilers shows that gains and losses of execution speed should be measured, but also those of code length. The shorter codes for procedure entry  $(2 - 2\frac{1}{4})$  words vs. 4 - 6 words), procedure exit (2 vs. 3 words), and procedure calls (no updating of display) are very attractive, particularly in a compiler where space is more on a premium than time. (It should be noted that the instructions marked with an asterisk can be omitted in the call or the entry code of procedures declared on the first level). Of course it must be kept in mind that the decision about which compiler is to be preferred depends not only on the weighting of space vs. time, but even more on the programs to be processed. But it is obvious that if the

majority of these programs rarely use nested procedure declarations, and often call procedures on the same level, then the compiler without. Display is to be preferred. The compiler itself, although featuring nested procedure declarations, but seldom accessing intermediate level variables, belongs to this class. Comparisons of code generated by the two compiler versions produced the following results:

- 1. The efficiency of codes not using a Display is in the average slightly higher (the compiler itself runs about 1.5% faster).

- 2. The size of codes not using a Display is smaller (by about 4% measured on 25 sample programs, about 6% in the case of the compiler's code).

- The compiler program itself is slightly less complex without Display.

This episode where a more sophisticated method was abandoned in favor of a simpler and more direct technique could well be added to the list of D. Knuth's examples of adverse influences of "computer science" on "computer usage" [5]. Their common characteristic is that improved methods are adopted without closer inspection of the nature and direction of the improvement, and without analysis of the circumstances to be improved. An interesting fact is that the Burroughs B5500 computer -- specifically designed for ALGOL implementation -- did contain exactly the two base registers required to efficiently address objects at levels 0 and i . Unfortunately, addressing of intermediate level objects was impossible due to the software; this deficiency was justifiably criticized. The remedy adopted in the successor B6500 was, however, not a correction of the deficient software, but the inclusion of a full set of high-speed registers to serve as Display.

# 7. Summary of the Main Trouble Spots of the CDC 6000 Architecture

- 1. Use of one's complement arithmetic. In order to keep comparisons simple and efficient, the occurrence of negative zeroes must be prohibited. (Note that PL and NG test the sign bit only.) Various optimizations are more cumbersome and less effective, because negative zeroes must be suppressed by additional instructions.

Some instructions are themselves unsafe against the generation of -0!

- 2. No overflow check on fixed-point arithmetic. This lack is very serious and may cause wrong restuls in totally unexpected situations. Overflow check by software is prohibitive.

- 3. No compare instructions. The use of subtraction may cause wrong results, unless expensive precautions are taken.

- 4. Use of 48-bit multiplier and divider for fixed-point 60-bit numbers without warning of possible "overflow" of operands.

- 5. Floating-point addition and subtraction without automatic post-normalization.

- 6. Floating-point arithmetic with rounding of operands instead of rounding postnormalized results.

- 7. No subroutine jump instruction depositing the program counter P in an operand register, and no return jump loading P from a general operand register. This defect requires the use of 3 instructions each to jump and deposit a return address, and to retrieve it and return, whereas many other computers need only a single instruction for these purposes.

## Conclusions

When considering these complaints, the reader should bear in mind that this computer's architecture was conceived in the very early 1960's. The CDC 6600 machine was a very advanced design for a special purpose: fast number crunching. The design relied heavily on the use of several arithmetic units working simultaneously ("in parallel"). Integer arithmetic was considered as almost dispensible, and overflow interrupts as undesirable, because of the impossibility to mirror the present state of the entire machine by a simple program counter and of resuming compu-The use of simultaneously operating units is apparently also tation. made responsible for the otherwise incomprehensible absence of postnormalization, namely because the unit for floaint-point addition does not contain a left-shift circuitry. A few years later, the CDC 6400 (and 6500) computers were announced; they were to have the same instruction set as the 6600, but only one conventional integrated arithmetic-logical unit. Although the "reasons" for the absence of interrupts and postnormalization had vanished, these "features" were retained in the name of compatibility. It was apparently considered most important that pitfall loaded programs could be transported to the new machines at no extra cost. This policy of staying "upward compatible with all previous mistakes" was sternly maintained when the successor to the 6000 series was announced in 1971.

This attitude, which is by no means atypical among computer manufacturers, makes it doubtful whether any progress toward more reliable and more efficient computing will ever be achievable. It does not seem so, until the computer consumers' attitudes will no longer justify the present manufacturers' policies. They, in turn, will not

change before they are made aware of the hidden cost involved in using the present equipment. I am convinced that the cost incurred by the programmers having to discover bugs the hard way by reprogramming repeatedly, and having to reexecute programs many times until they were believed to be correct, is incomparably higher than the reduction in cost due to staying compatible with outdated architectures. The project to develop the PASCAL compiler for the CDC 6000 computer unfortunately provided ample support for this conviction.

# Acknowledgments

I am grateful to W. Kahan for pointing out some additional problems with the CDC floating-point arithmetic as well as the method for obtaining correct rounding.

#### References

- [1] N. Wirth, "The programming language PASCAL", ACTA INFORMATICA, Vol. 1, 35-68 (1971).

- [2] D. S. Lindsay, "A rounded arithmetic FORTRAN compiler for CDC 6000 machines", U. of California, Berkeley, Dec. 1971.

- [3] B. Randell and L. Russell, "ALGOL 60 implementation", Acad. Press, 1964.

- [4] N. Wirth, "The design of a PASCAL compiler", Software Practice and Experience, Vol. 1, [1971].

- [5] D. E. Knuth, "The dangers of computer-science theory", unpublished paper, August 1971.

- [6] J. Welsh and C. Quinn, "A PASCAL compiler for ICL 1900 series computers", Dept. of Computer Science, Queen's University, Belfast, Sept. 1971.

```

005001 ($C+

T1: EXPRESSIONS AND ASSIGNMEWS }

005001

VAR I, J, K: INTEGER;

005004

X,Y,Z: REAL;

N: 0..9999;

005007

P,Q: BOOLEAN;

005010

BEGIN { REAL ARITHMETIC 3

005012

x = 1.0; Y = x + 3.14159; Z = X + Y + X/Y;

005076

x := x + (Y + (Z + (1.0 + X)));

005105

x = ABS(+Y); Y = SQR(X); Z = -X;

005112

{$R+ ROUNDED REAL ARITHMETIC}

005117

X = Y + Z; X = Y+Z; X = Y/Z;

005117

{ INTEGER ARITHMETIC }

005127

005127

I = 1; J = I + 100; K = I + J; K = I DIV J;

K = (-J) MOD K; J a = SQR(J);

005140

I = TRUNC(X); Z = I; X = I/J;

005145

005154

₹ BOOLEAN ARITHMETIC 3

P #= TRUE; Q #= P A "(Q VP);

005154

P = x = Y; P = I = J; Q = P = Q;

005160

P := X < Y; P := I < J; Q := P < Q;

005171

P = x \leq Y; P = I \leq J; Q = P \leq Q;

005200

Q := ODD(I);

005210

{ OPTIMIZATION OF INTEGER ARITHMETIC }

005212

I a= I*8 + J*10;

005212

J := I DIV 8 - N OIV 2; K := I MOD 16;

005216

005223

N = I + 100

005223

END •

005103

B0+005005

005074

SA3

SA7

85+80

FX2

X2/X3

SX7

B5+B0

FX1

X1+X2

005104

SA7

80+005000

NX6

B0.X1

005075

SB6

85+000001

B0+005006

SA6

B0+005225

NO

SA1

005076

005105

SA1

BX6

Xi

80+005004

B0+005004

SA2

80+005005

SA6

005106

NO

SA3

80+005006

005077

SA1

B0+005004

SA4

B0+005225

SA2

B0+005226

005107

SA5

BO+005004

005100

FX1

X1+X2

FX4

x4+x5

NX6

80,X1

NX4

B0, X4

SA6

B0+005005

005110

FX3

x3+x4

005101

B0+005004

NX3

B0, X3

SAI

SA2

B0+005005

FX2

X2+X3

NX2

B0, X2

005102

FX1

X1*X2

005111

B0+005004

FX1

SA2

X1+X2

NO

NX6

B0,X1

SA6

B0+005004

```

|            |                    |        | SA1              | B0+005001              |  |

|------------|--------------------|--------|------------------|------------------------|--|

|            | _                  | 005130 |                  |                        |  |

| SAI        | B0+005005          |        | SXO              | 80+000144              |  |

| BXO        | хi                 |        | IX6              | X1+X0                  |  |

| AXO        | <b>73</b>          | 005121 | NO               |                        |  |

| BX6        | X0-X1              | 005131 | CAC              | 004000000              |  |

| SA6        | B0+005004          |        | SA6<br>SA1       | 80+005002<br>80+005001 |  |

| NO         | DU TU DU T         | 005132 | SAT              | 80400001               |  |

|            |                    | 000102 | SA2              | <b>BP</b> +005002      |  |

| SA1        | 80+005004          |        | DX1              | X1*X2                  |  |

| FX6        | X1*X1              |        | 0x0              | X0-X0                  |  |

| NO         |                    | 005133 |                  |                        |  |

|            |                    |        | IX6              | X1+X0                  |  |

| SA6        | B0+005005          |        | SA6              | B0+005003              |  |

| SA1        | 80+005004          |        | NO               |                        |  |

| 0 V 4      | VA VA              | 005134 |                  | 202224                 |  |

| BXO        | X0-X0              |        | SA1              | B0+005001              |  |

| IX6        | X0-X1              | 005405 | SA2              | 80+005002              |  |

| SA6        | B0+005006          | 005135 | PX2              | B0 Y2                  |  |

| SA1        | B0+005005          |        | NX2              | B0,X2<br>B0,X2         |  |

| SA2        | B0+005006          |        | PX1              | B0,X1                  |  |

| SAL        | BU + U U D U U     |        | FXI              | X1/X2                  |  |

| FXO        | X1+X2              | 005136 | LVT              | V11 VE                 |  |

| NXO        | BO,XO              | 003130 | UX1              | 87,X1                  |  |

| DX1        | X1+X2              |        | LX1              | 87,X1                  |  |

| RX1        | X9+X 1             |        | 0x0              | X0-X0                  |  |

|            |                    |        | IX6              | X1+X 0                 |  |

| NX6        | B0,X1              | 005137 |                  |                        |  |

| SA6        | B0+005004          |        | SA6              | 80+005003              |  |

| NO         |                    |        | SAI              | 80+005002              |  |

|            |                    | 005140 |                  |                        |  |

| SA1        | B0+005005          |        | BXO              | X0-X0                  |  |

| SA2        | B <b>0+</b> 005006 |        | IX1              | X0-X 1                 |  |

| <b>TIT</b> | V4 # V 5           |        | SA2              | 80+005003              |  |

| FXO        | X1*X2              | 005141 | DVA              | 00 40                  |  |

| DX1        | X1*X2              |        | PX6              | 80,X2                  |  |

| RX6        | X0+X1              |        | NX6              | 80,X6                  |  |

| NO         |                    |        | PX0<br>FX6       | B0,X1<br>X0/X E        |  |

| SA6        | 80+005004          | 005142 | FAO              | AU/A E                 |  |

| SA1        | B0+005005          | UUJ142 | UX6              | 87,X6                  |  |

| 3 M T      |                    |        | LX6              | 87, X6                 |  |

| SA2        | B0+005006          |        | DX6              | X2*X6                  |  |

| RX6        | X1/X2              |        | IX6              | X1-X6                  |  |

| NO         |                    | 065143 | LAU              | n2 NU                  |  |

| 110        |                    | 000110 | SA6              | 80+005003              |  |

| SA6        | 80+005004          |        | SA1              | 80+005002              |  |

| SX6        | 80+000001          | 005144 | - · <del>-</del> |                        |  |

| -          |                    | ,-     | DX6              | X1*X1                  |  |

| CAO        | 80+005001          |        | SA6              | 80+005002              |  |

| SA6        | TODGOGAG           |        | DAU              | 00.007007              |  |

| ,         |                        |          | NO          |                         |  |

|-----------|------------------------|----------|-------------|-------------------------|--|

| SA1       | 80+005004              | 005163   | NO          |                         |  |

| UX1       | B7,X1                  | 000100   | SA6         | BO+005010               |  |

| 1x1       | 87,X1                  |          | SAI         | B0+005001               |  |

|           |                        | 005164   |             |                         |  |

| 0x0       | X0-X0                  |          | SA2         | B0+00500 2              |  |

| IX6       | X1+X0                  |          | 1x0         | X1-X2                   |  |

| SA6       | 80+005001              |          | <b>MK6</b>  | 00                      |  |

|           |                        | 005165   |             |                         |  |

| SA1       | 80+005001              |          | NZ          | X0,005166               |  |

| 8X6       | X1                     |          | SX6         | B0+000001               |  |

| PX6       | 80,X6                  | 005166   |             | 00.005040               |  |

|           | ve                     |          | SA6         | 80+005010               |  |

| NX6       | 80,X6                  | 007407   | SA1         | 80+005010               |  |

| SA6       | 80+005006              | 005167   | CAS         | B0+005011               |  |

| NO        |                        |          | SA2         |                         |  |

| <u> </u>  | 004005004              |          | BX1<br>MKO  | X1-X2<br>73             |  |

| SA1       | 80+005001<br>80+005002 | 005170   | MAU         | 13                      |  |

| SA2       | DU TU U DU U C         | 003170   | вх6         | 7X1-X0                  |  |

| PX2       | 80,X2                  |          | SA6         | B0+005011               |  |

| NX2       | 80,X2                  |          | NO          | 30.0070TT               |  |

| PX1       | B0,X1                  | 005171   | 110         |                         |  |

| NX1       | B0,X1                  | 007212   | SA1         | 80+005004               |  |

| 17.4      | ou y n a               |          | SAZ         | B0+005005               |  |

| RX6       | X1/X2                  | 005172   | 0           | 00100000                |  |

| SA6       | B0+005004              | 003172   | FX1         | X1-X2                   |  |

| NO        |                        |          | MXO         | 01                      |  |

|           |                        |          | % <b>X6</b> | XBAX1                   |  |

| SX6       | 80+000001              |          | LX6         | 01                      |  |

| SA6       | 80+005010              | 005173   |             |                         |  |

| -         |                        |          | SA6         | 80+005010               |  |

| SA1       | B0+005010              |          | SA1         | <b>80+00500</b> 1       |  |

| SA2       | 80+005011              | 005174   |             |                         |  |

|           |                        |          | SAZ         | B0+005002               |  |

| SA3       | B0+005010              |          | 1x1         | X1-X2                   |  |

| 0x2       | X2 <b>×</b> X3         |          | HXO         | 01                      |  |

| MX0       | <b>73</b>              | 005175   | <b>.</b>    | VA. V4                  |  |

|           | <b></b>                |          | BX6         | X8^X1                   |  |

| 0x2       | 7X2-X0                 |          | LX6         | 01                      |  |

| BX6       | X1^X2                  | 001450   | SA6         | 80+005010               |  |

| SA6       | B0+005011              | 005176   | CA 4        | 20±00E040               |  |

| 0.1.4     | 00.005004              |          | SA1<br>SA2  | 80+005010<br>80+0050 11 |  |

| SA1       | 80+005004              | UUE 1 77 | SMZ         | <b>9878878</b> ±±       |  |

| SA2       | BO+005005              | 005177   | вх6         | 7X1^X2                  |  |

| TVn       | V4_V2                  |          | SA6         | B0+005011               |  |

| IXO       | X1-X2                  |          | SAO<br>NO   | 004003077               |  |

| MK6<br>NZ | 00<br>X0,005163        |          | NU          |                         |  |

| 17 4      | VATOR                  |          |             |                         |  |

| SX6       | 80+000001              |          |             |                         |  |

|           | 50.0000                |          |             |                         |  |

| NO        |                        |          |             |                         |  |

| 005200                             |                                                                                                      |                                                                                           |        | SA1        | 80+005001       |

|------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------|------------|-----------------|

| 000200                             | SA1                                                                                                  | B0+005004                                                                                 | 005216 |            |                 |

|                                    | SA2                                                                                                  | 80+005005                                                                                 | 009210 | AX1        | 03              |

| 007004                             | SMC                                                                                                  | 80 + 00 90 0 9                                                                            |        |            |                 |

| 005201                             |                                                                                                      |                                                                                           |        | BXO        | X0-X0           |

|                                    | FX1                                                                                                  | X2-X1                                                                                     |        | IX1        | X1+X0           |

|                                    | HXO                                                                                                  | 01                                                                                        |        | NO         |                 |

|                                    | BX6                                                                                                  | 7X1^X0                                                                                    | 005217 |            |                 |

|                                    | LX6                                                                                                  | 01                                                                                        |        | SA2        | 804005007       |

| 005202                             |                                                                                                      | <u> </u>                                                                                  |        | AX2        | 01              |

| 000202                             | CAG                                                                                                  | B0+005010                                                                                 |        | IX6        | X1-X2           |

|                                    | SA6                                                                                                  |                                                                                           | 005000 | 140        | V1-V5           |

|                                    | SA1                                                                                                  | 004005001                                                                                 | 005220 | 0.4.6      | 00.005000       |

| 005203                             |                                                                                                      |                                                                                           |        | SA6        | 80+005002       |

|                                    | SA2                                                                                                  | 80+005002                                                                                 |        | SA1        | BO+005001       |

|                                    | 1x1                                                                                                  | <b>x2-x</b> 1                                                                             | 005221 |            |                 |

|                                    | MXO                                                                                                  | 01                                                                                        |        | BXO        | Xi              |

| 005204                             |                                                                                                      |                                                                                           |        | <b>AXO</b> | 04              |

| 00000                              | BX6                                                                                                  | TX1AX0                                                                                    |        | LXO        | 04              |

|                                    | LX6                                                                                                  | 01                                                                                        |        | IX6        | X1-X0           |

|                                    |                                                                                                      | _                                                                                         | 005222 | 170        | Y7-Y0           |

|                                    | SA6                                                                                                  | 80+005010                                                                                 | UU3ZZZ | ~          |                 |

| 005205                             |                                                                                                      |                                                                                           |        | SA6        | B0+005003       |

|                                    | SA1                                                                                                  | B0+005010                                                                                 |        | SA1        | B0+00500 1      |

|                                    | SAZ                                                                                                  | 80+005011                                                                                 | 005223 |            |                 |

| 005206                             |                                                                                                      |                                                                                           |        | SX6        | x14000144       |

|                                    | BX1                                                                                                  | 7X2^X1                                                                                    |        | SA6        | B0+005007       |

|                                    | MKO                                                                                                  | 73                                                                                        | 005224 |            |                 |

|                                    | BX6                                                                                                  | 73<br>7X1-X0                                                                              | 003224 | SA1        | B5+B0           |

|                                    |                                                                                                      | VI-V0                                                                                     |        |            |                 |

|                                    | NO                                                                                                   |                                                                                           |        | SB7        | X1+80           |

| 005207                             |                                                                                                      |                                                                                           |        | JP         | B7+000000       |

|                                    | SA6                                                                                                  | B0+005011                                                                                 | 005225 |            | 000000000000000 |

|                                    | SA1                                                                                                  | 80+005001                                                                                 | 005226 | 172162     | 220771740156064 |

| 005910                             |                                                                                                      |                                                                                           |        |            |                 |

| 005210                             |                                                                                                      |                                                                                           |        |            |                 |

| 003210                             | BXO                                                                                                  | Xl                                                                                        |        |            |                 |

| 005210                             | BX0                                                                                                  | X1<br><b>73</b>                                                                           |        |            |                 |

| 005210                             | LXO                                                                                                  | 73                                                                                        |        |            |                 |

| 005210                             | LX0<br>BX1                                                                                           | 73<br>X1-X0                                                                               |        |            |                 |

|                                    | LXO                                                                                                  | 73                                                                                        |        |            |                 |

| 005210                             | EXO<br>BX1<br>MXO                                                                                    | 73<br>X1-X0<br>01                                                                         |        |            |                 |

|                                    | EXO<br>BX1<br>MXO<br>BX6                                                                             | 73<br>X1-X0<br>01<br>X0AX1                                                                |        |            |                 |

|                                    | EXO<br>BX1<br>MXO                                                                                    | 73<br>x1-x0<br>01<br>x0^x1<br>01                                                          |        |            |                 |

|                                    | EXO<br>BX1<br>MXO<br>BX6                                                                             | 73<br>X1-X0<br>01<br>X0AX1                                                                |        |            |                 |

| 005211                             | EXO<br>BX1<br>MXO<br>BX6<br>LX6                                                                      | 73<br>x1-x0<br>01<br>x0^x1<br>01                                                          |        |            |                 |

|                                    | BX6<br>LX6<br>SA6                                                                                    | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011                                             |        |            |                 |

| 005211                             | BX6<br>LX6<br>SA6                                                                                    | 73<br>X1-X0<br>01<br>X0^X1<br>01<br>80+005011<br>B0+005001                                |        |            |                 |

| 005211                             | BX6<br>LX6<br>SA6<br>SA1<br>LX1                                                                      | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011                                             |        |            |                 |

| <b>005211</b> 005212               | BX6<br>LX6<br>SA6                                                                                    | 73<br>X1-X0<br>01<br>X0^X1<br>01<br>80+005011<br>B0+005001                                |        |            |                 |

| 005211                             | BX6<br>LX6<br>SA6<br>SA1<br>LX1                                                                      | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011<br>B0+005001<br>03                          |        |            |                 |

| <b>005211</b> 005212               | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO                                                                | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011<br>B0+005001<br>03                          |        |            |                 |

| <b>005211</b> 005212               | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO                                                                | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011<br>B0+005001<br>03                          |        |            |                 |

| <b>005211</b> 005212               | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO                                                                | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011<br>B0+005001<br>03                          |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO                                                                | 73<br>X1-X0<br>01<br>X0-X1<br>01<br>80+005011<br>B0+005001<br>03                          |        |            |                 |

| <b>005211</b> 005212               | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0                                           | 73<br>X1-X0<br>01<br>X0^X1<br>01<br>80+005011<br>B0+005001<br>03<br>80+005002<br>01<br>x2 |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | EX0<br>BX1<br>MXO<br>BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0                      | 73 X1-X0 01  X0^X1 01 80+005011  B0+005001 03  B0+005002 01 x2 02                         |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0                                           | 73 X1-X0 01 X0-X1 01 80+005011  B0+005001 03  B0+005002 01 x2 02 X2+X0                    |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | EX0<br>BX1<br>MXO<br>BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0<br>LX2<br>IX2<br>IX6 | 73 X1-X0 01  X0^X1 01 80+005011  B0+005001 03  B0+005002 01 x2 02                         |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0                                           | 73 X1-X0 01 X0-X1 01 80+005011  B0+005001 03  B0+005002 01 x2 02 X2+X0                    |        |            |                 |

| <b>005211</b> 005212 <b>005213</b> | EX0<br>BX1<br>MXO<br>BX6<br>LX6<br>SA6<br>SA1<br>LX1<br>NO<br>SA2<br>LX2<br>BX0<br>LX2<br>IX2<br>IX6 | 73 X1-X0 01 X0-X1 01 80+005011  B0+005001 03  B0+005002 01 x2 02 X2+X0                    |        |            |                 |