# TECHNIQUES FOR EFFICIENT FORMAL VERIFICATION USING BINARY DECISION DIAGRAMS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

By Alan John Hu December 1995

© Copyright 1995 by Alan John Hu All Rights Reserved I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

David L. Dill (Principal Advisor)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Robert K. Brayton

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Vaughan R. Pratt

Approved for the University Committee on Graduate Studies:

To my parents

For always standing behind me

But never pushing...

#### Abstract

The appeal of automatic formal verification is that it's automatic — minimal human labor and expertise should be needed to get useful results and counterexamples. BDD(binary decision diagram)-based approaches have promised to allow automatic verification of complex, real systems. For large classes of problems, however, (including many distributed protocols, multiprocessor systems, and network architectures) this promise has yet to be fulfilled. Indeed, the few successes have required extensive time and effort from sophisticated researchers in the field. Clearly, techniques are needed that are more sophisticated than the obvious direct implementation of theoretical results.

This thesis addresses that need, emphasizing an application domain that has been particularly difficult for BDD-based methods — high-level models of systems or distributed protocols — rather than gate-level descriptions of circuits. Additionally, the emphasis is on providing useful debugging information for the designer rather than on certifying correctness. Accordingly, I only consider a simple verification paradigm (that all reachable states of a system satisfy a propositional logic formula) and seek to make it applicable to complex, real systems, rather than devising theoretically more complicated verification paradigms.

I identify several common obstacles to BDD-based automatic formal verification and propose techniques to overcome them. Specifically, (1) I consider the difficulty of specifying realistic high-level designs using BDDs and give a set of high-level language constructs and the accompanying algorithms for automatic translation that are expressive enough to specify real designs, yet are still efficiently handled by BDDs; (2) I describe how to compute images (pre- and post-conditions) of sets of states efficiently

through the high-level description of the system being verified without ever building the BDD for the transition relation of the system, thereby avoiding a major BDD-size blowup; and (3) I highlight why BDD-size blowup is so common when performing high-level verification and propose techniques based on functional dependencies and on implicitly conjoined lists of BDDs to avoid some of these blowups. I have implemented these techniques in the Ever verification system and applied them to several examples, illustrating the effectiveness of the new techniques in expanding the range of problems that can routinely be verified automatically.

### Acknowledgments

Dissertation tradition apparently dictates that I rattle off a lengthy list of my nearest and dearest friends, sprinkle in an inside joke or two, and disclaim that just because I forgot to list someone doesn't mean that I'm not eternally grateful to him or her. I choose to break with this tradition not out of lack of gratitude, but rather from an overabundance of it. Any delineation of people to thank excludes, unavoidably and arbitrarily, other people who also deserve my thanks. On what basis do I thank person A who accrued x UGUs (universal gratitude units), yet exclude person B who has only accrued  $x - \epsilon$ ? And doesn't person C, who has accrued 10x UGUs, deserve special mention? Worse, the UGU doesn't even exist, for the intellectual and personal debts I have incurred are multidimensional, incomparable quantities. How can I rank a net.friend whose quick wit and insightful intellect brightened many a day versus a dance partner whose grace, poise, and beauty (not to mention quick wit and insightful intellect) brightened many an evening? How do I valuate my intellectual indebtedness to the teachers and mentors who taught me theoretical computer science versus those who taught me about electronic design automation? How do I compare my eternal gratitude to the friend who has countless times kept my computer running versus the friend who held my head in her lap while I wept with self-doubt? In short, how can I list a set of names without committing a disservice to those I list as well as to those I do not? Allow me instead to paint with broad strokes.

That being said, I do need to single out my advisor for conning me into a wonderfully interesting research area and then putting up with me for the better part of a decade with patience, humor, good advice (research and otherwise), friendship, and money.

A consequence of the research area is the excellent set of researchers I have met, at Stanford, across the Bay, across the country, and around the world. They have unfailingly provided intellectual stimulation and comraderie.

I consider myself very fortunate to have spent a decade at Stanford. The faculty and my fellow students are truly outstanding and inspirational. Even with all the downsides of student life, if I had the option to spend my career working with these people, I would leap at the chance.

And despite my generally rude and antisocial personality, I've somehow been blessed with a wonderful set of friends and family members. (Another reason not to list names is to deny this information to long-distance carrier telemarketers.) From across the vast asynchrony in time and space of soc.culture.asian.american to the intimate closeness of a tango, whether (very) patiently explaining to me the intricacies (basics?) of  $\omega$ -automata or of T'ai Chi Ch'uan, from going up and down mountains to hitting things over nets, whether sharing a concert, a meal, or an impromptu chat in the hallway, they have made my life so much fuller, so much richer, so much happier.

To all of you who have touched my life in your myriad ways, thank you. May your friends be as kind to you as you have been to me.

# Contents

| 1 | Intr | roduction                                          | 1  |

|---|------|----------------------------------------------------|----|

|   | 1.1  | Motivation and Philosophy                          | 1  |

|   | 1.2  | Background                                         | 3  |

|   |      | 1.2.1 Proof-Based Methods                          | 3  |

|   |      | 1.2.2 State-Exploration Methods and Model Checking | 6  |

|   |      | 1.2.3 Binary Decision Diagrams                     | 9  |

|   |      | 1.2.4 Symbolic Model Checking                      | 13 |

|   | 1.3  | What This Thesis Is About                          | 17 |

| 2 | Tra  | nslation into BDDs                                 | 21 |

|   | 2.1  | High-Level Language Constructs                     | 21 |

|   | 2.2  | Translation                                        | 24 |

|   |      | 2.2.1 Constants and Variables                      | 25 |

|   |      | 2.2.2 Arithmetic and Logical Expressions           | 28 |

|   |      | 2.2.3 Assignment                                   | 30 |

|   |      | 2.2.4 Control Flow                                 | 32 |

| 3 | Effi | cient Image Computation                            | 35 |

|   | 3.1  | Background                                         | 35 |

|   | 3.2  | Image Computation Procedure                        | 38 |

| 4 | BD   | D Blow-Up Representing Sets of States              | 41 |

|   | 4.1  | A Historical Note                                  | 42 |

|   | 4.2  | BDD Size Intuition                                 | 43 |

|   | 4.3 | High-Level Verification Is Hard for BDDs | 47  |

|---|-----|------------------------------------------|-----|

| 5 | Fun | ctionally Dependent Variables            | 51  |

|   | 5.1 | Introduction                             | 51  |

|   | 5.2 | Theoretical Basis                        | 53  |

|   | 5.3 | Implementation                           | 57  |

|   | 5.4 | A Benchmark Example                      | 61  |

| 6 | Imp | olicitly Conjoined BDDs                  | 73  |

|   | 6.1 | Introduction                             | 73  |

|   | 6.2 | Theoretical Basis                        | 75  |

|   | 6.3 | Heuristics                               | 78  |

|   |     | 6.3.1 A Simple Approach                  | 78  |

|   |     | 6.3.2 Greedy Evaluation                  | 79  |

|   |     | 6.3.3 Exact Termination Testing          | 81  |

|   | 6.4 | Experimental Results                     | 87  |

|   |     | 6.4.1 A Typed FIFO Buffer                | 87  |

|   |     | 6.4.2 A Simple Network                   | 89  |

|   |     | 6.4.3 A Moving-Average Filter            | 91  |

|   |     | 6.4.4 A Simple Pipelined Processor       | 95  |

|   | 6.5 | Comments                                 | 98  |

| 7 | Cor | ntributions and Future Work              | 101 |

|   | 7.1 | Contributions                            | 101 |

|   | 7.2 | Future Work                              | 102 |

| A | Eve | r Verifier Reference Manual              | 107 |

|   | A.1 | Introduction                             | 107 |

|   | A.2 | A Tutorial Example                       | 109 |

|   | A.3 | Ever Language Details                    | 116 |

|   |     | A.3.1 Lexical Units                      | 116 |

|   |     | A.3.2 Type System                        | 118 |

|   |     | A 3.3 Variable Versions                  | 120 |

| Bibliography |              | 135   |

|--------------|--------------|-------|

| A.3.6        | Commands     | . 131 |

| A.3.5        | Declarations | . 128 |

| A.3.4        | Expressions  | . 121 |

# List of Tables

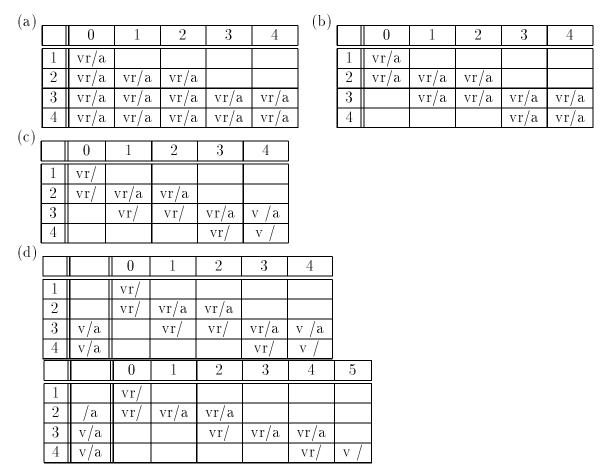

| 5.1 | Functionally Dependent Variables Results                      | 71 |

|-----|---------------------------------------------------------------|----|

| 6.1 | Implicitly Conjoined BDDs Results: Typed FIFO Buffer          | 90 |

| 6.2 | Implicitly Conjoined BDDs Results: Messages in Network        | 92 |

| 6.3 | Implicitly Conjoined BDDs Results: Moving-Average Filter      | 96 |

| 6.4 | Implicitly Conjoined BDDs Results: Simple Pipelined Processor | 99 |

# List of Figures

| 1.1 | CTL Model Checking Example                                         | 8   |

|-----|--------------------------------------------------------------------|-----|

| 1.2 | A Binary Decision Diagram (BDD)                                    | 10  |

| 1.3 | BDD Variable Order Matters                                         | 12  |

| 1.4 | Symbolic Model Checking Example                                    | 14  |

| 4.1 | Fooling Set Intuition                                              | 45  |

| 4.2 | Effect of Separating Related Variables                             | 46  |

| 4.3 | Variable Relationships in a Typical System-Level Model             | 48  |

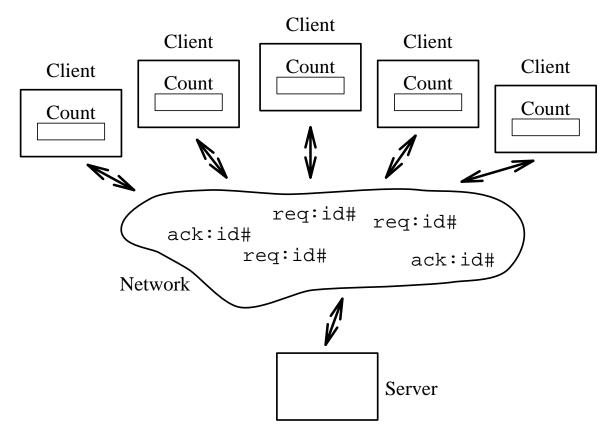

| 5.1 | Network Example                                                    | 62  |

| 5.2 | Proof of Theorem 5.3: BDD Nodes in a Square                        | 65  |

| 5.3 | Proof of Theorem 5.3: BDD Nodes on a Chessboard                    | 67  |

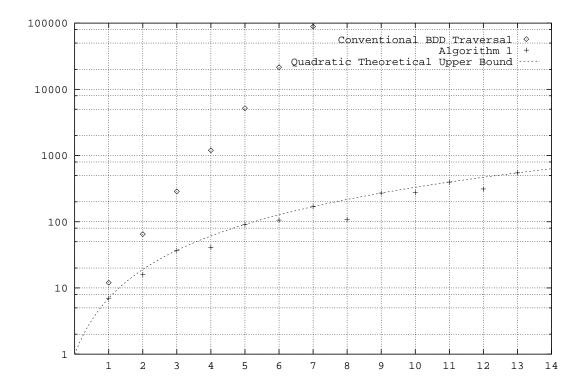

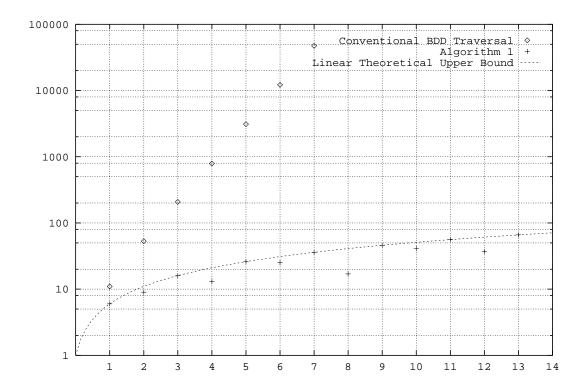

| 5.4 | Functionally Dependent Variables Results: Largest Intermediate BDD | 69  |

| 5.5 | Functionally Dependent Variables Results: Reachable State BDD      | 70  |

| 6.1 | Backward Traversal with Implicitly Conjoined BDDs                  | 76  |

| 6.2 | Greedy Algorithm to Select Conjunctions in a List to Evaluate      | 82  |

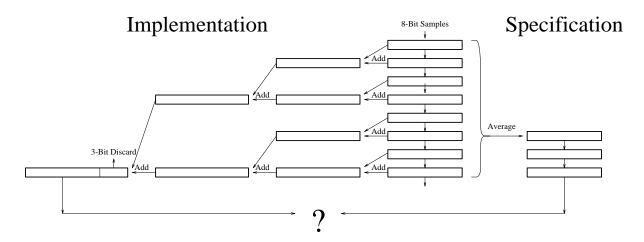

| 6.3 | Moving-Average Filter Example                                      | 95  |

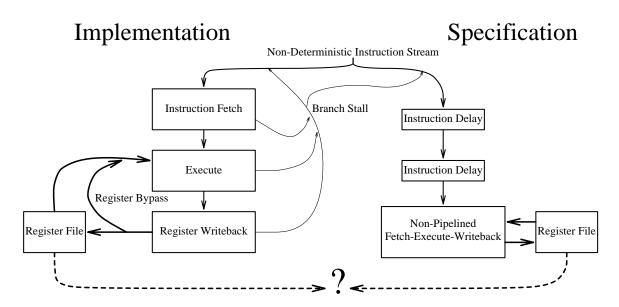

| 6.4 | Pipelined Processor Example                                        | 98  |

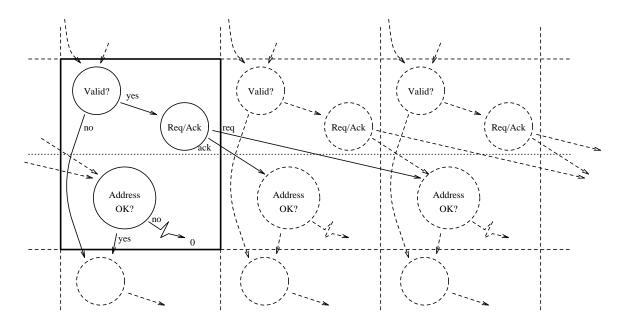

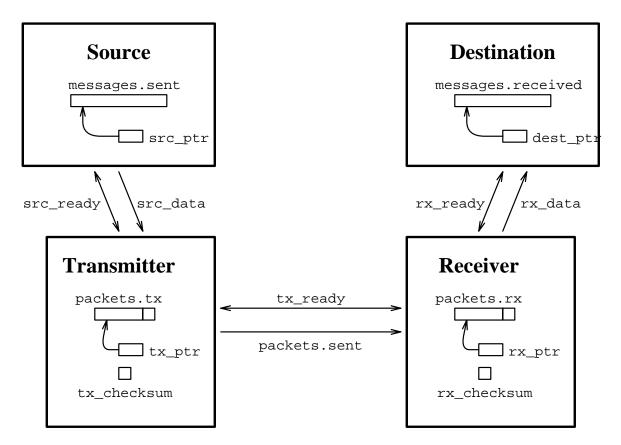

| A.1 | Link-Level Protocol Example                                        | 110 |

# Chapter 1

#### Introduction

#### Chapter Overview

This chapter motivates my emphasis on automatic verification as a practical debugging tool, situates my approach as a state-exploration or model-checking approach rather than a theorem-proving one, and provides basic background on CTL model-checking, binary decision diagrams (BDDs), and how to use BDDs for my verification problem.

#### 1.1 Motivation and Philosophy

Bugs cost money. Whenever an error creeps into a design, time and money must be spent to locate the problem and correct it, and the longer a bug evades detection, the harder and more expensive it is to fix. Indeed, the cost of making an engineering change rises by an order of magnitude at each successive stage of the design cycle [78]. Beyond the high cost of fixing bugs is the even higher cost of being late to market — a McKinsey and Company study indicates that being only six months late on a product with a five year life cycle results in one-third less total profit [25]. Should a bug slip through into the completed product, the results can be disastrous. For example, the Pentium FDIV public relations fiasco cost Intel Corporation a half billion dollars [40]. Detecting and eliminating bugs as early in the design cycle as possible is clearly an

economic imperative.

Working against this imperative, however, is the engineering reality that systems are becoming ever larger and more complicated. A person can no longer gain a reasonable assurance of correctness by simply staring at and thinking about a paper design. Worse, as design complexity increases, simulation times become prohibitive and coverage becomes poor, allowing numerous bugs to slip through to later stages of the design cycle. What is needed, therefore, is an aid to developing conceptually correct designs to start with and a supplement to simulation and testing in debugging the implementation of the conceptual design.

My interest in formal verification is to meet this need. Note that my motivation is explicitly economic. I have made no appeals to safety-critical systems, saving lives, or the moral superiority of proving systems correct. I do not discount the importance of such work. Indeed, I believe that safety-critical systems demand the most rigorous assurances of correctness available, especially when my own safety is at stake. But I also believe that for an enormous range of practical, real problems, pure financial profit is a compelling motivation to use formal verification as a debugging tool to speed a product to market, and my research focuses on this domain. Condensed to a slogan, my research aims to save money, not lives.<sup>1</sup>

Adopting a purely economic justification for formal verification has consequences. Fundamentally, the time and labor invested in verification must repay itself by helping the designer find and correct bugs quickly. Therefore, the emphasis must be on methods that are easy-to-use and highly automatic to minimize the time and labor invested and that provide counterexamples to help the designer find and correct the bugs. Furthermore, verification should be applied as early in the design cycle as possible, when bugs are cheaper and easier to fix. The goal is rapid, light-weight debugging support, rather than slow, laborious certification of correctness.

<sup>&</sup>lt;sup>1</sup>For readers interested in safety-critical systems, Leveson [60] provides a comprehensive introduction.

#### 1.2 Background

The goals of designing correct systems and finding and correcting bugs have been around for as long as people were designing systems. The idea of using formal methods to help these goals have been around almost as long.

#### 1.2.1 Proof-Based Methods<sup>2</sup>

"In the beginning, there was Floyd." Floyd introduced the first rigorous treatment of correctness of sequential programs [31]. The basic idea is to annotate each point in a program with an assertion. The program computes the correct result if (1) it terminates, (2) the state of the system before the program executes satisfies the assertion at the start of the program, (3) for each statement in the program, we can prove that the truth of the assertion before the statement implies the truth of the assertion following the statement, and (4) the assertion at the end of the program implies the result is correct. Of particular relevance to my work is Floyd's notion of a strongest verifiable consequent: Given an assertion that holds before a statement, the strongest verifiable consequent is the strongest assertion that must hold after executing that statement. Furthermore, Floyd gives rules to compute the strongest verifiable consequent automatically for several programming-language constructs and notes that these rules allow fully automatic verification in the absence of loops. We will see these ideas again later in this thesis.

An extensive array of formal treatments of program correctness have sprung from this start. Hoare reworked Floyd's ideas into a logical framework, introducing the notation  $P\{Q\}R$  to denote the statement: If assertion P (the precondition) holds

<sup>&</sup>lt;sup>2</sup>The terminology is somewhat problematic, since all formal methods are "proof-based" in that, by definition, they produce some sort of mathematical proof. I am stealing this terminology from Long, who contrasts "proof-based methods" — which emphasize the construction of a proof of correctness via axioms and inference rules for the specification language used — to "state-exploration methods" — which search the state space of an implementation to check that it satisfies its specification [62]. Emerson draws a similar distinction, labeling them "proof-theoretic" and "model-theoretic" [28].

<sup>&</sup>lt;sup>3</sup>Quotation is from Lamport [58], referring to Floyd's seminal work [31].

before program Q executes, then assertion R (the postcondition) holds after Q completes [39]. An idea relevant to my thesis is that Hoare defined his axiom for assignment backwards from Floyd's — whereas Floyd starts from the precondition and computes the strongest verifiable consequent, Hoare starts from the postcondition and gives a means to compute the precondition. Dijkstra expanded in this direction, introducing the notion of the weakest precondition wp(S,R), which is the weakest assertion about the state prior to the execution of program (or program fragment) S that guarantees that assertion R will hold afterwards [26]. Furthermore, Dijkstra provided rules to compute the weakest precondition of a program constructed from assignment statements and guarded command sets (which provide if-then-else, non-deterministic choice, and looping) by recursively propagating weakest preconditions backward through the structure of the program. (In the absence of loops, this approach also gives fully automatic verification.) Pratt's introduction of dynamic logic [79] unified earlier work in a clean conceptual framework that has served as the foundation for considerable further research, which lies beyond the scope of this thesis. Kozen and Tiuryn [56] and Cousot [24] provide recent surveys of this area.

The above methods were all designed to deal with programs that compute a result and then terminate, sometimes called transformative programs. In contrast, many important applications, generally referred to as reactive systems, are considered not to terminate: for example, operating systems, controllers, communication protocols, and hardware systems. Instead, correct behavior means the system is maintaining a continuing dialog with its environment. Thus, a different logical formalism is better suited to these applications.

Temporal logic has emerged as a main formalism for reactive systems. A temporal logic is essentially an ordinary predicate or propositional logic with the addition of modal operators for describing how the interpretation of symbols changes over time. Typical temporal operators include the next-time operator (generally written  $\bigcirc$  or X), the eventuality operator (generally written  $\bigcirc$  or F), and the henceforth or always operator (generally written  $\square$  or G). For example, the sentence p asserts that p holds in the current state, the sentence Xp is true in the current state if p holds in the next state, and the sentence  $\square \diamondsuit p$  (always eventually p) is true if at all points in

the future, it is always true that eventually p will hold (in other words, p will hold infinitely often). Pnueli introduced the use of temporal logic for the formal verification of reactive systems [76], and Manna and Pnueli codified a general means to create a temporal logic proof system for any programming language [64]. As with program logics, the field of temporal logic has spawned considerable research, most of which lies beyond the scope of this thesis. Pnueli [77] surveys this area espousing a proofbased methodology; Emerson [28] provides a more recent survey and also covers the model-checking approach to temporal logic (discussed below).

Regardless of logical formalism, constructing proofs can be tedious and difficult, so some have turned to automatic theorem provers, achieving limited success. The field of automatic deduction and theorem proving is enormous, spanning both logic and AI, and extending far beyond the field of formal verification, not to mention this thesis. Wos et al. [87] provide a starting point to survey this area. Recent high-profile successes in the use of automatic theorem provers for formal verification include Cohn's verification of the Viper microprocessor [20] using the HOL theorem proving system [37, 36], Hunt's verification of the FM8502 microprocessor [46] using the Boyer-Moore theorem prover nqthm [4] (both of these microprocessors are very simple and were specifically designed for formal verification), and, very recently, Srivas and Miller's verification of a half-million transistor commercial microprocessor, the AAMP5 [84], using the PVS theorem prover [71, 72].

Despite the periodic success stories, proof-based methods remain notoriously time-consuming [60, p. 496], and "most of the 'automated' theorem-provers available today are semi-automated at best." [38, p. 220] Much progress has been made in automating proofs of correctness, but these methods have yet to have widespread industrial impact. The user must cleverly guide the proof process, and the generation of appropriate invariants for loops and inductions is particularly difficult. Furthermore, if the user is unable to prove correctness, no indication differentiates inadequate cleverness on the part of the user from the existence of a real bug in the design. Indeed, even proponents of automatic theorem provers have taken a keen interest in integrating state-exploration methods into their provers [52, 80], touting the increased automation and efficiency of state-exploration methods over proof-based methods. Over a

quarter century ago, Hoare wrote:

The practice of supplying proofs for nontrivial programs will not become widespread until considerably more powerful proof techniques become available, and even then will not be easy.... At present, the method which a programmer uses to convince himself of the correctness of his program is to try it out in particular cases and to modify it if the results produced do not correspond to his intentions. After he has found a reasonably wide variety of example cases on which the program seems to work, he believes that it will always work. [39, p. 579]

A quarter century later, the situation has only started to change.

#### 1.2.2 State-Exploration Methods and Model Checking

Of course, the world of simulation and testing hasn't been stationary. Real people have been designing ever larger and more complex real systems and have therefore developed more sophisticated means to simulate and test them. (For just two examples, Holzmann [41] overviews a wide variety of validation techniques for protocols, and Cheng and Agrawal [14] survey simulation and test generation techniques for VLSI.) In particular, if we can somehow exhaustively simulate every possible execution of a system, then we have actually proven (by exhaustive case analysis) the system correct. This idea provides a natural lead-in to the concept of model checking.

Model checking was invented by Clarke and Emerson [18] and represents an approach to verification fundamentally different from the proof-based methods described above. With proof-based methods, the user describes the system being verified using assertions in some logical formalism and attempts to deduce a proof, using inference rules for the logic being used, that the assertions imply the correctness property being checked. In contrast, model checking treats the entire reachability graph of the system being verified as a Kripke structure, and verification consists of checking whether or not the structure is a model of the correctness property being checked. For many logics, if the state space is finite, checking whether the (finite) Kripke structure is a

model of a formula is very efficient, using graph algorithms to traverse the Kripke structure.

Before presenting an example of model checking, let me introduce the logical notation used throughout this thesis as well as the temporal logic CTL used in the following example. Throughout the thesis, I will mix Boolean algebra notation and propositional logic notation in an effort to maximize clarity and brevity. Accordingly, the unary operator  $\neg$  denotes logical negation, the binary operators  $\cdot$  and  $\wedge$  as well as juxtaposition denote conjunction, the binary operator  $\oplus$  denotes exclusive-OR, the binary operators + and  $\vee$  denote disjunction, and the binary operator  $\Rightarrow$  denotes logical implication. Operator precedence is in the order listed, with ¬ being highest. CTL (Computation Tree Logic) is a propositional, branching-time temporal logic frequently associated with model checking [18, 17]. In addition to atomic propositions and Boolean operators, CTL contains the usual forward time temporal operators: X (next time), F (eventually), G (always), and U (until). However, each use of any temporal operator must always be paired with a path quantifier: A (for all paths), or E (there exists a path). For example, the formula AGp is true in a state if for all paths starting from that state, p is always true; the formula EFp is true in a state if there exists a path starting in that state that eventually leads to a state where p is true; and the formula AFGp is not a valid CTL formula because the G is not controlled by a path quantifier, and in fact, this formula cannot be expressed in CTL.<sup>4</sup>

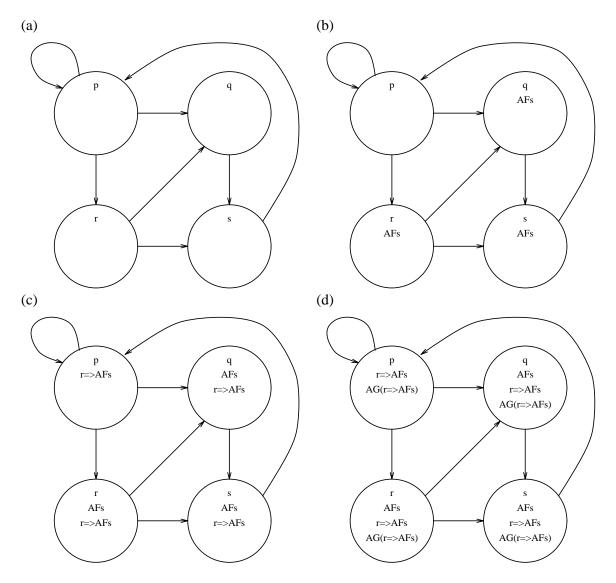

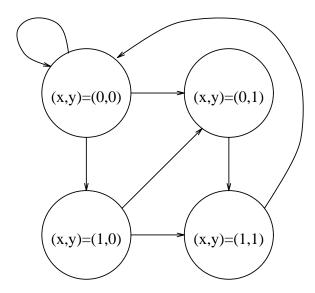

Let's consider the simple example in Figure 1.1(a). In this example, the Kripke structure has four states and ostensibly describes the transition structure of some system we wish to verify. Suppose we wish to check the CTL formula  $AG(r \Rightarrow AFs)$  that says that throughout the system, whenever r is true, s must inevitably be true now or in the future. Model checking proceeds by repeatedly traversing the graph, labeling all states that satisfy each subformula. Note that in CTL, the truth or falsehood of a subformula at a state does not depend on the formula in which it is embedded, so we can make a single pass through the CTL formula starting from

<sup>&</sup>lt;sup>4</sup>This result follows from Emerson and Halpern [29, Theorem 4.4], since AFGp is equivalent to  $\neg \text{EGF} \neg p$ , which is equivalent to  $\neg \text{E} \overset{\infty}{\text{F}} \neg p$  ("There does not exist a path where  $\neg p$  holds infinitely often."), which is shown not to be expressible in CTL.

Figure 1.1: CTL Model Checking Example: Model checking proceeds by repeatedly traversing the graph for each subformula, labeling those states that satisfy the subformula. Here, we are checking the formula  $AG(r \Rightarrow AFs)$ . Part (a) shows the original Kripke structure labeled with atomic propositions, part (b) labels those states that satisfy AFs, part (c) labels those states that satisfy  $r \Rightarrow AFs$ , and part (d) labels those states that satisfy the entire formula. As we can see, all states satisfy the formula.

the smallest subformulas, giving time complexity linear in the size of the formula. Accordingly, we label those states that satisfy AFs (Figure 1.1(b)) by using a depth-first search of the graph: if a state is labeled s, then label it AFs, mark it as visited, and return; if a state is on our depth-first search stack, then there exists a cycle where s is never true, so don't label it AFs, do mark it as visited, and return; otherwise, AFs holds iff it holds at all of the successors of the state. Next, we can traverse the graph again, labeling all states that satisfy  $r \Rightarrow AFs$  (Figure 1.1(c)). Finally, we perform another depth-first search, similar to the one for AF, to label all states that satisfy AG( $r \Rightarrow AFs$ ) (Figure 1.1(d)). Details about CTL model checking as well as model checking research for other logics can be found in Emerson's recent survey [28, Sec. 6.4 and 7.4].

In general, the complexity of model checking is a function of the size of the Kripke structure. CTL model checking, for example, requires time proportional to the product of the size of the structure and the length of the formula being checked. Since the size of the model is typically exponential in the number of variables in the system being verified (the "state explosion problem"), unless we find efficient means to represent the structure and sets of states, we can use model checking only on fairly small problems. Symbolic model checking with binary decision diagrams promises to be such an efficient means and has generated considerable excitement recently. Before we proceed, therefore, we need to know what a binary decision diagram is; then, we can examine how to use binary decision diagrams for symbolic model checking.

#### 1.2.3 Binary Decision Diagrams

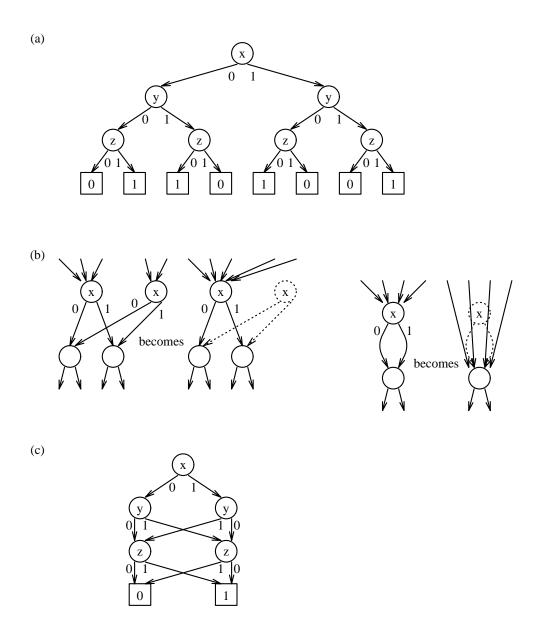

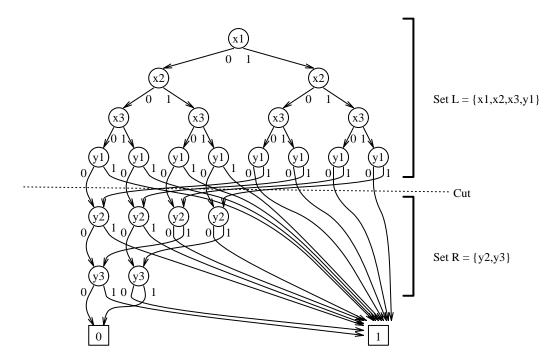

The binary decision diagram (BDD) is a data structure for representing Boolean functions. Bryant [6] introduced the BDD in its current popular incarnation, although the general ideas have been floating around for quite some time (e.g., as branching programs in the theoretical computer science literature). Conceptually, we can construct the BDD for a Boolean function as follows. First, build a decision tree for the desired function, obeying the restrictions that along any path from root to leaf, no variable may appear more than once, and that along every path from root to leaf, the variables always appear in the same order (Figure 1.2(a)). Next, repeatedly apply

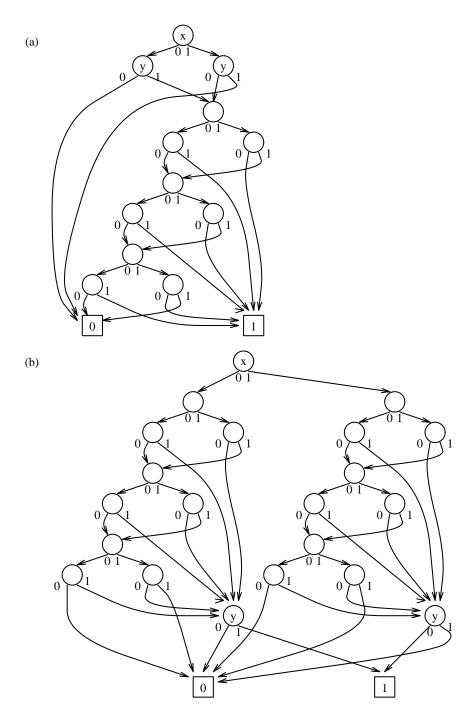

Figure 1.2: A Binary Decision Diagram (BDD): This example shows the BDD for the exclusive OR of x, y, and z. Conceptually, we can construct the BDD for the function by starting from a decision tree, shown in part (a). The decision tree is restricted so that (1) along any path from root to leaf, no variable appears more than once, and (2) along every path from root to leaf, the variables always appear in the same order. Next, we merge identical nodes and delete redundant nodes, as shown in part (b). The result is the BDD for the function, shown in part (c). In practice, BDDs are always maintained in the fully reduced form.

the following two reduction rules as much as possible: (1) Merge any duplicate (same label and same children) nodes, and (2) if both child pointers of a node point to the same child, delete the node because it is redundant (with the parents of the node now pointing directly to the child of the node) (Figure 1.2(b)). The resulting DAG is the BDD for the function (Figure 1.2(c)). In practice, BDDs are generated and manipulated in the fully reduced form, without ever building the decision tree.

BDDs have several useful properties. First, although a simple counting argument shows that "most" Boolean functions require large BDD representations, many common function have small BDDs. For example, generalizing the pattern in Figure 1.2(c), we can see that the BDD for the parity of n variables requires 2n-1 nodes, whereas parity requires an exponential-size representation using disjunctive normal form. In addition, BDDs are easy to manipulate. We can compute any binary Boolean operation on two functions represented as BDDs in time proportional to the product of the sizes of the BDDs. We can evaluate a function in time linear in the number of variables. We can existentially or universally quantify (Boolean) variables in a function in time quadratic in the size of the BDD. Finally, once we fix the order in which the variables appear, the BDD is a canonical representation for the Boolean function. Thus, function comparison, including special cases tautology and satisfiability, become trivially easy (constant time for efficient implementations [5]).

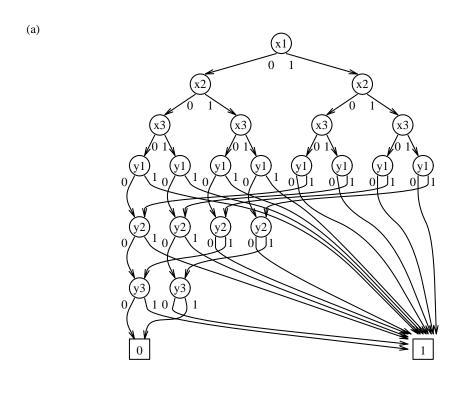

Choosing a good variable order is important. For example, suppose we wish to build a BDD for the function  $(x_1 \oplus y_1) + (x_2 \oplus y_2) + (x_3 \oplus y_3)$ . If we order the variables  $x_1, x_2, x_3, y_1, y_2, y_3$ , we get the large BDD shown in Figure 1.3(a). If instead we order the variables  $x_1, y_1, x_2, y_2, x_3, y_3$ , we get the smaller BDD shown in Figure 1.3(b).

<sup>&</sup>lt;sup>5</sup>In general usage, "BDD" refers to the data structure described here, possibly with some modifications for efficiency [5] that don't concern us at the moment. This data structure has achieved widespread acceptance in VLSI, formal verification, and other fields. Subsequently, several researchers have generated a menagerie of BDD variants that relax, modify, or extend the rules governing the construction of BDDs, e.g., if-then-else DAG [54], MDD [83, 53], XBDD [50], snDD [49], EVBDD [57], FDD [55], SQBDD [70, 69], OPDD [74], ADD [1], etc., to name only a few. Accordingly, when there is risk of confusion in the literature, the BDD described here is dubbed an ROBDD, for reduced (because the reduction rules were applied) ordered (because the variables are always in the same order from root to leaf) BDD. Since this thesis only concerns itself with the standard BDD, I will use the simpler and common term "BDD" rather than "ROBDD".

<sup>&</sup>lt;sup>6</sup>There are  $2^{2^n}$  Boolean functions of n variables. A representation scheme with size bounded by some polynomial P(n) can represent at most  $O(2^{P(n)})$  functions.

Figure 1.3: BDD Variable Order Matters: Here we consider the BDD for  $(x_1 \oplus y_1) + (x_2 \oplus y_2) + (x_3 \oplus y_3)$  using two different variable orders. In general, the choice of variable order can make a difference between linear and exponential size.

In general, the choice of variable order can make the difference between a linear size BDD and an exponential one. The problem of finding the best variable order for a given function is co-NP-complete [6]. Friedman and Supowit give an  $O(n^23^n)$  algorithm for finding the optimum order [32]. Several heuristics for variable ordering exist for various applications such as combinational circuits [34, 63, 33] and sequential circuits [51]. The variable order can even be changed efficiently after the BDD has already been built [81].

In sum, BDDs are a practically efficient representation of Boolean functions. This is sufficient for us to examine how to use BDDs for model checking. Bryant [8] provides a detailed exposition on BDDs and surveys some applications and variations.

#### 1.2.4 Symbolic Model Checking

The basic idea behind symbolic model checking is to use a more efficient "symbolic" representation for the Kripke structure being checked and for sets of states of the Kripke structure. Since the sizes of these representations is typically the limiting factor in applying model checking, an efficient representation can potentially allow much larger structures to be checked. The idea of using BDDs as this representation came upon several researchers roughly simultaneously [22, 21, 3, 10, 75, 85]. Among these early works, Burch et al.'s [10] is the most comprehensive treatment of symbolic model checking with BDDs and can be consulted for details. Here, I will briefly sketch symbolic model checking for CTL.

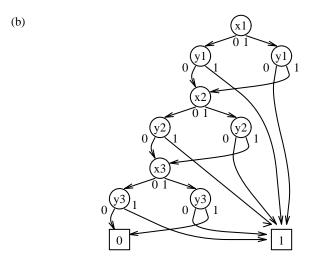

The first step is to label each state of the Kripke structure with a unique binary vector of length n, choosing n so that  $2^n$  is at least the number of states in the structure. Associate each position in the binary vectors with a Boolean variable. For example, Figure 1.4 shows the same structure from the model checking example we saw previously (Figure 1.1), but now each state has a unique two bit label. We will associate the first bit with the Boolean variable x and the second bit with the Boolean variable y. In practice, we omit this step and simply use the state variables of the system we are verifying as the unique binary vector identifying each state. (For hardware, use the logic levels of the nets or latches; for software, use the program state.)

| p                       | $\neg x \neg y$ |

|-------------------------|-----------------|

| q                       | $\neg xy$       |

| $\mid r$                | $x \neg y$      |

| s                       | xy              |

| AFs                     | x + y           |

| $r \Rightarrow AFs$     | 1               |

| $AG(r \Rightarrow AFs)$ | 1               |

Figure 1.4: Symbolic Model Checking Example: This is the same structure as in Figure 1.1. Each state now has a unique two bit label (x, y), so we can describe any set of states by a Boolean expression as shown. Symbolic model checking works by computing directly with the Boolean expressions (represented as BDDs), rather than with an explicit representation of the Kripke structure.

With this labeling, any expression on the Boolean variables represents a set of states of the structure. For example, the expression  $\neg x \neg y$  represents the single state in the upper left of the structure, the expression x+y represents the set of all states except the upper left corner, and the expression 1 represents the set of all states. To perform model checking, instead of labeling states with subformulas as we did before, we associate each subformula with a BDD that represents the Boolean expression for the set of states at which the subformula holds. Thus, for example, we associate the atomic proposition s with the BDD for the Boolean expression xy.

We also need to represent the Kripke structure itself symbolically. The easiest way is to build the transition relation  $\delta(q, q')$  that is true iff there is a transition from state q to state q'. Note that in the preceding paragraph, we represent a set of states by a Boolean function on a single state that indicates whether or not the state is in the set. In contrast, here we need to represent a transition relation, which is a Boolean function on a **pair** of states that indicates whether or not the specified transition exists. To use BDDs to represent transition relations, therefore, we must introduce

1.2. BACKGROUND

15

for each BDD variable x, another BDD variable x' that denotes the value of x in the next state. Returning to the example in Figure 1.4, we see that (0,0) can transition to itself or state (0,1) or state (1,0), yielding  $\neg x \neg y \Rightarrow \neg x' + \neg y'$ . Similarly, state (0,1) must transition to state (1,1), yielding  $\neg xy \Rightarrow x'y'$ ; state (1,0) can transition to either states (0,1) or (1,1), yielding  $x \neg y \Rightarrow y'$ ; and state (1,1) must transition to state (0,0), yielding  $xy \Rightarrow \neg x' \neg y'$ . Putting this all together gives us the transition relation

$$(\neg x \neg y \Rightarrow \neg x' + \neg y') \cdot (\neg xy \Rightarrow x'y') \cdot (x \neg y \Rightarrow y') \cdot (xy \Rightarrow \neg x' \neg y'),$$

which simplifies to  $\neg x \neg y \neg x' + \neg x \neg y \neg y' + \neg xyx'y' + xy \neg x' \neg y' + x \neg yy'$ .

The key to symbolic model checking is to perform all calculations directly using these Boolean expressions, rather than using the Kripke structure explicitly. For example, if we want to complement or intersect sets of states, we can just negate or AND the corresponding BDDs. More interesting are the modal operators. For example, given BDDs for the transition relation  $\delta$  and the set of states that satisfy some formula p, we can compute the BDD for the set of states that satisfy AXp as  $\lambda q \forall q' [\delta(q, q') \Rightarrow p(q')]$ . Using AX, we can express AFp as the least fixed point of a predicate transformer:

$$AFp = IfpZ.p \vee AXZ$$

which can be computed iteratively by starting Z at False. Similarly, AGp is the greatest fixed point of a predicate transformer:

$$AGp = gfpZ.p \wedge AXZ,$$

which can be computed iteratively by starting Z at True. Convergence of both

<sup>&</sup>lt;sup>7</sup>Please forgive the abuse of notation. Recall that  $\delta$  and p are BDDs and are therefore propositional. The pseudo-first-order notation here simply indicates whether the BDD contains the primed or unprimed variables. Accordingly, the precise sequence of BDD operations to implement this expression is (1) change the BDD for p from unprimed to primed variables, (2) from the BDDs for  $\delta$  and (primed) p, compute the BDD for the implication, and (3) universally quantify the primed variables from the resulting BDD. Changing the variables in a BDD between primed and unprimed is straightforward as long as the variable order keeps each primed-unprimed variable pair together.

iterations is guaranteed because the transformation is monotonic on a finite lattice.

Returning again to Figure 1.4, we can now work the example using symbolic model checking. The atomic proposition s has associated Boolean formula xy. To compute the Boolean formula for the CTL subformula AFs, we use the fixed point formula given above:

$$Z_{0} = 0$$

$$Z_{1} = xy + AXZ_{0}$$

$$= xy + \forall x'y'[(\neg x \neg y \neg x' + \neg x \neg y \neg y' + \neg xyx'y' + xy \neg x' \neg y' + x \neg yy') \Rightarrow 0]$$

$$= xy +$$

$$(\neg x \neg y + xy \Rightarrow 0) \cdot$$

$$(\neg xy + x \neg y \Rightarrow 0) \cdot$$

$$(\neg xy + x \neg y \Rightarrow 0)$$

$$= xy + (x + y)(\neg x + \neg y)(\neg x + y)(x + \neg y)$$

$$= xy$$

$$Z_{2} = xy + AXZ_{1}$$

$$= xy + \forall x'y'[(\neg x \neg y \neg x' + \neg x \neg y \neg y' + \neg xyx'y' + xy \neg x' \neg y' + x \neg yy') \Rightarrow x'y']$$

$$= xy +$$

$$(\neg x \neg y + xy \Rightarrow 0) \cdot$$

$$(\neg x \neg y + xy \Rightarrow 0) \cdot$$

$$(\neg xy + x \neg y \Rightarrow 0) \cdot$$

$$(\neg xy + x \neg y \Rightarrow 0) \cdot$$

$$(\neg xy + x \neg y \Rightarrow 1)$$

$$= xy + (x + y)(\neg x + \neg y)(\neg x + y)$$

$$= y$$

$$Z_{3} = xy + AXZ_{2}$$

$$= xy + \forall x'y'[(\neg x \neg y \neg x' + \neg x \neg y \neg y' + \neg xyx'y' + xy \neg x' \neg y' + x \neg yy') \Rightarrow y']$$

$$= xy +$$

$$(\neg x \neg y + xy \Rightarrow 0) \cdot (\neg x \neg y + x \neg y \Rightarrow 1) \cdot (\neg x \neg y + x \neg y \Rightarrow 1) \cdot (\neg xy + x \neg y \Rightarrow 1)$$

$$= xy + (x + y)(\neg x + \neg y)$$

$$= x + y$$

$$Z_4 = xy + AXZ_3$$

$$= xy + \forall x'y'[(\neg x \neg y \neg x' + \neg x \neg y \neg y' + \neg xyx'y' + xy \neg x' \neg y' + x \neg yy') \Rightarrow x' + y']$$

$$= xy + (\neg x \neg y + xy \Rightarrow 0) \cdot (\neg x \neg y + xy \Rightarrow 1) \cdot (\neg xy + xy \Rightarrow 1) \cdot (\neg xy + xy \Rightarrow 1)$$

$$= xy + (x + y)(\neg x + \neg y)$$

$$= x + y.$$

yielding x + y as the Boolean formula for AFs. Atomic proposition r has Boolean formula  $x \neg y$ , so CTL subformula  $r \Rightarrow$  AFs has Boolean formula  $x \neg y \Rightarrow x + y$ , which simplifies to 1. Computing the Boolean formula for the entire CTL formula AG $(r \Rightarrow$  AFs) requires another fixed point computation, which converges immediately to 1. Therefore, we know that all states in the structure satisfy the formula.

Note that all calculations described in this section can be done efficiently, provided the BDDs are reasonably small. Whether the BDDs are indeed small in practice remains to be seen.

#### 1.3 What This Thesis Is About

The research in this thesis falls under the general umbrella of symbolic model checking using BDDs. The emphasis of the work, however, is very specific. While most

current verification work with BDDs has focused on gate and switch-level designs, my emphasis is on the very highest levels of design, for example, checking communication and consistency-maintenance protocols in a very large system. As stated earlier, the goal is to provide a powerful debugging tool to catch conceptual errors early in the design cycle, when they are easier and cheaper to correct. Furthermore, my emphasis is explicitly practical and problem-driven, continually attempting interesting real problems in order to find the simplest tools that are still useful for a real user. Accordingly, I have restricted myself to a simple, very limited verification paradigm that has still proven useful for debugging a wide range of real, high-level designs [27] and instead concentrated on providing the techniques needed to bridge the gap between what is theoretically possible and what is practically feasible. In short, I have chosen to take something theoretically simple and try to make it useful on complex real problems, rather than taking something theoretically complex and apply it to simple problems.

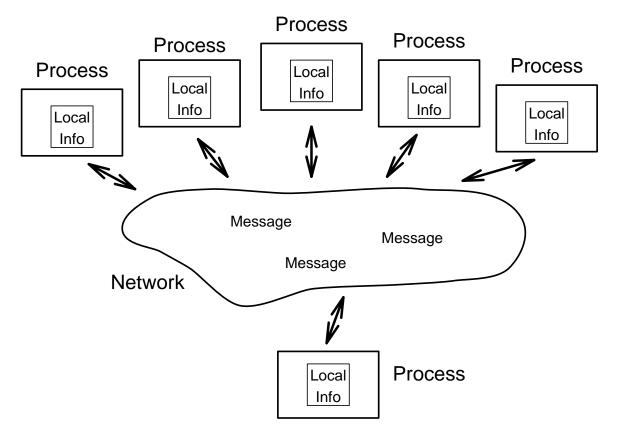

More concretely, I consider verifying only that every reachable state of a system satisfies a user-specified propositional logic formula (equivalent to model-checking only CTL formulas of the form AGp where p contains no modal operators). Formally, I model the system being verified as a single non-deterministic finite-state machine. Non-determinism is important for high-level verification both to model non-determinism in the environment and also to abstract away implementation details, allowing us to postpone making low-level decisions until we've finished high-level verification. Let the machine have state space Q, transition relation  $\delta: Q \times Q \to \{0,1\}$ , and a set of start states  $S \subseteq Q$ . The verification task is, given the set of "good" states  $G \subseteq Q$  that satisfies the property being verified, to determine if there exists a path starting from a state in S and leading to a state not in G, and, if such a path exists, to output it as a counterexample to the property being verified.

Before proceeding, we need a bit of notation:

**Definition 1.1 (Image Operators)** Given a set  $Z \subseteq Q$ , define the following operators:

$$Image(\delta, Z) = \{v | \exists u [u \in Z \land \delta(u, v)]\}$$

$$PreImage(\delta, Z) = \{u | \exists v[v \in Z \land \delta(u, v)]\}$$

$$BackImage(\delta, Z) = \{u | \forall v[\delta(u, v) \Rightarrow v \in Z]\}.$$

Intuitively, Image gives the set of states that can be reached in one transition from a state in Z, PreImage gives the set of states that in one transition can reach a state in Z, and BackImage gives the set of states that in one transition must end up in Z. These operators are by no means new: Image is essentially Floyd's strongest verifiable consequent [31], and BackImage is essentially Dijkstra's weakest precondition [26]. In CTL (with  $\delta$  implicit in the Kripke structure), PreImage( $\delta$ , Z) corresponds to EX[Z], and BackImage( $\delta$ , Z) corresponds to AX[Z]. Using the unified notation of dynamic logic [79], the expression Image( $\delta$ , Z) is precisely  $\langle \delta \rangle Z$ , and the expression BackImage( $\delta$ , Z) is precisely [ $\delta$ ]Z.

Using these image operators, it's easy to explain the standard approaches to our verification problem. One standard algorithm I call "forward traversal." The intuition is that we iteratively compute the set  $R_i$  of states that can be reached in i or fewer transitions from the start states. Mathematically, we initialize  $R_0 = S$ , and compute  $R_{i+1} = R_0 \vee \text{Image}(\delta, R_i)$ . If  $R_i$  ever goes outside the set of good states  $(R_i \not\subseteq G)$ , then we have a violation, and it's easy to produce a counterexample trace. Otherwise, the sequence will eventually converge to the set of reachable states, meaning that the verification succeeds. (The predicate transformation is monotonic on a finite Boolean lattice, so convergence is guaranteed.) Details of this approach are available elsewhere (e.g., [22, 11, 16, 85, 9]). The other standard algorithm I call "backward traversal." The intuition here is that we iteratively compute the set  $G_i$  of states such that all paths of length i or less starting in  $G_i$  must remain within the set of good states G. Mathematically, we initialize  $G_0 = G$ , and compute  $G_{i+1} = G_0 \wedge \text{BackImage}(\delta, G_i)$ .

<sup>&</sup>lt;sup>8</sup>An alternative formulation that is perhaps more intuitive is  $R_{i+1} = R_i \vee \operatorname{Image}(\delta, R_i)$ . Both formulas compute the same  $R_i$  for all i. An advantage of the formula given in the text is that  $R_0$  is often a simple property with smaller BDD than  $R_i$ . An advantage of the alternative formulation is that we can actually compute the image on any set S such that  $R_i - R_{i-1} \subseteq S \subseteq R_i$ , giving  $R_{i+1} = R_i \vee \operatorname{Image}(\delta, S)$ . This formula still generates the same  $R_i$  for all i, but the image computation can be faster if we can find at each iteration an S with BDD representation smaller than  $R_i$  [22, 21]. Note that combining these tricks into  $R_{i+1} = R_0 \vee \operatorname{Image}(\delta, S)$  is **not** guaranteed to produce the same sequence, and indeed may produce a sequence that is non-monotonic.

If we reach a point where  $G_i$  does not contain all of the start states ( $S \nsubseteq G_i$ ), then there exists a sequence of i transitions from a start state to a violating state. Otherwise, the sequence will converge, meaning the verification succeeds. (Again, convergence follows immediately from monotonicity and finiteness.) Details for this approach are also available from several sources (e.g., [10, 75, 30]). Incidentally, these two approaches are actually duals of each other, based on the dynamic logic duality between forward and backward execution of a program [79].

At this point, I appear to be done: I've stated a simple verification problem and have given two standard algorithms to solve it. We just build BDDs for  $\delta$  and the  $R_i$ s or  $G_i$ s, compute the image operators using Definition 1.1, and crank through the iterations described in the preceding paragraph. However, although indulging my Inner Theoretician by declaring victory and moving on to more mathematically beautiful verification problems is tempting and certainly valuable, I've explicitly set out to provide a practical solution to practical problems, so I need to indulge my Inner Practitioner first. As often happens, the difference between theory and practice emerges in the practice. Despite the extreme simplicity of our verification problem, several obstacles prevent the practical usefulness of direct implementations of the standard approaches on an enormous range of real problems. In particular, describing a complex system directly with BDDs is difficult and error-prone, the BDD for  $\delta$  is frequently too large to build, and the BDDs for the  $R_i$ s and  $G_i$ s are frequently too large to build as well. This thesis addresses these problems.

# Chapter 2

#### Translation into BDDs

#### Chapter Overview<sup>1</sup>

An enormous semantic gap lies between the low-level Boolean logic supported by BDDs and the high-level descriptions of systems we wish to verify. The first part of this chapter motivates the need to support high-level language constructs for these high-level descriptions and identifies an empirically useful set of constructs: data structures consisting of scalars, arrays, and records; expressions built from boolean and arithmetic operators; and control flow based on conventional assignment statements, sequence, if-then-else, and non-deterministic choice. The remainder of the chapter describes how to translate these language constructs automatically into BDDs.

#### 2.1 High-Level Language Constructs

The first step in BDD-based verification is to use Boolean formulas to describe the system being verified. For high-level verification, writing and maintaining such low-level descriptions can be a major obstacle. Allow me to illustrate with a personal

<sup>&</sup>lt;sup>1</sup>This chapter is based on material first published in the Fourth International Workshop on Computer-Aided Verification, 1992 [44].

anecdote. The seed of the Stanford Mur $\varphi$  group began in the spring of 1990. Inspired by recent stories of success with BDD-based model checking [10, 67], we set out to use BDD-based verification to help debug the directory-based cache coherence protocol of the Stanford DASH multiprocessor [59], then well under development. The results were humbling. The task of modeling the high-level description of the system in Boolean logic proved to be enormously time-consuming and error-prone. Furthermore, subtle modeling errors were hard to detect, as a hard-to-spot typographical error in the Boolean description can silently delete transitions from the transition relation. Worse, upon finding an error in our model, the task of revising a description written in Boolean logic was difficult and even more error-prone. The killing blow was that if we wanted to scale the description to have more or less memory or processors, we essentially needed to rewrite the description from scratch. The end result was that we were unable to produce useful verification results in a timely manner. In retrospect, McMillan and Schwalbe's success story that had inspired us — verifying a hierarchical snooping cache coherence protocol [67] — should also have forewarned us, as they too complained that the low-level Boolean descriptions were very cumbersome for high-level verification. Clearly, high-level verification with BDDs required better tool support.

We learned two main language-design lessons from this experience. First, descriptions must be easy to revise and modify. This requirement is true for programming in general but is particularly compelling for high-level prototyping, debugging, and verifying, as we need and expect to iterate the modify-check-debug cycle very quickly and very often. A particularly important revision for state-exploration verification is scaling. Often, we cannot verify the system in its full complexity, so being able to quickly scale the sizes of various parts of the description (e.g., number of processors, number of addresses, size of buffers, etc.) is crucial to be able to find bugs [27]. The other language-design lesson is that the description language must be semantically close to the way the user normally writes descriptions. Thus, the verification system must support the data structures, the imperative semantics, and the control flow typical of current programming languages. A particularly unpleasant mismatch between imperative semantics and logic is an instance

of the Frame Problem in AI [66]: in imperative semantics, when modifying a variable, any other variable that isn't mentioned doesn't change; in logic, any variable that isn't mentioned is completely unconstrained. While it's straightforward but tedious to translate an imperative assignment like " $\mathbf{x} := \mathbf{1}$ " into the next-state relation<sup>2</sup>  $(x'=1) \wedge (y'=y) \wedge (z'=z) \wedge \cdots$  (a clause for every variable)  $\cdots$ , it's arduous, error-prone, and still tedious to translate something (taken from an industrial cache coherence protocol) like:

```

If (i < Homes[h].Dir[a].Shared_Count) &

(Homes[h].Dir[a].Entries[i] = n)

Then

-- overwrite this entry with last entry.

Homes[h].Dir[a].Entries[i] :=

Homes[h].Dir[a].Entries[Homes[h].Dir[a].Shared_Count-1];

-- clear last entry

Homes[h].Dir[a].Entries[Homes[h].Dir[a].Shared_Count-1] := 0;

Homes[h].Dir[a].Shared_Count := Homes[h].Dir[a].Shared_Count-1;

Endif;</pre>

```

The user should not be forced to perform such a translation by hand.

The objective, therefore, is to support a high-level description language, counterbalanced by the need to keep the description finite-state and comfortably within the bounds of our verification paradigm. For example, to allow easy scalability and high-level descriptions, the language must support scalar-valued variables (integer and enumerated types) as well as complex data structures built from records and arrays. Pointers, however, would allow infinite-state descriptions and must therefore be disallowed. Once the language permits scalar-valued variables, it obviously must provide adequate means to manipulate them, such as built-in operators for addition, subtraction, comparison, etc. Providing a built-in imperative assignment frees the user from the onerous and error-prone translation described in the preceding paragraph. For control flow, the imperative assignment goes hand-in-hand with sequential control

<sup>&</sup>lt;sup>2</sup>Recall from Chapter 1 that a primed variable denotes the value of the variable in the next state.

flow and if-then-else, which are basic control structures that the user expects to have. While-loops, however, would require a nested fixed point computation, which is too expensive to support. A non-deterministic choice operator provides a convenient high-level means to introduce non-determinism and implement guarded command sets [26]. Finally, some sort of subroutine mechanism is needed to provide modularity, but we cannot permit recursion, which could violate the finite-state restriction.

We built the non-BDD-based  $Mur\varphi$  verifier around these language features [27], embedded into an iterated, guarded command framework inspired by the UNITY language [13]. That these language features are sufficiently high-level and easy-to-use is clear from the consistent praise  $Mur\varphi$  has drawn on ease of use and description language convenience (e.g., [88, 86]). That these language features can be translated into BDDs is the subject of the following section.

#### 2.2 Translation

As noted in Chapter 1, symbolic model checking requires that the system be modeled by a transition relation on the current and next state values of the state variables. The preceding section listed the set of high-level language features we wish to support. This section shows how to translate these features automatically into transition relations in Boolean logic, suitable for implementation with BDDs. I have implemented the automatic translation in the Ever verification system, described in more detail in Appendix A.

I assume the preceding section's desirable language features are combined in the typical manner into an Algol-style language. The translation process is syntax-directed, traversing the high-level description recursively, building the Boolean formulas for the subparts of a given part of the description and then combining the formulas for the subparts into the Boolean formula(s) for the part. I will describe the routines that perform this translation starting from the bottom-level translation routines and proceeding to the top, which converts the entire high-level description into a transition relation in Boolean logic.

The process of translation requires manipulating different representations of the

same conceptual objects, making explaining the process potentially confusing; introducing some concepts and notation eases the exposition. The translation routimes generate three main types of results: Boolean conditions, scalar quantities, and transition relations that correspond to subparts of the high-level description. Both Boolean conditions and transition relations are represented by single Boolean functions, although keeping these two concepts distinct is helpful. In particular, the Boolean formula for a condition refers only to variables for the current state or only to variables for the next state, but not to both, whereas the Boolean formula for a transition relation typically refers to variables for both the current and the next state of the system. Scalar quantities are represented by vectors of Boolean formulas, which give the binary encoding of the scalar value. For a given part P of the high-level description, let BFUN(P), BVEC(P), or TR(P), whichever is appropriate, denote the result of translating P into a Boolean formula, a vector of Boolean formulas, or a transition relation, respectively. Unless otherwise specified, Boolean operations performed on vectors of Boolean formulas should be interpreted as applying component-wise. Subscripts specify particular formulas within a vector of Boolean formulas, with 0 referring to the low-order bit. For example,  $BVEC(13)_1$  is False, and  $BVEC(x)_0$  refers to the low-order bit of x. By default, Boolean formulas and vectors of Boolean formulas should be assumed to refer to the current state variables; a tick mark applied to any expression indicates that the expression refers to the next state variables instead. For example, BFUN(x < 42) is a Boolean formula that specifies that the current value of x is less than 42, whereas BFUN(x < 42)' is a Boolean formula that specifies that the next value of x is less than 42. Note that the expression BFUN(x' < 42) is meaningful only if "x' < 42" is meaningful in the high-level description language; if the description language uses "x'" to denote the next value of x, then BFUN(x' < 42) = BFUN(x < 42)'.

#### 2.2.1 Constants and Variables

For an integer constant c, the translation BVEC(c) is simply the binary representation of c. Enumerated types can be handled by associating each enumeration constant with an integer, exactly as a normal compiler does. Note that other encodings of

finite domains into Boolean variables are possible [53], but the binary encoding is advantageous in supporting a high-level description language because it simplifies automatic translation of arithmetic and logical expressions, as we shall see shortly.

Variable declarations are handled exactly as in a normal compiler, except that rather than allocating bits of memory for the high-level variables, the translator allocates entries in an array of Boolean variables. Call this array V, with the notation  $V_i$  indicating the ith Boolean variable and the notation  $V_i[s]$  indicating the s Boolean variables starting with the ith one. I will assume a Pascal or C-like type system, in which the base types are integers and enumerations, and additional types can be constructed as records whose fields are of previously defined types and as arrays whose elements are of a previously defined type. For any type, a straightforward recursive computation tells how many Boolean variables are needed to represent it: the size of a scalar is the number of bits used to represent it, the size of a record is the sum of the sizes of its fields, and the size of an array is the product of the number of elements in the array and the size of an array element. A related quantity is the offset from the start of a record or an array at which a specific record field or array element starts. The offset is easily computed as the sum of the sizes of the record fields or array elements that precede the specified one. I will use the notation SIZEOF(x) to denote the size of a variable or type x and the notation OFFSET(x) to denote the offset to the start of the field named x or the xth element in an array (using context to disambiguate which I mean). When a new variable x is declared, its size and offset (We can treat all variables as fields in a global record that starts at  $V_0$ .) are stored in the symbol table, and the Boolean variables  $V_{OFFSET(x)}[SIZEOF(x)]$  are allocated for variable x.

Recall from Section 1.2.3 the importance for BDDs of choosing a good variable ordering. Ideally, such a detail should not belong in the high-level description; the translator should choose a good order automatically. Unfortunately, current variable ordering heuristics for high-level descriptions are not as good as what a human can do, so the user needs some means to provide variable ordering hints to the translator. For example, for an array, in some instances ordering all the BDD variables for one array element before all of the BDD variables of the next array element is the best

choice; in other instances, interleaving the corresponding bits (most significant bits first, followed by the next most significant bits, etc.) is better [83, 53]. The user can use intuition or a result like Jeong *et al.*'s Non-Interleaving Lemma [51]<sup>3</sup> to decide which order to use and must be able to tell the translator to do so.

When an expression refers to a variable (possibly with record field accesses and array indexing), the translation process is again very similar to what a normal compiler does, except that rather than generate instructions that compute the correct address offset, the translation into Boolean logic generates a vector of case expressions that select the correct Boolean variables. For a simple variable reference, the translator looks up in the symbol table the offset to the correct BDD variables much as a compiler would generate the offset to the start of the correct block of memory. The Boolean variables starting at that offset form the correct vector of Boolean formulas. For a record field access, start with the base variable as before, add the field offset, and proceed as in the case of the simple variable reference. Array indexing is the most complex. If the index were a constant, we could proceed as for records. The index, however, can be an arbitrary scalar-valued expression. For example, an expression like a[x + 4] should be translated into a vector of Boolean formulas that, when restricted to having x = 0, are equivalent to the Boolean formulas for a[4]; when restricted to having x = 1, are equivalent to a[5]; and so forth. Therefore, the formulas for an array access must perform a case analysis for each possible value of the array index.

More formally, the translation of a variable reference can be expressed by a recursive computation. Define a modifier to be either a field name or an array-indexing expression. Since we can consider a variable to be just a field in a global record structure, any variable reference is just a list of modifiers. Given an arbitrary variable reference  $\rho$ , the translation BVEC( $\rho$ ) is given by the function SELECTBITS:

$$\mathsf{BVEC}(\rho) \stackrel{\mathsf{def}}{=} \mathsf{SELECTBITS}(\rho, 0, \mathsf{SIZEOF}(\rho)).$$

<sup>&</sup>lt;sup>3</sup>In an unfortunate clash of terminology, what I and Srinivasan *et al.* [83] call an interleaved variable order, because the bits comprising the scalars are interleaved, creates what Jeong *et al.* call a non-interleaved order, because the Boolean relations for the individual bit-slices have disjoint supports and are grouped together.

In defining SELECTBITS, recall that operations on vectors of Boolean formulas should be assumed to be applied component-wise. Two exceptions are  $\stackrel{*}{=}$ , which denotes checking equality of two vectors of Boolean formulas and returns a single Boolean formula, and  $\stackrel{*}{\Rightarrow}$ , which denotes a single Boolean formula implying a vector of Boolean formulas and returns the vector in which the implication was applied to each component. For example, BVEC(12) = BVEC(7) yields the result (False, True, False, False), whereas  $BVEC(12) \stackrel{*}{=} BVEC(7)$  yields the result False. With this notation, we define SELECTBITS recursively as follow:

$$\begin{split} & \text{SELECTBITS}(\epsilon, \text{offset}, \text{size}) \stackrel{\text{def}}{=} V_{\text{offset}}[\text{size}] \\ & \text{SELECTBITS}(\textit{field\_name} :: \sigma, \text{offset}, \text{size}) \stackrel{\text{def}}{=} \\ & \text{SELECTBITS}(\sigma, \text{offset} + \text{OFFSET}(\textit{field\_name}), \text{size}) \\ & \text{SELECTBITS}(\textit{index\_expr} :: \sigma, \text{offset}, \text{size}) \stackrel{\text{def}}{=} \\ & \bigvee_{i=l}^{u} \begin{bmatrix} \text{BVEC}(\textit{index\_expr}) \stackrel{*}{=} \text{BVEC}(i) \\ & \stackrel{*}{\Rightarrow} \\ \text{SELECTBITS}(\sigma, \text{offset} + \text{OFFSET}(i), \text{size}) \end{bmatrix}, \end{split}$$

where  $\sigma$  is a (possibly empty) list of modifiers,  $\epsilon$  is the empty list, :: is the list cons operator, and l and u are the lower and upper bounds of the array. The actual implementation also requires type information for the variables to be propagated through the recursive calls in the obvious way; I have omitted this detail for brevity. We will see how to compute  $BVEC(index\_expr)$  in a moment. The generated formulas are essentially banks of multiplexors whose select lines are driven by the array-indexing expressions and whose inputs are the BDD variables. The formula for array indexing can be considered a scalar-valued generalization of work by Beatty  $et\ al.\ [2]$ .

# 2.2.2 Arithmetic and Logical Expressions

Compared to the translation of variable references, the translation of arithmetic and logical expressions is easy. I assume that the translator can parse expressions in the

29

high-level language and perform type checking using standard compiler techniques. Thus, the task of translating arbitrary expressions can be broken down into defining the translation of each supported operator, assuming its operands have been properly translated already. The translator applies these rules recursively on the parse tree, first translating the subexpressions that are the arguments of an operator, and then using the specific translation rules for that operator. The base cases of the recursion are the translations for variable references and constants.

Keep in mind that the translation process does not compute the result of the operation; it generates Boolean functions that compute the result of the operation for all input values. For example, if the translation BVEC(expr) is the vector of Boolean formulas  $(f_3, f_2, f_1, f_0)$ , the translation of expr - 4 would be the vector of formulas  $(f_3 = f_2, \neg f_2, f_1, f_0)$ .

The use of the standard unsigned binary representation to encode integers makes defining the translation of common arithmetic operators easy.<sup>4</sup> Let's consider some representative examples: addition, less-than, and a conditional expression.

Suppose the high-level description contains the expression "expr1 + expr2", where expr1 and expr2 are arbitrary scalar-valued expressions. As stated above, we first apply the translation recursively on the subexpressions. Let x be the translation BVEC(expr1), and let y be the translation BVEC(expr2). Compute the vector of Boolean formulas z by the following rules:

$$c_{-1} \stackrel{\text{def}}{=} \text{False}$$

$$z_i \stackrel{\text{def}}{=} x_i \oplus y_i \oplus c_{i-1}$$

$$c_i \stackrel{\text{def}}{=} (x_i \wedge y_i) \vee (c_{i-1} \wedge (x_i \vee y_i)),$$

with  $\oplus$  denoting exclusive-OR. These rules implement addition by a ripple-carry adder. Note that since BDDs are canonical, using this simple adder structure gives

<sup>&</sup>lt;sup>4</sup>Not surprisingly, we are actually encoding integers modulo  $2^k$ , where k is the number of bits we've allocated for the result. Two's complement permits handling negative numbers with minimal hassle. If the high-level language makes extensive use of negative numbers, the translation should be modified slightly to handle signed comparison (versus the unsigned comparison given in the text) and sign extension issues, just as a normal compiler does.

the exact same final result z as using a more complicated adder. The translation BVEC(expr1 + expr2) is just the vector z.

As a second example, suppose the high-level description contains the expression "expr1 < expr2", where again expr1 and expr2 are arbitrary scalar-valued expressions. Note that in this example, the result should be a single Boolean formula, rather than a vector of Boolean formulas, so the translation is denoted by BFUN rather than BVEC. This type inference is a function of the high-level language, not the translation process, and can be handled by standard compiler techniques. As in the preceding example, let x be the translation BVEC(expr1), and let y be the translation BVEC(expr2). Compute a sequence of Boolean formulas:

$$z_0 \stackrel{\text{def}}{=} \text{False}$$

$$z_i \stackrel{\text{def}}{=} (\neg x_i \land y_i) \lor ((x_i = y_i) \land z_{i-1}).$$

The translation BFUN(expr1 < expr2) is just the Boolean formula  $z_i$  for i equal to the larger of SIZEOF(x) and SIZEOF(y). (If one expression is smaller than the other, pad the smaller with leading 0s for the computation of z. Small adjustments like this are needed for all operations.)

As a final example, consider a conditional expression: "cond?expr1:expr2" in C syntax. Let x be BVEC(expr1) and y be BVEC(expr2) as in the previous examples. Let c be BFUN(cond). Compute the vector of Boolean formulas z:

$$z_i \stackrel{\text{def}}{=} (c \wedge x_i) \vee (\neg c \wedge y_i),$$

padding the smaller of x and y as before. The translation BVEC(cond?expr1:expr2) is just z.

Translation rules for many other operators are similar.

#### 2.2.3 Assignment

So far, we have only considered translating the bottom-level parts of a description: constants, variables, and expressions. Now, we have developed enough machinery

to translate our first construct that generates a transition relation: an assignment statement. The assignment statement, in turn, will be the basis for inductively constructing high-level descriptions.

To translate an assignment statement, we use a computation similar to the variable reference computation described above. Now, however, we must build a transition relation that specifies that every Boolean variable that isn't modified in the assignment keeps its current value. Doing so resolves the mismatch mentioned earlier between imperative and logical semantics. For records, generating this relation is straightforward. For each field not being accessed, we AND into the Boolean relation being generated the further requirement that the field not change. For the field that we do access, we equate a variable reference expression like those we generated previously with the right-hand side of the assignment. For arrays, we must again perform a case analysis.

Formally, given assignment statement "var := expr", let  $\rho$  be the list of modifiers that corresponds to the variable reference var. As with the computation for a variable reference, we define the translation TR(var := expr) by a recursive helper function:

$$TR(var := expr) \stackrel{\text{def}}{=} ASSIGN(\rho, 0, SIZEOF(\rho), expr).$$

$\operatorname{ASSIGN}(\epsilon, \operatorname{offset}, \operatorname{size}, \operatorname{expr}) \stackrel{\operatorname{def}}{=} (V_{\operatorname{offset}}[\operatorname{size}]' \stackrel{*}{=} \operatorname{BVEC}(\operatorname{expr}))$

The recursive definition of ASSIGN is similar to that of SELECTBITS:

ASSIGN(field\_name ::

$$\sigma$$

, offset, size, expr)  $\stackrel{\text{def}}{=}$

$$ASSIGN(\sigma, \text{offset} + \text{OFFSET}(field\_name), \text{size}, \text{expr}) \qquad \land \\ \bigwedge_{\substack{f \in record\_fields \\ f \neq field\_name}} \begin{pmatrix} V_{\text{offset}+\text{OFFSET}(f)}[\text{SIZEOF}(f)]' \stackrel{*}{=} \\ V_{\text{offset}+\text{OFFSET}(f)}[\text{SIZEOF}(f)] \end{pmatrix}$$

$ASSIGN(index\_expr :: \sigma, offset, size, expr) \stackrel{\text{def}}{=}$

$$\bigwedge_{i=l}^{u} \begin{bmatrix} \text{if BVEC}(index\_expr) \stackrel{*}{=} \text{BVEC}(i) \\ \text{then} \\ \text{ASSIGN}(\sigma, \text{offset} + \text{OFFSET}(i), \text{size}, \text{expr}) \\ \text{else} \\ \begin{pmatrix} V_{\text{offset}+\text{OFFSET}(i)}[\text{SIZEOF}(element)]' \stackrel{*}{=} \\ V_{\text{offset}+\text{OFFSET}(i)}[\text{SIZEOF}(element)] \end{pmatrix} \end{bmatrix},$$

where  $\sigma$  is a list of modifiers,  $\epsilon$  is the empty list, :: is the list **cons** operator, and l and u are the lower and upper bounds of the array.

A non-deterministic assignment statement, in which a variable is assigned any value that satisfies some user-specified condition, can be implemented by essentially the same computation, except the base case of the recursion is the condition on the variable rather than the expression  $(V_{\text{offset}}[\text{size}]' \stackrel{*}{=} \text{BVEC}(\text{expr}))$  above. For example, the translation of an assignment statement that says, "Let x have any value less than 42." would proceed exactly as above for a normal deterministic assignment to x, except the base case of the recursion would be BFUN(x < 42)'.

#### 2.2.4 Control Flow

With the assignment statement as the basis, we can define compound statements for the high-level language features we wish to support (sequence, if-then-else, and non-deterministic choice) inductively in the usual manner. If  $s_1, \ldots, s_n$  are statements, then the sequence of statements " $s_1; \ldots; s_n$ " (executed sequentially in order) is also a statement. If  $s_1$  and  $s_2$  are statements and c is a conditional expression, then "if c then  $s_1$  else  $s_2$  endif" is also a statement. If  $s_1, \ldots, s_n$  are statements, then the non-deterministic choice of one of them, denoted here by the expression " $s_1|\ldots|s_n$ ", is also a statement. The description of the entire transition relation, therefore, is just a single statement, albeit a complex one.