### Asynchronous Serial Interface for Connecting a PDP-11 to the ARPANET (BBN 1822)

by

Ronald C. Crane

July 1976

#### Technical Report No. 116

The views and conclusions contained in this document are those of the author and should not be interpreted as necessarily representing the officia I policies, either express or implied, of the Defense Advanced Research Projects Agency or the United States Government.

This research was supported by the Defense Adva nced Resea rc h Projects Agency under ARPA Order No. 2494, Contract No. MDA903-76C -0093.

## DIGITAL SYSTEMS LABORATORY STANFORD ELECTRONICS LABORATORIES

STANFORD UNIVERSITY • STANFORD, CALIFORNIA

Asynchronous Serial Interface for Connecting a PDP-11 to the ARPANET (BBN 1822)

Technical Report No. 116

July 1976

Ronald C. Crane Digital Systems Laboratory Departments of Electrical Engineering and Computer Science Stanford University Stanford, California

#### ABSTRACT

This report describes an interface to permit the connection of any PDP-11 to either the Packet radio network or the ARPAnet. The interface connects to an IMP on one side, meeting the specifications published in BBN report number 1822, and to a 16 bit parallel interface (DRV-11 or DR11-C) as described in the DEC peripherals and interfacing handbook. The interface card itself is a double height board  $(5.2"\times8.5")$  which can be plugged into any peripheral slot in a PDP-11 backplane. The interface card is connected to the parallel interface card via two cables with Berg 40 pin connectors (DEC H-856) and to the IMP via an Amphenol bayonet connector (48-10/R-18-315). All 3 cables and connectors are supplied with the I/O interface card. The parallel interface card (DEC DR11-C or DRV-11) together with the special I/O interface card described in this report conprise the 1822 interface. The report includes descriptions of the operation of circuits, programming, and diagnostics for the 1822 interface.

#### KEY WORDS

BBN 1822 INTERFACE, HOST-IMP INTERFACE, LSI-11, PDP-11, DRV-11, DR11-C PACKET-RADIO-HOST INTERFACE, ASYNCHRONOUS SERIAL INTERFACE, ARPANET

The views and conclusions contained in this document are those of the author and should not be interpreted as necessarily representing the official policies, either express or implied, of the Defense Advanced Research Projects Agency or the United States Government.

This research was supported by the Defense Advanced Research Projects Agency under ARPA Order No. 2494, Contract No. MDA903-76C-0093

ł

#### Table of Contents

.

-

-

-

•

| Section |          | Contents                                                                                                                                                                                           | Page |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.0     | Introduc | tion                                                                                                                                                                                               | 3    |

|         | 1.1      | Block Diagram                                                                                                                                                                                      | 3    |

| 2.0     | Transmit | Section                                                                                                                                                                                            | 5    |

|         | 2.1      | Host Power Relay                                                                                                                                                                                   | 5    |

|         | 2.2      | Data Section<br>2.2.1 Data Path<br>2.2.2 Handshaking Procedure<br>2.2.3 Last Host Data Bit Signa<br>2.2.4 Transmit Enable<br>2.2.5 Initialize Pulse<br>2.2.6 Load Pulse<br>2.2.7 Interrupt Request | 5    |

| 3.0     | Receive  | Section                                                                                                                                                                                            | 10   |

|         | 3.1      | IMP Power Sensing                                                                                                                                                                                  | 10   |

|         | 3.2      | Data Section<br>3.2.1 Interrupt Request<br>3.2.2 Initialize & Read Pulses<br>3.2.3 Bit 15 Output<br>3.2.4 Data<br>3.2.5 Bit Count<br>3.2.6 Receiver Timing                                         | 10   |

| 4.0     | Electric | al Specifications                                                                                                                                                                                  | 16   |

|         | 4.1      | Line Drivers and Receivers                                                                                                                                                                         |      |

|         | 4.2      | Power Distribution on Board                                                                                                                                                                        |      |

| 5.0     | Changing | Time Delays                                                                                                                                                                                        | 19   |

| 6.0     | Connecto | rs                                                                                                                                                                                                 | 20   |

|         | 6.1      | Loopback Test Connector                                                                                                                                                                            | 21   |

| 7.0     | Programm | ling                                                                                                                                                                                               | 23   |

|         | 7.1      | Status Register                                                                                                                                                                                    | 23   |

|         | 7.2      | Input and Cu <b>tput</b> Buffers                                                                                                                                                                   | 23   |

е

|     | 7.3        | Transmit Register<br>7.3.1 Data Section<br>7.3.2 Control Section                                                                     | 24 |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 7.4        | Receive Register<br>7.4.1 Data<br>7.4.2 Control                                                                                      | 25 |

|     | 7.5        | Reference Tables                                                                                                                     | 26 |

| 8.Q | Diagnostic | CS                                                                                                                                   | 29 |

|     | 8.1        | Packet Source/Sink Program<br>8.1.1 Description of Program<br>8.1.2 Running Source/Sink Program<br>8.1.3 Source/Sink Program Listing | 29 |

|     | 8.2        | Scope Loop<br>8.2.1 Running Scope Program<br>8.2.2 Using Scope Loop                                                                  | 32 |

|     | Appendix   |                                                                                                                                      | 34 |

|     | A          | DR11-C Specifications                                                                                                                | 35 |

|     | В          | Parts list for Interface                                                                                                             | 4Ø |

,

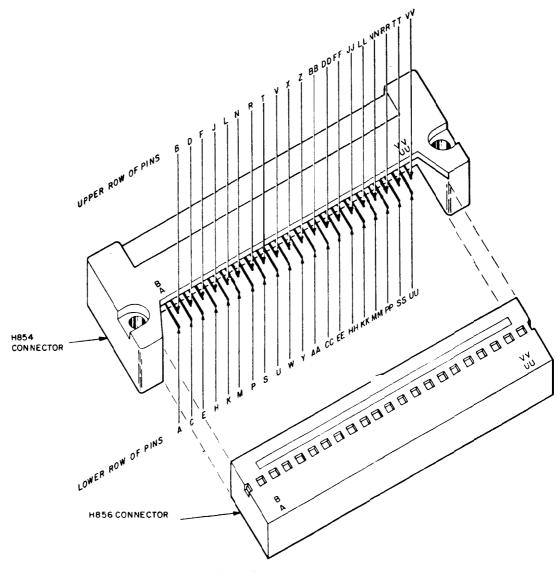

This report describes an interface to permit the connection of any PDP-11 to either the Packet radio network or the ARPAnet. The interface connects to an IMP on one side, meeting the specifications published in BBN report number 1822, and to a 16 bit parallel interface (DRV-11 or DR11-C) as described in the DEC peripherals and interfacing handbook. The interface card itself is a double height board (5.2"x8.5") which can be plugged into any peripheral slot in a PDP-11 backplane. The interface card is connected to the parallel interface card via two cables with Berg  $4\emptyset$ pin connectors (DEC H-856) and to the IMP via an Amphenol bayonet connector (48-10R-18-31S). All 3 cables and connectors are supplied with the I/O interface card. The parallel interface card (DEC DR11-C or DRV-11) together with the special I/O interface card described in this report comprise the 1822 interface.

Except for differences in handling the IMP power relay status, this interface reflects the current prototype as constructed by SRI. In the SRI unit, an interrupt is continuously generated when the IMP goes down. The interrupt generation can be stopped by disabling the receiver, after which it is necessary to poll the interface to see if the IMP comes back up. The interface described here generates one interrupt on each change of state of the IMP.

The following sections describe the operation of circuits, programming, and diagnostics for the 1822 interface.

1.1

#### Block Diagram

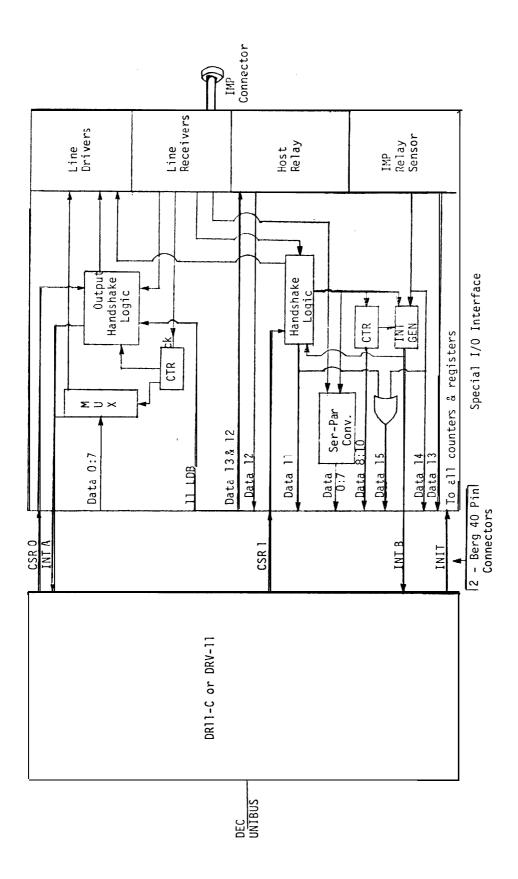

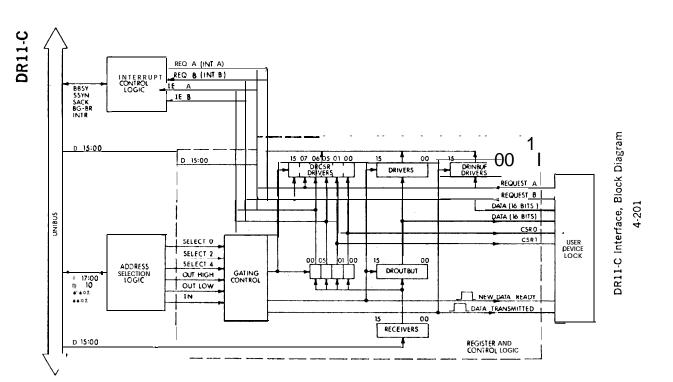

The block diagram shows the basic parts of the special I/O interface card and its connections to the parallel interface card and the IMP.

The parallel interface card performs interrupt control on the PDP-11 unibus. It has 3 addresses on the Unibus; the control and status register, the output register, and the input gate. The status register includes both the interrupt enable bits as well as the transmit and receive enable bits. The output register is a buffer whose contents change only when the interface is loaded (written into). The input gate does not contain a buffer. Its function is only to gate its input signal to the Unibus. Thus the data sections of the I/O card need only store data for the receiver, but not the transmitter. A block diagram and description of the parallel interface unit supplied by DEC are in the appendix.

In the following section, the reader is referred to the block diagram as well as the circuit and timing diagrams that follow.

Figure 1 FUNCTIONAL BLOCK DIAGRAM The transmitter has two independent sections. One is the power relay and the other is the data section.

2.1 Host Power Relay

Bits 12 and 13 in the output register control the host power relay contacts. They are the R and S inputs to an R-S flip flop. Setting bit 12 closes the contacts, and setting bit 13 opens the contacts. If both bits are on, the contacts will be closed. If both bits are simultaneously cleared after both being set, the resulting contact position is indeterminate.

| <u>Last State</u> | New   | State | Contact Status  |

|-------------------|-------|-------|-----------------|

| Bit Bit           | Bit   | Bit   |                 |

| 13 12             | 13    | 12    |                 |

| ( any )           | 0     | 0     | No change       |

| (any)             | 0     | 1     | Contacts closed |

| ( any )           | 1     | 0     | Contacts open   |

| (any)             | 1     | 1     | Contacts closed |

| 1 1               | 0     | 0     | Indeterminate   |

| Initialize        | Pulse |       | Contacts open   |

Bits 12 and 13 need to be set only once, as can be seen from the table, since the state of the relay remains at its previous setting when bits 12 and 13 are both zero.

Since the transmit register cannot be used to read out the state of the relay, bit 13 of the receive register is used for that purpose. Bit 13 is a 1 if the contacts are open, and 0 if they are closed.

| Bit 13 of INBUF | Contact | position |       |      |

|-----------------|---------|----------|-------|------|

| 0               | CLOSED  | (Host    | power | on)  |

| 1               | OPEN    | (Host    | power | off) |

The relay used is a Magnecraft W107-DIP-1 reed relay. Magnecraft claims the contact bounce is less than 500 microseconds. Therefore to be safe, no data should be transmitted until 1 millisecond after the relay is closed. This means that bit 12 of the transmit register ( OUTBUF ) must be set before transmit enable is 'set to prevent the interface from transmitting a byte when the power bit is set.

#### 2.2 Data Section

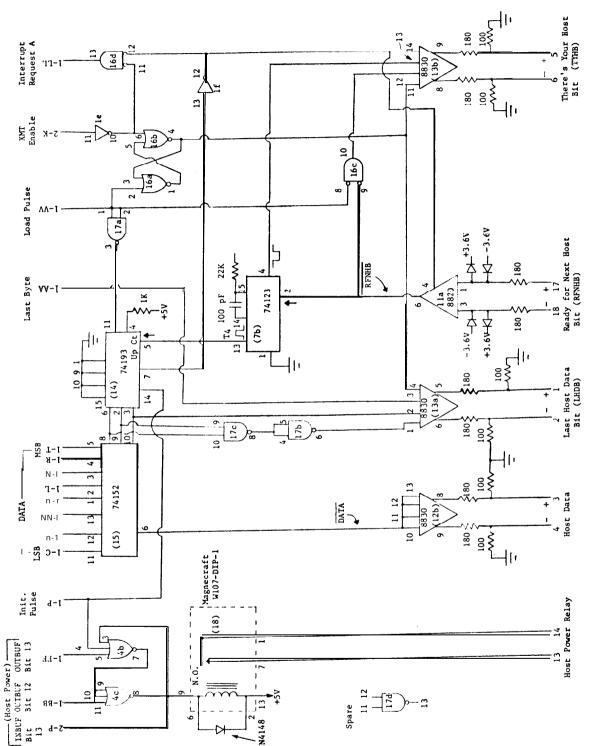

The data section of the transmitter is an 8 bit parallel to serial converter implemented with a multiplexer. The 8 bit data byte and control information are supplied by the DR11-C whose output buffer holds these values until they are replaced by new data and control information.

2.0

#### 2.2.1 Data Path

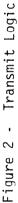

The actual parallel to serial conversion is done by an 8 line multiplexer (74152), which selects bits 7 to 0 of the output buffer and directly feeds the output driver. The bit selection is done by the low order 3 bits of a 4 bit binary counter (74193). The counter starts at zero and is advanced one count each time the RFNHB (Ready for Next Host Bit) line makes a high to low transition. On the 8th count the high order bit becomes a 1 and is used to inhibit further counting and also to generate a transmit interrupt request.

#### 2.2.2 Handshaking Procedure

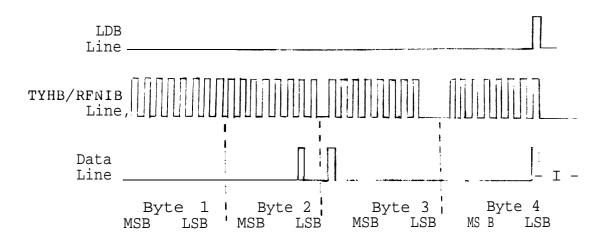

When the RFNHB line goes high, and transmit enable is a 1 (enabled), the TYHB (There's Your Host Bit) line goes high indicating availability of a data bit. RFNHB eventually goes low indicating acceptance of data. This triggers the 74123 pulse generator generating a pulse T4 seconds long The leading edge of the pulse (nominally 1 microsecond). advances the counter. The TYHB line is held low for at least the duration of the pulse, and possibly longer if the RFNHB line remains low for longer than the pulse duration. Usinq the pulse generator provides a straightforward method of meeting the minimum pulse width requirements for the 2-Way handshake. This is useful when operating over long cables. For systems using only a 4-Way handshake, a simple time delay would suffice as long as it is long enough to allow the counter and multiplexer to settle after being advanced (See transmit timing diagram for details).

#### 2.2.3 Last Host Data Bit (LHDB) Signal

The LHDB signal is asserted if the Last Byte signal is present (bit 11 in OUTBUF is a 1) and the counter is selecting the last bit of the byte to be transmitted. The timing for this signal coincides with the timing for the data signal.

#### 2.2.4 Transmit Enable

The transmit enable signal is used to gate out the interrupt request signal as well as to hold off data transmission while it is low. When the transmit enable signal is returned to the "1" (enabled) state, the transmitter waits for new data to be loaded into the output register (OUTBUF) before starting transmission. This means that the transmit enable line cannot be used to turn the transmitter on and off in the middle of a byte since the remainder of the byte would never be transmitted.

#### 2.2.5 Initialize Pulse

The initialize pulse resets the counter to zero and opens the host power relay contacts. It also clears the registers in the DRV-11, thus clearing the transmit enable signal.

#### 2.2.6 Load Pulse

The load pulse resets the counter and holds the TYHB line low for the duration of the load pulse (nominally 300 nano-seconds). If it is the first load pulse after the transmit enable line has been raised (=1), it also clears the hold-off flip-flop. The hold-off flip flop prevents handshaking from occurring until the first load pulse after the transmit enable line goes high.

2.2.7 Interrupt Request

A transmit interrupt can occur only after the last data bit has been received by the IMP and both of the following conditions have been met.

XMT enable is set (=1) Bit Ø in DRCSR XMT interrupt enable is set (=1) Bit 6 in DRCSR

If one wishes only to poll the interface, only the XMT enable needs to be set. Bit 7 of the status register (DRCSR) indicates the state of the INT A line. If an interrupt has been requested, bit 7 will be a one. If bit 6 is also set, an interrupt will actually occur.

ł

9

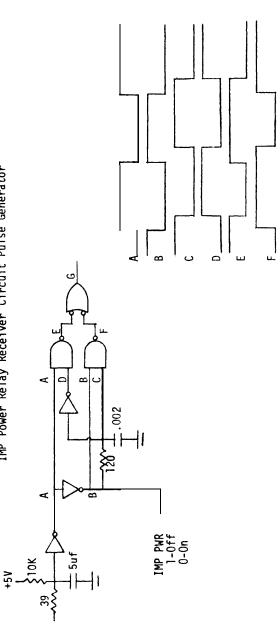

The receive section supplies one byte of data along with control information. The receiver is divided into two parts. One part senses the status of the IMP power relay contacts and the otner part performs the handshaking and serial to parallel conversion.

#### 3.1 IMP Power Sensing

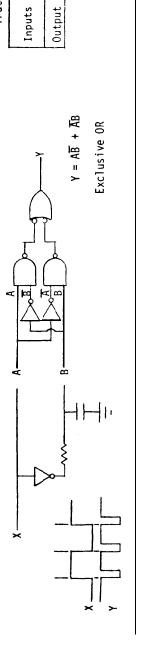

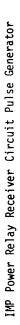

The IMP power relay contacts ground the filtered input to the inverter. The 39 ohm resistor, 5 microfarad capacitor the 10K resistor provide some debouncing of the relay and contacts. This supplies a signal through the inverters directly to the DRV-11 (bit 12). The high to low and low to high transitons generate a pulse via the EXCLUSIVE-OR gate and time delay which sets the power interrupt flip flop. See figure 4 illustrating the EXCLUSIVE-OH pulse generator. An interrupt request is generated if the receive enable bit set in the DRCSR (bit 1). An interrupt will actually is occur if bit 5 is also set. These actions will occur independent of actions in the data section of the receiver. Bit 14 (=1) indicates that the interrupt was initiated by the INP power relay (IMP recently down) and bit 12 indicates the current status of the IMP relay.

#### 3.2 Data Section

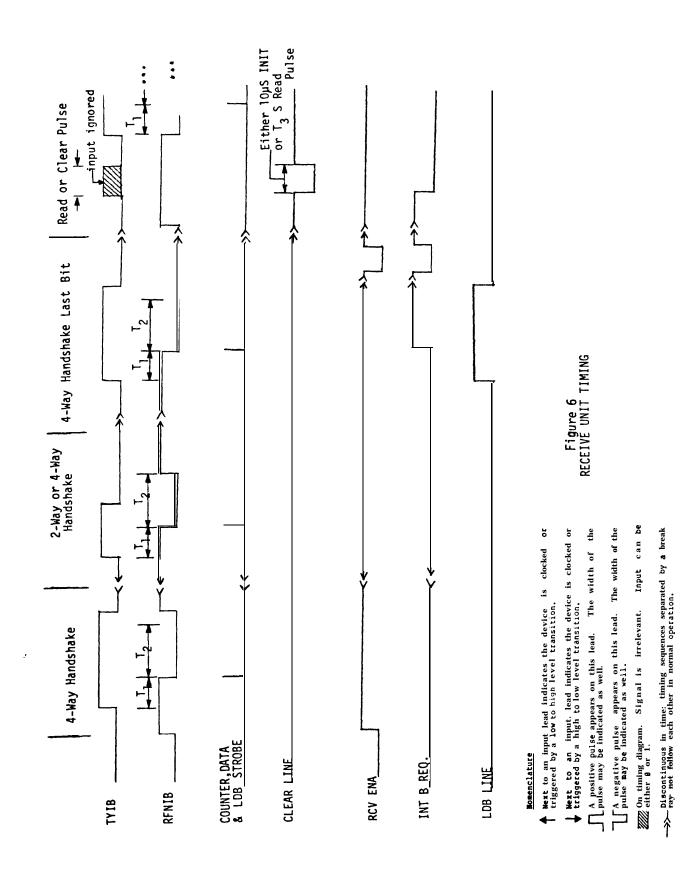

The data path in this section is from the line receiver directly to the serial-in, parallel-out shirt register (74164). The data is strobed into the shift register Tl sec. after the TYIB signal is asserted (=1). The time delay TI allows deskewing of the signals on the TYIB line and the This time delay can be varied by data and LDB lines. changing the timing capacitor. After the data is strobed into the register, the RFNIB line is dropped  $(=\emptyset)$ . It is held down for a minimum period of T2 sec. and possibly longer if the TYIB line has not dropped when T2 has elapsed. The RFNIB line will not go high again until the TYIB line is dropped. This meets the requirement of the 4-way handshaking procedure. The perioa T2 occuring after tile data is strobed into the register is to meet the minimum pulse width requirements when using the 2-Way handshaking procedure on long cables. The pulse width requirement at the IMP end of the cable can also be met by changing the appropriate timing capacitor on the interface card.

#### 3.2.1 Interrupt Requests

An interrupt request can be generated only if the Receive enable line is high (DRCSR bit 1 is 1) and one of the following is true:

- a) 8 bits have been received since the last interrupt as counted by the 74193 counter.

- b) The Last Data Bit (LDB) flip flop has been set by receipt of an LDB signal.

- c) The power status flip flop has been set due to a change in the status of the IMP power relay contacts. (Connecting and disconnecting the cable will have the same effect.)

#### 3.2.2 Initialize and Read Pulses

Both the read and the initialize pulses produce a pulse on the clear line in the interface. The initialize pulse is inverted and fed directly to the clear line. The trailing edge of the read pulse indicates that the data has been read from the register. The pulse generator T3 generates a 1 microsecond pulse AFTER the trailing edge of the read pulse. When the clear line is lowered (= $\emptyset$ ), the register, flip-flops, and counter are cleared. T2 pulse generation is inhibited and the TYIB input signal is held low for the duration of a clear pulse.

#### 3.2.3 Bit 15 Output

Bit 15 is the OR value of bit 14 (IMP recently down) and bit 11, the LIDB bit in the receive register. It is "1" only if the last bit of a packet has been received (the only time the LIDB line is asserted) or the the IMP has lost and/or regained power (its relay contacts changed position).

#### 3.2.4 Data

The data bits appear in the low order byte of the receive register (bits  $\emptyset$ -7). The most significant bit (MSB) or bit 7 is the first bit received from the line and the least significant bit (LSB) or bit  $\emptyset$  is most recently received bit.

#### 3.2.5 Bit Count

The three bits  $(8,9,1\emptyset)$  indicate how many bits have been received since the last interrupt. If a number other than  $\emptyset$ appears in these three bits, a full byte has not been received. The bits are a binary number indicating how many bits have been shifted into the register. The data bits are shifted into the low order byte starting at bit 0 and moving toward bit 7. Thus, the MSB starts at bit 0 and moves toward bit 7, its final destination. If the bit positions were numbered 1 to 8 (LSB to MSB) instead of 0 to 7, then the bit count (10,9,8) is the position of the MSB. 000 means the MSB has reached its final destination.

#### 3.2.6 Receiver Timing

•

-

•

-

See the timing diagrams for the receiver in figure 6.

Exclusive OR Pulse Generator (on level transitions)

0 -

- 0

----0

0 ~

**Truth Table**

Figure 4 - EXCLUSIVE-OR Pulse Generator

5

Figure 5 - Receive Logic

This section provides details on the power wiring for the board and data on the line drivers and receivers.

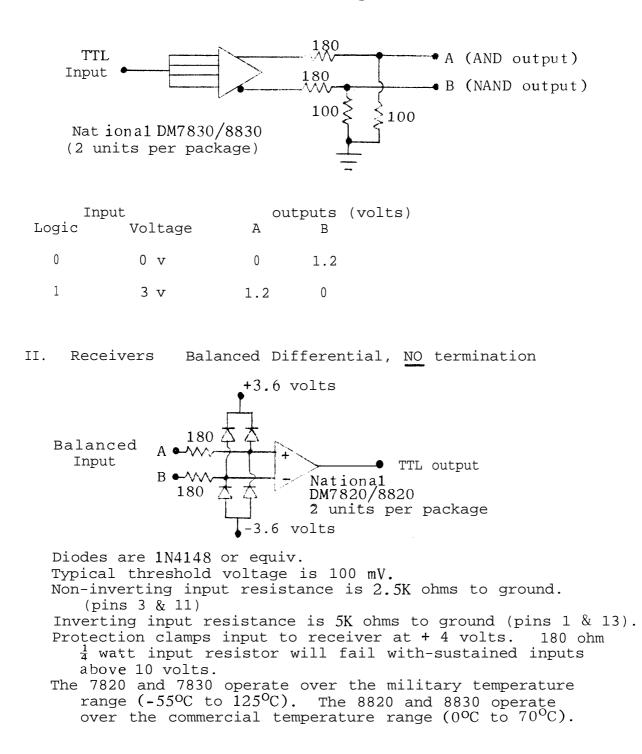

4.1 Line Drivers and Receivers (DM 8820 and DM 8830)

The line drivers are National DM 7830/8830 differential balanced drivers. The receivers are National DM 7820/8820differential balanced receivers. Connection details are shown in the figure showing drivers and receivers. The receivers provide a high impedence (2.5K or 5K) termination of the line, with protective clamping at + and - 4 volts with respect to ground. When an input is out of the + or -4 volt range, the input impedence from the out of range input to ground is 180 ohms. The maximum input voltage for any input lead should be held to + or - 10 volts with respect to ground. This is the dissipation limit of the protection circuit.

The outputs are balanced differential and provide a 1.2 volt differential voltage swing with a +.6 volt common mode voltage (both measured open circuit).

4.0

The output impedence is 130 ohms differential balanced with respect to ground (or 65 ohms to ground from each side).

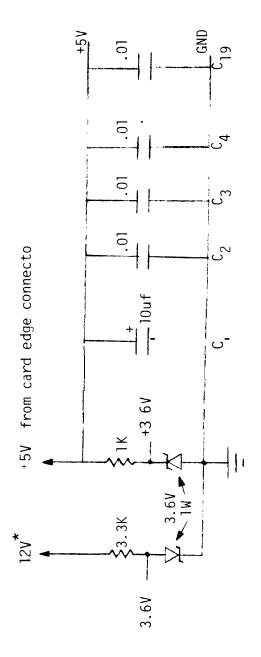

4.2 Power Distribution

The power distribution is shown in figure 8.

16

Figure 7

Line Drivers & Receivers Electrical Specifications

I. Drivers: Differential Balanced Drivers (130 ohms balanced, 65 ohms each side to ground)

\* If -12V is not available, leave resistor unterminated. The Zener will still protect against negative transients

Figure 8 POWER DISTRIBUTION

ł

1

5.0

The value of the time delays is linearly proportional to the value of the timing capacitor over reasonable values of time delay. Thus to change the time delays, the timing capacitors should be changed accordingly. All time delays shown are set to one microsecond.

#### Connectors

The I/O interface card makes 4 connections to the outside world.

a) Edge connector on the card. DEC double height board. +5 volts and ground are used. Current consumption is about 600 mA.

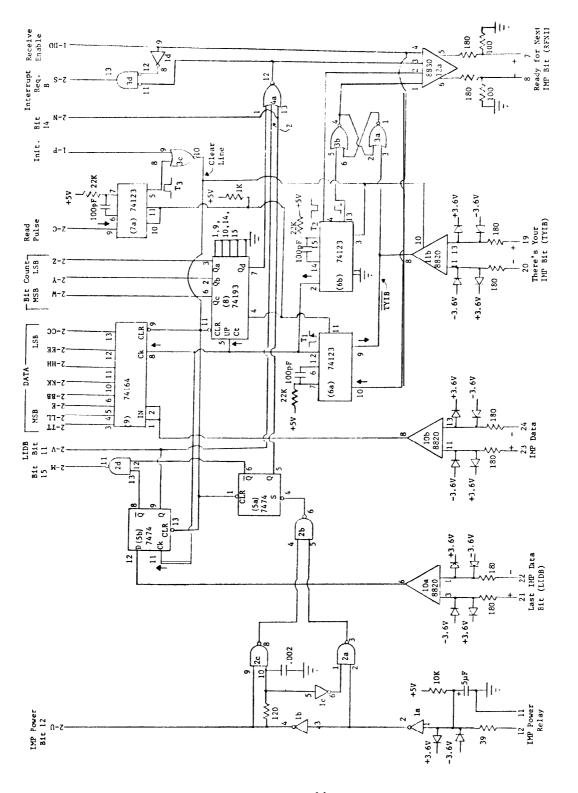

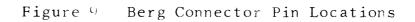

b) Berg 40 pin connectors (2), one for input and one for output to parallel interface. They are labeled J1 and J2 corresponding to DEC nomenclature. (Pin numbers at the top of the schematics indicate the connector number and pin number. Connector 2, pin VV is 2-VV.) The connector number is DEC H-856

c) Amphenol 31 pin female bayonet connector. This is specified by the BBN 1822 report. The pin numbers for this connector are on the bottom of the schematics along with the signal name. The connector is Amphenol number 48-10R-18-31S.

6.0

| 6.1       | Loopback T  | est Connector |

|-----------|-------------|---------------|

| Originate | Destination | Signal        |

| Pin No.   | Pin No.     | Name          |

| 1         | 21          | + LDB         |

| 2         | 22          | - LDB         |

| 3         | 23          | + Data        |

| 4         | 24          | - Data        |

| 5         | 19          | + TYB         |

| 6         | <b>20</b>   | - TYB         |

| 7         | 17          | + RFNB        |

| 8         | 18          | - RFNB        |

| 11        | 13          | Power Relay   |

| 12        | 14          | Power Relay   |

J1 or J2 Connector Pin Locations

.

•

The programmer has 3 registers to deal with in programming the interface: the status register, the input buffer, and output buffer.

- |

#### 7.1 Status Register

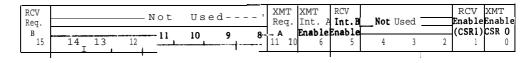

This register has 4 read/write enable bits, and 2 read only status bits. There are two enable bits, one each to allow operation of the transmitter and receiver. The two status bits indicate whether a receive interrupt request has occurred. An interrupt request can occur only if the respective transmitter or receiver has been enabled. An interrupt will actually occur if the appropriate interrupt enable bit (one for receive & one for transmit) has also been set.

#### 7.2 Input and Output Buffers

Both the input and output buffers are divided into a data section (bits 0:7) and a control section (bits 8:15). The user should not write into the transmit register or read from the receive register if they are in the process of transmitting or receiving a byte of data. Reading or writing into a register while it is in the process of transferring a byte may cause some bits to become lost and/or out of synchronization. This can be avoided by waiting until either an interrupt or interrupt request (as seen in the status register) is present before accessing the register.

7.3 Transmit (Output) Register

One byte of data will be transmitted each time this register is loaded if the transmit enable bit is set. Any old data will be cleared upon loading, independent of the state of transmit enable.

- 7.3.1 Data Section (Bits Ø:7) Bit 0 is least significant bit. Bit 7 is the most significant bit and is the first bit to be transmitted.

- 7.3.2 Control Section

Bit 11 (LHDB) - If this bit is set, the last host data bit line will go high during the transmission of the last data bit in the byte (bit 0).

Bit 12 - Host Power Relay Set- If this bit is set, the host power relay contacts will be closed indicating host is up. This bit need be set only once since the interface will latch the value. Either an initialize pulse or setting bit 13 will clear the latch. The latch will remain in the last state to which it was set. Bit 13 of the receive register contains the status of the latch.

Although the power latch can be set any time, it is recommended that the relay be turned on before the transmit enable bit is set in the status register. This prevents a data byte from being transmitted when the relay is turned on. It is important because the host must wait until the contacts have solidly closed before transmitting data which is approximately 1 mS for the relay used.

Bit 13 - Host power relay clear - Setting this bit clears the HOST power relay.

#### 7.4.0 Receive Register

Reading the receive register clears the receive buffer making it ready for another byte. Thus program testing of control bits should be done after the contents of the receive register have been moved elsewhere. If the receiver wishes to suspend receipt of more data he can:

- a) Not read the receive register.

- b) Clear recieve enable after a receive interrupt and then read the receive buffer. In this case he has access to all data accepted by the interface and blocked data at the entry point to the interface.

- c) Clear receive enable without waiting for an interrupt. In this case some bits may be lost. Setting receive enable will start the receiver again, but not necessarily where it left off.

- 7.4.1 Data (Bits 0:7)

Bit 0 is LSB and the last one received from the line. Bit 7 is MSB and the first one received from the line.

7.4.2 Control

Bits 8,9,10 - Point to last bit received in byte.

- Bit 11 (=1) Indicates last data bit line was asserted concurrently with receipt of the last data bit.

- Bit 12 IMP Power status. Indicates current status of the IMP power relay.

- Bit 13 Host power relay status. 0 ON 1 OFF

- Bit 14 Indicates the IMP has been down since the last interrupt was serviced. (i.e. the interrupt was generated by IMP changing status.) (see bit 12 for current status)

- Bit 15 Either bit 11 or 14 is a 1. This bit being set indicates the current interrupt requires special handling either because it is the last byte of a packet, or the IMP has been down.

Programming the 1822 Interface (with the DRV-11 or DR11-C)

The bus address and interrupt vector locations shown are for the first DR11-C (DRV-11) in a system. If there is more than one DR11-C, or other devices competing for the same address area, the proper numbers may not be the ones shown. Check the appropriate system documentation and/or the hardware address jumpers on the DR11-C to be sure.

Control and Status Register - DRCSR 167770

Transmit Register - OUTBUF 167772

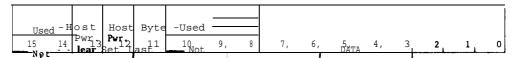

| 1 I V 14 | IMP<br>vas | NO<br>Host          |                   | Last<br>Byte | Bi<br>Cou |   |   |   |   |   | DATA |   |   |   |   |

|----------|------------|---------------------|-------------------|--------------|-----------|---|---|---|---|---|------|---|---|---|---|

| 15       | dowr<br>14 | 1 <b>Pwr.</b><br>13 | <b>Pwr.</b><br>12 | 11           | 10        | 9 | 8 | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

Receive Register - INBUF 167774

Bit Function

- Bit 15- This bit indicates that the DRV-11 has received a request from the interface to generate an interrupt. If bit 5 of this register is set, an interrupt will occur. This bit is read only.

- Bit 14-8 NOT USED

- Bit 7 This bit indicates that the DRV-11 has received a request from the interface to generate a transmit interrupt. If bit 6 of the interface is set, an interrupt will occur. This bit is read only.

- Bit 6 **Transmit interrupt ENABLE-** Setting this bit allows interrupts to be generated upon completion of transmission of each byte of data. This bit is read/write.

- Bit 5 Receive interrupt ENABLE- Setting this bit allows interrupts to be generated upon receipt of each byte of data and/or a change in the status of the IMP power bit in the interface. This bit is read/write.

- Bits 4-2 NOT USED

- Bit 1 Receive enable- Setting this bit enables the receiver (by allowing the RFNB line to go high). The interface will then receive bits until either it is full, or it receives the last data bit (LDB) signal. At this point the interface stops and requests an interrupt. It will not accept any new bits until the present load of bits is read from INBUF. This bit is read/write.

- Bit 0 Transmit enable-Setting this bit enables the transmitter (by allowing the TYB line to go high). The interface will transmit all bits which are loaded into OUTBUF after this bit is enabled. This bit is read/write.

#### Transmit Register OUTBUF 167772

All bits are read/write. Transmission of a byte is initiated each time OUTBUF is loaded, the transmitter is enabled (bit 0 of DRCSR is set).

- Bit Function

- 15-14 Not used

- 13 Setting this bit releases the Host relay contacts. This bit need be set only once, as the interface holds the information in a latch. Either bit 13 OR bit 12 should be set. NOT BOTH.

- Host Power Set- This bit sets the Host relay contacts. As with bit 13, this bit need be set only once, since the interface holds the information in a latch. Either bit 13 or bit 12 should be set. NOT BOTH. No data should be sent until at least 1 millisecond after this bit is set to allow for relay contact bounce.

- 11 Last Data Byte- This bit causes the last data bit (LDB) line to go high concurrently with the transmission of the last bit of the byte. This is typically set with the last byte of a packet.

- 10,9,8 NOT USED (On the early unit, these bits indicated the last bit position to be transmitted within the byte.)

- 7-0 DATA (Bit 7 is the high order byte, and bit Ø is the low order byte.)

#### Receive Register INBUF 167774

The interface will receive bits until either it is full, or it receives the last IMP data bit (LIDB) signal. At this point the interface stops and requests an interrupt. It will not accept any new bits until the present load of bits is read from INBUF.

- FUNCTION BIT

- Special conditon If set, the byte of data  $j_{ust}$  received requires special handling. (i.e. it is either the last byte of a packet, or there has been a change in the status of the IMP relay 15 contacts (IMP recently down).

- 14 IMP just went down or IMP has been down and just came up

0 - No change in IMP status

1 - IMP has been down recently

(see bit 12 for current status).

- 13 HOST POWER- Indicates the current status of the Host power relay as set or cleared by either bit 12 or 13 respectively in the transmit register OUTBUF. This bit should be interpreted as follows: 0 - HOST power relay contacts closed ( ON )

1 - HOST power relay contacts open ( OFF )

- IMP POWER- Indicates the current status of the IMP power relay. 12 The bit should be interpreted as follows: 0 - IMP power ON 1 - IMP power OFF (See bit 14 to determine if the interrupt was generated by the power circuit.)

- 11 LAST BYTE - If this bit is set, the data byte is the last one in a packet. Bits 8,9,10 should be checked to determine the position within the byte of the last bit transmitted.

- 10.9.8 Bit Count - The three bits (10,9,8) indicate how many bits have been received since the last interrupt. If a number other than  $\emptyset$  appears in these three bits, a full byte has not been received. The bits are a binary number indicating how many bits have been shifted into the register. The data bits are shifted into the low order byte starting at bit  $\emptyset$  and moving toward bit 7, its final destination. If the bit positions were numbered 1 to 8 (LSB to MSB) instead of 0 to 7, then the bit count (10,9,8) is the position of the MSB. 000 means the MSB has reached its final destination (position 8).

- DATA Bit 7 is the MSB of the data byte and is the first bit of the byte to be received from the IMP. 7-0

#### INTERRUPT VECTORS FOR THE INTERFACE

Transmit Interrupt Vector Loc. Contents 300 XMT = (PC)302 200 = (PS) Receive Interrupt vector Loc. Contents 304 RCV = (PC)200 = (PS) 306

XMT- Address of transmit interrupt routine RCV- Address of receive interrupt routine

#### Diagnostics

It is assumed that the DRll-C or DRV-11 is functional before these tests are attempted. If the above is not true, the programmer/user has no means of accessing the special I/O card. If in doubt, the DRll-C tests should be run first.

- 8.1 Packet Source/Sink

- 8.2 Scope Loop

#### 8.1 Packet Source Sink Program

#### 8.1.1 General

The packet source and sink program can be used to make the interface do handshaking for hardware and software checkout purposes.

The transmit part continuously loads the contents of 16 sequential memory locations into the transmit buffer. The low order byte is transmitted as data. Bit 11 of the high order byte may be set both as an end of packet indicator and also to test the LDB lines in the interface.

The receive or sink program circularly fills a 16 word area in memory with the contents of the receive register. The user may stop the program at any time to see the contents of the last 16 bytes received.

8.0

#### 8.1.2 Running Source/Sink Program

A) Location 602 determines what the program does. It is loaded into the control and status register of the interface. It should be loaded with one of the following.

101 Transmit Only

42 Receive Only

143 Transmit & Receive

- B) Locations 440 to 476 (octal) contain the transmit buffer. They should be filled with the data and control as the user wishes. Words from the buffer are successively loaded into the output buffer of the interface.

- C) Load the program into memory using ODT or switch register. Alternately assemble the listing and load it from some storage device.

- D) The program starts at location 600 (octal) after it is loaded.

8.1.3

| Memory                     | Contents                  | Function                                                         |

|----------------------------|---------------------------|------------------------------------------------------------------|

| locatio<br>(octal)         |                           |                                                                  |

| 300<br>302<br>304<br>306   | 1000<br>200<br>700<br>200 | \<br>I- Interrupt Vectors<br> <br>/                              |

| 400<br>1<br>436            |                           | \<br> - Receive Buffer 16 words (8 received<br>I bytes)<br>/     |

| 44Q<br> <br>476            |                           | \<br>I- Transmit Buffer 16 words (8 transmitted<br>I bytes)<br>/ |

| 600<br>602<br>604          | 12737<br>see table        | MOV C(loc 602),DRCSR<br>101-Transmit 42-Receive 143-Both         |

| 606                        | 167770<br>127615          | R5=44Ø                                                           |

| 610<br>612                 | 440<br>12704              | $R4 = 4 \emptyset \emptyset$                                     |

| 614<br>616<br>620          | 400<br>12706<br>2000      | R6=2ØØØ                                                          |

| 620<br>622<br>624          | 2000<br>12537<br>167772   | MOV (R5)+,OUTBUF Start transmitter                               |

| 626                        | 167772<br>777             | BR 626 Wait loop                                                 |

| 7 <b>00</b><br>702         | 13724<br>167774           | MOV INBUF, (R4) +                                                |

| 704<br>706                 | 22704<br>440              | COMP #440,R4                                                     |

| 700<br>710<br>712<br>714   | 1ØØ2<br>12704<br>400      | BNE 716<br>R4=400                                                |

| 716                        | 2                         | RTI                                                              |

| 1000<br>1002               | 12537<br>167772           | MOV (R5)+,OUTBUF                                                 |

| 1004<br>1006               | 22705<br>500              | COMP #500,R5                                                     |

| 1010<br>1012<br>1014       | 1002<br>12705<br>440      | BNE 1016<br>R5=44Ø                                               |

| 1014                       | 2                         | RTI                                                              |

| 16777Q<br>167772<br>167774 |                           | DRCSR<br>OUTBUF<br>INBUF                                         |

8.2.1 Running Scope Loop Program

- A) Load Source/Sink program in 8.1.3.

- B) Location 602 should be 143 (transmit & receive)

- C) Locations 440 to 446 should be:

| 440 | 000000 |

|-----|--------|

| 442 | 000002 |

| 444 | 000200 |

| 446 | 004001 |

8.2

- D) Change contents of location 1006 from 500 to 450 so transmitter loops after 4 bytes.

- E) Start program at location 600 (octal).

Using Scope Loop

The loop program transmits two word packets. They are transmitted continuously. They are:

Word 1 000002 octal

8.2.2

Word 2 100001 octal

The most significant bit (MSB) of each word is transmitted first. Thus, the bytes are sent as follows:

| Memory<br>Location | Byte | Oct<br>MSB | al<br>LSB | Binary<br>MSB LSB |      |                       |  |

|--------------------|------|------------|-----------|-------------------|------|-----------------------|--|

| LOCALION           | NO.  | мэр        | дел       | Мар               | ДСЦ  |                       |  |

| 440                | 1    | 000        |           |                   | 0000 |                       |  |

| 442                | 2    | 002        |           |                   | 0010 |                       |  |

| 444                | 3    | 200        |           | 1000              | 0000 |                       |  |

| 446                | 4    | 001        |           | 0000              | 0001 | asserted<br>3 of byte |  |

The last host data bit (LHDB) line is asserted with the last bit (LSB) of the second word.

33

#### Appendix

•

•

-

-

-

•

| А | DR11-C Specifications                           | 35 |

|---|-------------------------------------------------|----|

|   | (from DEC Peripherals and Interfacing Handbook) |    |

| В | Parts list for Interface                        | 40 |

# **GENERAL DEVICE INTERFACE, DR11-C**

# DESCRIPTION

The DR11-C is a general-purpose interface between the PDP-11 UNIBUS and a user's peripheral. The DR11-C provides the logic and buffer register necessary for program-controlled parallel transfers of 16-bit data between a PDP-11 System and an external device. The interface also includes status and control bits that may be controlled by either the program or the external device for command, monitoring, and interrupt functions.

The DR11-C interface consists of three functional sections: address selection logic, interrupt control logic, and device interface logic. The address selection logic determines if the interface has been selected for use, which register is to be used, if a word or byte operation is to be performed, and what type of transfer (input or output) is to be performed.

The interrupt control logic permits the interface to gain bus control and perform program interrupts to specific vector addresses. The interrupt enable bits are under program control; the interrupt bits are under control of the user's device.

The DR11-C interface logic consists of three registers: control and status, input buffer, and output buffer. Operation is initialized under program control by addressing the DR11-C to specify the register and the type of operation to be performed.

If an output operation is specified, information from the UNIBUS is stored in a 16-bit register. Once this register has been loaded under program control (e.g., MOV RO, OUTBUF), the outputs are available to the device until the register is loaded with new data from the bus. The register can also be read onto the bus. Upon transfer of data to the buffer register, a NEW DATA READY control signal is supplied to indicate to the user's decice that data has been loaded by means of a DATO or DATOB bus cycle and is read by means of a DATI or DATIP bus cycle. When an input operation is specified, the DR11-C provides 16 lines of input to UNIBUS transmitters. This permits data from the user's device to be read onto the bus. A control signal, DATA TRANSMITTED, informs the device that the input lines have been read. The input lines, which are not buffered, can be read by a DATI bus cycle (e.g., MOV INBUF, RO).

The control and status register provides six bits that can be used to control and monitor user functions. Two of these bits are interrupt enable (INT ENB) bits under control of the program. Two bits (REQ A and B) are under direct control of the user's device and can only be read by the program. These bits can be used either to initiate interrupt requests or to provide flags that can be monitored by the program. The remaining two bits (CSR0 and OSR1) are read/write bits that can be controlled by the program to provide command or monitoring functions. In the main-

| DR11-C | ferring to these addresses must also be modified accordingly if the jumpers are changed.<br>Control and Status Register (DRCSR) 767 770<br>The control and status register is used to enable interrupt logic and to provide user-defined command and status functions for the external device.                                                                                                                                                    | Two REQUEST bits, which are under device control, may be used to provide device status indications, or may be used to initiate interrupts when used with associated INT ENB (interrupt enable) bits which are under program control. Two other bits (CSRO and CSR1) are controlled from the UNIBUS and serve as command bits. | Although the REQUEST and CSR bits can be used for any function the user desires, standard PDP-11 interface conventions attempt to allocate bit 15 for error conditions and bit 7 for ready indications and both of these bits can generate interrupt requests. In addition, bit 0 is normally used for start or go commands.<br>DRCSR Bit Assignments                                                                                                     | BIT NAME FUNCTION | 15 REQUEST B This bit is under control of the user's device and<br>may be used to initiate an interrupt sequence or<br>to generate a flag that may be tested by the pro-<br>gram. When used as an interrupt request, it is set by the<br>external device and initiates an interrupt provided<br>the INT ENB B bit (bit 05) is also set.                                                                                                                                                                                                                                     | When used as a flag, this bit can be read by the program to monitor external device status.                                                    | When the maintenance cable is used, the state of<br>this bit is dependent on the state of CSR1 (bit<br>01). This permits checking interface operation by<br>loading a 0 or 1 into CSR1 and then verifying that<br>REQUEST B is the same value. | Read-only bit. Cleared by INIT when in Mainte-<br>nance Mode. | 07 <b>REQUEST A</b> Performs the same function as REQUEST B (bit<br>15) except <b>that</b> an interrupt is generated only if<br>INT ENB A (bit 06) is also set. | When the maintenance cable is used, the state of REQUEST A is identical to that of CSRO (bit 00). Read-only bit. Cleared by INIT when in Maintenance Mode. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DR11-C | tenance mode, they are also used to check operation of the interface.<br>A maintenance cable, which is supplied with the interface, permits<br>checking of the DR11-C logic by loading the input buffer from the output<br>buffer rather than from the user's device. Thus, a word from the bus is<br>loaded into the output register and the same word appears when reading<br>the input buffer, provided the interface is functioning properly. | The DR11-C can also be used as an interprocessor buffer (IPB) to allow<br>two PDP-11 processors to transfer data between each other. In this case,<br>one DR11-C is connected to each processor bus and the two DR11-Cs<br>are cabled together, thereby permitting the two processors to communi-<br>cate.                    | <b>Physical Description</b><br>The DR11-C interface is packaged on a single quad module that can be<br>plugged into a small peripheral slot (SPC).<br>The module has two Berg connectors for all user input/output signals.<br>Two M971 connector boards, which are not supplied with each interface,<br>can be used to bring all input/output lines to individual pins on a back<br>pouned via two H866 cables. Note that this cable is a "mirror image" |                   | The following accessories are available for interfacing:<br><b>a. BCO3R</b> (Berg-to-Berg) flat cable. Available in lengths of 1, 6, 8, 10,<br>12, 20, and 25 feet. When ordering, the dash number indicates the<br>desired cable length; e.g., BCO3R-1 or BCO3R-25.<br><b>b.</b> M971 connector board. A single-height by <b>8-1/2</b> in. board that brings<br>the signals from one Berg connector to the module fingers.<br><b>c. BC11K-25</b> cable. Consists of <b>a</b> 20 twisted-pair cable with a Berg con-<br>nector on one end only Available in 75 ft lenorths. | d. H856 But off connector. Includes an H856 Berg connector and 40 pins.<br>Crimping tools are available from: Berg Electronics, Inc., New Cum- | Defension     Defension       15     M       757700     B       15     M       757700     B                                                                                                                                                    | DAOUTBUE É OUTPUT DATA BUFFER                                 | 15 DR.NBUF<br>2677.14 INPUT DATA BJFFER                                                                                                                         | The register addresses can be changed by altering the jumpers on the address selection logic. However, any arograms or other software re-                  |

.

¢

4-202

4-203

| DR11-C | Input Buffer Register (DRINBUF) 767 774<br>The input buffer is a 16-bit read-only register that receives data from the<br>user's device for transmission to the UNIBUS. Information to be read is<br>provided by the user's device on the data IN signal lines. Because the<br>input buffer consists of gating logic rather than a flip-flop register, the<br>data IN lines must be held until read onto the bus. The register is read | by a DATI sequence and the data is transmitted on the UNIBUS for<br>transfer to the processor or some other device. When the input lines are<br>read during a DATI sequence, a pulsed signal (DATA TRANSMITTED) is<br>sent to the user's device to inform it that the transfer has been com-<br>pleted. The trailing edge of the positive-going pulse indicates that this<br>transfer is completed, | Whenever the maintenance cable is used, the input buffer register re-<br>ceives data from the output buffer register rather than from the user's<br>device. This permits checking of the interface logic by loading a word<br>from the bus into the output register and verifying that the same word<br>appears in the input buffer.<br>Input and Output Signals | outputs                                                                                           | Pin Signal Connector Pin | TT 0UT00<br>LLL 0UT01<br>H 0UT02<br>BB 0UT03<br>KK 0UT03<br>HH 0UT04<br>HH 0UT04<br>HI 1 L 1<br>N N                                                                                                                                               | 001707<br>001708<br>001710<br>001712<br>001712<br>001713<br>001713<br>001713                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - 0 0 <del></del>                                                                                                                                                                                    | 2<br><i>w</i> ide. Width can be changed                                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | nput Buffer Register (DRINBUF) 767<br>The input buffer is a 16-bit read-only<br>user's device for transmission to the<br>provided by the user's device on the<br>nput buffer consists of gating logic<br>data IN lines must be held until read                                                                                                                                                                                         | by a DATI sequence a<br>transfer to the processor<br>read during a DATI sequence<br>sent to the user's devic<br>pleted. The trailing edg<br>transfer is completed,                                                                                                                                                                                                                                  | Whenever the maintenance<br>ceives data from the outp<br>device. This permits check<br>from the bus into the out<br>appears in the input buffer.<br>Inp                                                                                                                                                                                                          | Inputs                                                                                            | Connector                | ~~~~~                                                                                                                                                                                                                                             | 100000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - 0                                                                                                                                                                                                  | se signals, approxim                                                                                                                                                                |

| DR11-C | When set, aliows an interrupt<br>ated, provided REQUEST A<br>ad by the program (read/write                                                                                                                                                                                                                                                                                                                                             | When set, allows an interrupt<br>ated, provided REQUEST B<br>ad by the program (read/write                                                                                                                                                                                                                                                                                                          | or read (under program<br>and can be used for a<br>to the device (appears<br>cable is used, setting or<br>its checking operation of                                                                                                                                                                                                                              | bit 15 which cannot be loaded by the program.<br>Beadwrite hit fram he harded or read hy the pro- | NIT. Signal              | Performs the same functions as <b>CSR1</b> (bit 01) but iN00 appears only on Connector No. 2. When the maintenance cable is used, the state of iN02 this bit controls the state of bit 07 (REQUEST A). IN03 IN04 Read/write bit. Cleared by INIT. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | may be read at any time by REQB ng the read operation, the out-<br>tata lines.                                                                                                                       | ·                                                                                                                                                                                   |

|        | INT ENB A Interrupt enable bit. V<br>sequence to be initi<br>(bit 07) becomes set.<br>Can be loaded or rev<br>bit). Cleared by INIT.                                                                                                                                                                                                                                                                                                   | INT ENB B Interrupt enable bit.<br>sequence to be initi<br>(bit 15) becomes set.<br>Can be loaded or re.<br>bit). Cleared by INIT.                                                                                                                                                                                                                                                                  | CSR1 This bit can be loaded<br>control) from the UNIBUS<br>user-defined command<br>only on Connector No. 1).<br>When the maintenance of<br>clearing this bit causes at<br>(REQUEST B). This perm                                                                                                                                                                 | bit 15 which cannot<br>Read/write hit (ren                                                        | gram). Cleared by INIT.  | CSRO Performs the same functions as<br>appears only on Connector No. 2.<br>When the maintenance cable is u<br>this bit controls the state of bit 0<br>Read/write bit. Cleared by INIT.                                                            | Output Buffer Register (DROUTBUF) 767 772<br>The output buffer is a 16-bit read/write register that may be read or<br>loaded from the UNIBUS. Information from the bus is loaded into this<br>register under program control. At the time of loading, a pulsed signal<br>(NEW DATA READY) is generated to inform the user's device that the<br>register has been loaded. The trailing edge of the positive pulse should<br>be used to allow the data to be loaded and settle on the user's input<br>lines. Data from the buffer is transmitted to the user's device on the<br>data OUT lines by means of a DATO or DATOB bus cycle. | The contents of the output buffer register may be read at any time by means of a DATI or DATIP bus cycle. During the read operation, the output of the buffer is fed directly to the bus data lines. | Whenever the maintenance cable is used, the data from the output<br>buffer is also applied to the input buffer register. This permits checking<br>operation of the interface logic. |

|        | 06                                                                                                                                                                                                                                                                                                                                                                                                                                     | 05                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                                                                                |                                                                                                   |                          | 0 0                                                                                                                                                                                                                                               | Output<br>The ot<br>loaded<br>register<br>(NEW<br>register<br>be use<br>lines. I<br>data OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The cc<br>means<br>put of t                                                                                                                                                                          | Whene<br>buffer<br>operatic                                                                                                                                                         |

≥7

4-204

4-205

|        |                   | Connector    | 100. 2          | OPEN<br>OPEN         | DATA TRANS.<br>OPEN | IN02<br>OPEN           | INO2<br>GND     | CSRO<br>GND       | IN15<br>IN13           | IN14<br>GND                                                                                      | REQ B<br>GND        | IN12<br>IN11          | IN10<br>GND        | 1N09<br>1N08 | GND<br>IN03             | 1007<br>GND   | IN06<br>OPEN       | INO5<br>GND                     | 1004<br>1001    | GND                 |       |

|--------|-------------------|--------------|-----------------|----------------------|---------------------|------------------------|-----------------|-------------------|------------------------|--------------------------------------------------------------------------------------------------|---------------------|-----------------------|--------------------|--------------|-------------------------|---------------|--------------------|---------------------------------|-----------------|---------------------|-------|

|        | BC11K Connections | Connector    | 1.001           | OPEN<br>OPEN         | OUT00<br>OPEN       | OPEN<br>OPEN           | OPEN<br>GND     | 0UT01<br>0UT04    | GND                    | OUT05<br>OUT06                                                                                   | GND<br>0 UT07       | OUT03<br>GND          | OUT08<br>OUT09     | GND<br>OUT10 | OUT1 1<br>OUT12         | GND<br>CSR1   | GND<br>OUT13       | OUT14<br>OUT15                  | GND<br>REQ A    | GND<br>GUT02        |       |

|        |                   | 0            | 1               | ВĄ                   | <u>ں</u> ں          | шц                     | エっ              | хJ                | ≥⊾                     | ZĽ                                                                                               | ς<br>Γ              | $\supset$ >           | ≥×                 | Σ≺           | AA<br>BB                | с<br>С<br>С   | ᇤᇆ                 | Ξ⊰                              | 좆긕              | ΜN                  | 4-207 |

| 71100  |                   | Color        |                 | black<br>wh-org      | black<br>wh-yel     | black<br><b>wh-gry</b> | black<br>wh-red | black<br>wh-grn   | brown<br>green         | brown<br>red                                                                                     | black<br>wh-blu     | black<br>orange       | black<br>wh-vio    | black<br>red | brown<br>yellow         | black<br>blue | brown<br>orange    | brown<br>blue                   | black<br>yellow | brown<br>'violet    |       |

|        |                   | Twietod Dair |                 | black/white-orange   | black/white-yellow  | black/white-grey       | black/white-red | black/white-green | brown/green            | brown/ red                                                                                       | black/white-blue    | black/orange          | black/white-violet | black/ red   | brown/yellow            | black/ blue   | brown/orange       | brown/ blue                     | black/yellow    | brown/violet        |       |

| D'IINU | Pin Connections   | M971         | ú               | berg<br>Header Board | W Al<br>uu A2       |                        |                 |                   |                        |                                                                                                  | AA JI               | ~ <b>~</b> ×          |                    |              | л Р<br>Р2<br><b>7</b> 1 |               |                    | П<br>12<br>71<br>72<br>71<br>71 |                 | В <b>U1</b><br>А u2 |       |

|        |                   |              | Connector No. 1 | e Pin                | ⊲ 80 ;              | о<br>о                 | μт-             | , _               | ≥zſ                    | ы<br>2<br>2<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 |                     | ≥×≻                   |                    |              |                         |               | N M C              |                                 | F               | u u<br>DATA VV      |       |

|        |                   |              |                 | Name                 | OPEN<br>OPEN        | OUT 0C<br>OPEN<br>OPEN | OPEN<br>OPEN    | OUT01<br>OUT04    | GND<br>DUT05<br>INIT H | GND<br>GND                                                                                       | OUT03<br>GND<br>GND | OUT08<br>OUT09<br>GND | 0UT10<br>0UT10     | GND IS       | GND<br>OUT13<br>OUT14   | GND<br>GND    | GND<br>OUT02       | GND<br>OUT02                    | OPEN<br>0       |                     | 700   |

|        |                   | DR11-C       | Connector No. 2 | Name                 | OPEN<br>GND         | GND<br>GND<br>INIT H   |                 | 1001<br>1001      | GND<br>IN05<br>OPEN    | GND<br>GND                                                                                       | IN03<br>GND         | IN08<br>GND<br>GND    |                    | GND<br>REQ B | GND<br>IN13<br>N14      | GND<br>GND    | GND<br>GND<br>IN02 | OPEN<br>IN02<br>OPEN            | DATA<br>TRANS.  | OPEN                |       |

|        |                   | L            | Conne           | Pin                  | vv<br>vv            | Ss<br>RR               | A NN<br>NN      | Υ<br>Υ<br>Κ<br>Γ  | ╕ቿ₶                    |                                                                                                  | ABBC                | ∼⊀∨                   | ≥>=                | റ⊢ഗ          | ۲ ۵ ۲                   | :∑⊣2          | ៹っェ                | ᇿᆈᇊ                             | ı<br>ں د        | βA                  |       |

|        |                   | M971         | 1               | Berg<br>Header       | ABA                 | СОШ                    | μт-             |                   | ≥z⊄                    |                                                                                                  |                     | ≥×≻                   |                    |              |                         |               |                    |                                 |                 |                     |       |

|        |                   |              |                 | Board                | u 2<br><b>U1</b>    | 2 <b>7</b> 2           | 1121            | s2<br>S1          | <b>R</b> 1<br>22<br>22 | <b>1</b> 22                                                                                      | Z Z Z               | 338                   | ¥9:                | 32 <b>7</b>  | F2<br>F1                | 1925          | C                  | 81<br>81<br>82                  | AI :            | A2<br>A1            |       |

DR11-C

≥8

4-206

4-207

DR11-C

•

.

-10

•

| DR11-C | NEW DATA READY-drives 30 units, positive pulse,<br>400-ns wide unless width changed by an external ca-<br>pacitor | DATA TRANSMITTED-drives 30 unit loads, positive pulse, 400-ns wide unless width changed by an external capacitor | INIT (initialize) - common signal on both connectors driven by one 30-unit load driver | 16-bit word from the external device | 16-bit word from the UNIBUS. Either a full word or an 8-bit byte (either high or low) may be loaded from the bus. | A MAINT cable (supplied with basic system) jumpers<br>the DROUTBUF outputs to the DRINBUF inputs and | forces bits 15 and 7 to read as CSR1 and CSR0, respec-<br>tively.                                      |                                                         |                                                 |                                    |                                  |                                      |                |                                                                                      |                                          |                                 |                                  |                                                                                            |

|--------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|------------------------------------|----------------------------------|--------------------------------------|----------------|--------------------------------------------------------------------------------------|------------------------------------------|---------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|

|        | Signals:                                                                                                          |                                                                                                                  |                                                                                        | Data Inputs:                         | Data Outputs:                                                                                                     | Maintenance<br>Mode:                                                                                 |                                                                                                        |                                                         |                                                 |                                    |                                  |                                      |                |                                                                                      |                                          |                                 |                                  |                                                                                            |