# Implementing a Directory-Based Cache Consistency Protocol

Richard Simoni

Technical Report No. CSL-TR-90-423

**March 1990**

# Implementing a Directory-Based Cache Consistency Protocol

Richard Simoni

**Technical Report: CSL-TR-90-423**

March 1990

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305-4055

#### **Abstract**

Directory-based cache consistency protocols have the potential to allow shared-memory multiprocessors to scale to a large number of processors. While many variations of these coherence schemes exist in the literature, they have typically been described at a rather high level, making adequate evaluation difficult. This paper explores the implementation issues of directory-based coherency strategies by developing a design at the level of detail needed to write a memory system functional simulator with an accurate timing model.

The paper presents the design of both an invalidation coherency protocol and the associated directory/memory hardware. Support is added to prevent deadlock, handle subtle consistency situations, and implement a proper programming model of multiprocess execution. Extensions are delineated for realizing a *multiple-threaded* directory that can continue to process commands while waiting for a reply from a cache. The final hardware design is evaluated in the context of the number of parts required for implementation.

<u>Kev Words and Phrases</u>: Directory-based cache consistency, cache coherency, scalable shared-memory multiprocessors.

Copyright © 1990

by

Richard Simoni

# **Table of Contents**

| 1. Introduction                                  | 1                                      |

|--------------------------------------------------|----------------------------------------|

| 2. System Assumptions -                          | 2                                      |

| 3. Command Messages                              | 2                                      |

| 4. Avoiding Deadlock                             | 3                                      |

| 4.1. Cache Deadlock                              | 4                                      |

| 4.2. Directory Deadlock                          | 5                                      |

| 43. Transit Ďeadlock                             | 6                                      |

| 5. Traffic Cop Problem                           | 2<br>2<br>3<br>4<br>5<br><b>6</b><br>6 |

| 5.1. Message Queueing                            |                                        |

| 5.2. Multiple Threads                            | 10                                     |

| 53. Routing                                      | 11                                     |

| <b>5.4.</b> What Causes the Traffic Cop Problem? | 11                                     |

| 6. Command Definition                            | 11                                     |

| 6.1. Replies                                     | 12                                     |

| 6.2. Subtle Cases                                | 12                                     |

| 7. Model of Parallel Execution                   | 17                                     |

| 8. Directory Controller                          | 19                                     |

| 8.1. Which Directory Organization?               | 19                                     |

| 8.2. Command Fields                              | 20                                     |

| 8.3. Datapath                                    | 21<br>23                               |

| 8.4. State Machine                               | 23<br>23                               |

| 8.4.1. Deciphering the Transition Table          | 25<br>25                               |

| 8.4.2. Transition Table Highlights               | 27                                     |

| 8.5. Implementing Multiple Threads               | 29                                     |

| 9. Dir, NB                                       |                                        |

| 10. Technology Options                           | 30                                     |

| 10.1. Directory Memory                           | 30                                     |

| 10.2. Directory Controller                       | 31                                     |

| 10.3. Queues                                     | 31                                     |

| 11. Conclusion                                   | 32                                     |

| 12. Acknowledgements                             | 32                                     |

| 13. References                                   | 33                                     |

**List of Figures**

| Figure 4-1: Deadlock situation that demonstrates why a cache must not wait for a reply to the C→MM command it has sent before processing received MM→C commands.  Figure 5-1: Overview of the traffic cop problem.  Figure 5-2: A solution to the traffic cop problem.  Figure 5-3: A modified configuration that replaces the arbiters on the inputs to the cache and directory controllers with separate input queues.  Figure 5-4: Highlighting the parts of the system with asynchronous signals.  Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the traffic cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a return data reply instead of the usual exclusive acknowledge reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a copyback command to the cache, the cache writes the block back to memory. Now when cache 1 receives the copyback command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the writeback command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.                                                        | Figure 2-1:   | The basic system. Each node consists of <b>a</b> processor (P), cache (C), main memory (MM), and interconnect controller (IC).                                                                                                                                                                                     | 2  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5-1: Overview of the traffic cop problem.  Figure 5-2: A solution to the <b>traffic</b> cop problem.  A modified configuration that replaces the arbiters on the inputs to the cache and directory controllers with separate input queues.  Figure 5-3: Highlighting the parts of the system with asynchronous signals.  Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the <b>traffic</b> cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 8-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: The format of each message in the queues.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-5: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made | Figure 4-1:   | Deadlock situation that demonstrates why a cache must not wait for a reply to the $C \rightarrow MM$ command it has sent before processing received $MM \rightarrow C$                                                                                                                                             | 5  |

| Figure 5-2: A solution to the <b>traffic</b> cop problem.  Figure 5-3: A modified configuration that replaces the arbiters on the inputs to the cache and directory controllers with separate input queues.  Figure 5-4: Highlighting the parts of the system with asynchronous signals.  Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the <b>traffic</b> cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                              | Figure 5.1.   | * *                                                                                                                                                                                                                                                                                                                | 7  |

| and directory controllers with separate input queues.  Figure 5-4: Highlighting the parts of the system with asynchronous signals.  Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the traffic cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a return data reply instead of the usual exclusive acknowledge reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache. But before the directory can issue a copyback command to the cache, the cache writes the block back to memory. Now when cache 1 receives the copyback command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the writeback command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                        |               |                                                                                                                                                                                                                                                                                                                    | Ŕ  |

| Figure 5-4: Highlighting the parts of the system with asynchronous signals.  Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the traffic cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a return data reply instead of the usual exclusive acknowledge reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a copyback command to the cache, the cache writes the block back to memory. Now when cache 1 receives the copyback command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the writeback command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                   |               | A modified configuration that replaces the arbiters on the inputs to the cache                                                                                                                                                                                                                                     | 8  |

| Figure 5-5: Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.  Figure 5-6: The solution to the <b>traffic</b> cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive</b> acknowledge reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                          | Figure 5-4    |                                                                                                                                                                                                                                                                                                                    | 9  |

| input to the directory controller for replies and commands.  Figure 5-6: The solution to the <b>traffic</b> cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                    | _             |                                                                                                                                                                                                                                                                                                                    | _  |

| Figure 5-6: The solution to the <b>traffic</b> cop problem is simpler if the system has only two resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 118010 0 01   |                                                                                                                                                                                                                                                                                                                    |    |

| resources that must communicate on each node.  Figure 6-1: The situation that occurs when two processors write a block at the same time that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a return data reply instead of the usual exclusive acknowledge reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache. But before the directory can issue a copyback command to the cache, the cache writes the block back to memory. Now when cache 1 receives the copyback command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the writeback command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 5-6:   |                                                                                                                                                                                                                                                                                                                    | 12 |

| that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\mathcal{E}$ |                                                                                                                                                                                                                                                                                                                    |    |

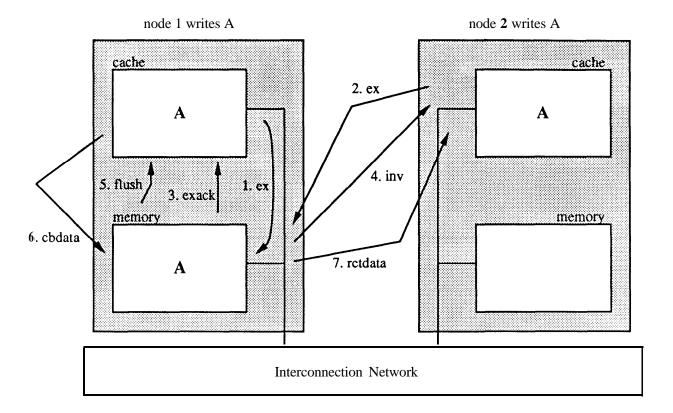

| that they both have cached. Here, node 1 gains exclusive access first. Node 2 eventually receives a <b>return data</b> reply instead of the usual <b>exclusive acknowledge</b> reply.  Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node 1's cache. But before the directory can issue a <b>copyback</b> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <b>copyback</b> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <b>writeback</b> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 6-1:   | The situation that occurs when two processors write a block at the same time                                                                                                                                                                                                                                       | 14 |

| Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache. But before the directory can issue a <i>copyback</i> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <i>copyback</i> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <i>writeback</i> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an <i>exclusive acknowledge</i> or <i>return data</i> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C             | that they both have cached. Here, node 1 gains exclusive access first. Node 2                                                                                                                                                                                                                                      |    |

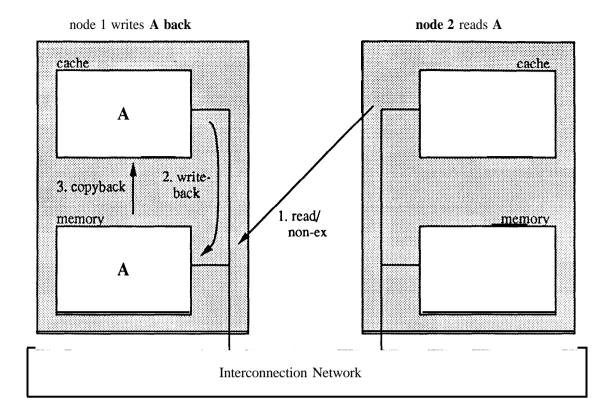

| Figure 6-2: Another tricky situation. Node 2 reads a block that is dirty in node l's cache.  But before the directory can issue a <i>copyback</i> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <i>copyback</i> command, it no longer has the block; the block is stuck in the command queue at the input to the directory.  Figure 6-3: A series of commands in the queue that demonstrate why the <i>writeback</i> command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an <i>exclusive acknowledge</i> or <i>return data</i> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                                                                                    |    |

| Figure 6-3: A series of commands in the queue that demonstrate why the writeback command must be discarded.  Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 6-2:   | Another tricky situation. Node 2 reads a block that is dirty in node I's cache. But before the directory can issue a <i>copyback</i> command to the cache, the cache writes the block back to memory. Now when cache 1 receives the <i>copyback</i> command, it no longer has the block; the block is stuck in the | 15 |

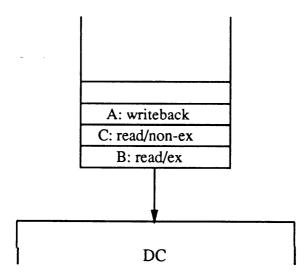

| Figure 8-1: A directory entry for the Dir, NB scheme.  Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 6-3:   | A series of commands in the queue that demonstrate why the writeback                                                                                                                                                                                                                                               | 16 |

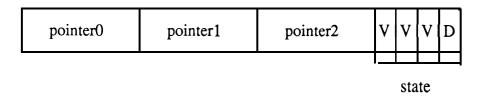

| Figure 8-2: The format of each message in the queues.  Figure 8-3: The datapath of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 8-1:   |                                                                                                                                                                                                                                                                                                                    | 20 |

| Figure 8-3: The <b>datapath</b> of the directory controller.  Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | · · ·                                                                                                                                                                                                                                                                                                              |    |

| Figure 8-4: The queued commands that will cause the problem.  Figure 8-5: The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _             |                                                                                                                                                                                                                                                                                                                    |    |

| Figure 8-5: The revised datapath includes three comparators so the determination of whether to send an exclusive acknowledge or return data reply can be made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _             |                                                                                                                                                                                                                                                                                                                    | 26 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | The revised <b>datapath</b> includes three comparators so the determination of whether to send an <b>exclusive acknowledge</b> or <b>return data</b> reply can be made                                                                                                                                             | 28 |

# **List of Tables**

| Table 3-1: | Initial version of command messages.                                                              | 4  |

|------------|---------------------------------------------------------------------------------------------------|----|

|            | Command messages and their replies.                                                               | 13 |

| Table 6-2: | Command messages revised to handle subtle cases.                                                  | 17 |

| Table 7-1: | Final version of the command messages, revised to include the wait/nowait                         | 19 |

|            | condition needed for the parallel model of execution.                                             |    |

| Table 8-1: | State transition table for the directory controller. An "x" indicates a "don't                    | 24 |

|            | care" condition, and a "*" means the field should remain unchanged from its                       |    |

|            | previous value.                                                                                   |    |

| Table 8-2: | Modifications to state transition table to handle problem occurring in <b>Dir</b> <sub>i</sub> NB | 29 |

|            | protocols.                                                                                        |    |

| Table 9-1: | Modifications to state transition table for Dir, NB scheme.                                       | 30 |

| Table 10-1 | : Parts needed to implement the datapath for the directory controller,                            | 31 |

|            | assuming 256 or fewer processors.                                                                 |    |

# Implementing a Directory-Based Cache Consistency Protocol

Richard Simoni Computer Systems Laboratory Stanford University Stanford, CA 94305

#### 1. Introduction

Directory-based cache consistency schemes have the potential to scale shared-memory multiprocessors to a large number of processors [1,4]. For this reason, we are interested in taking a closer look at the advantages and disadvantages of this class of protocols. But it is difficult to draw any certain conclusions about these schemes with only a vague notion of how they function and are implemented in a real system. The purpose of this paper is to clarify these notions by presenting a reasonably detailed design of the hardware needed to implement a directory-based cache consistency protocol.

We have chosen to approach the design at a level of detail that will allow a functional simulator with an accurate timing model to be written. Towards this end, our design shows every necessary piece of hardware in the datapath, but ignores controller details when it is apparent how one **would** go about designing the controller. In addition, we formally define the consistency protocol by identifying the states and their corresponding actions, including both messages that must be sent and state changes within the directory. The resulting "action table" could then define a simulator's functionality, while the detailed hardware specification can be used to derive an accurate timing model.

Because we would like the reader to understand our design decisions, we have chosen to not simply present the final design, but rather step the reader through the design process. We start in the next section by stating the assumptions we make about the system in which our protocol will operate. We then enumerate the types of messages required to implement consistency, and identify the conditions that must be satisfied to avoid deadlock. These conditions help us design a strategy for communication between the hardware units within a node. Once this is done, we know enough about how messages are handled in a node to further refine the message definitions to handle several subtle cases correctly. We then add the necessary support for a model of parallel execution, such as **strong ordering** or **weak ordering**. Once the protocol definition is complete, we design the directory hardware itself, including a precise definition of the contents of a directory entry, the hardware necessary to implement the directory and the messages required by the protocol, and a state transition table for the directory controller. Finally, we examine the size of the resulting hardware.

This is a revised edition of an unpublished report of July, 1988.

# 2. System Assumptions

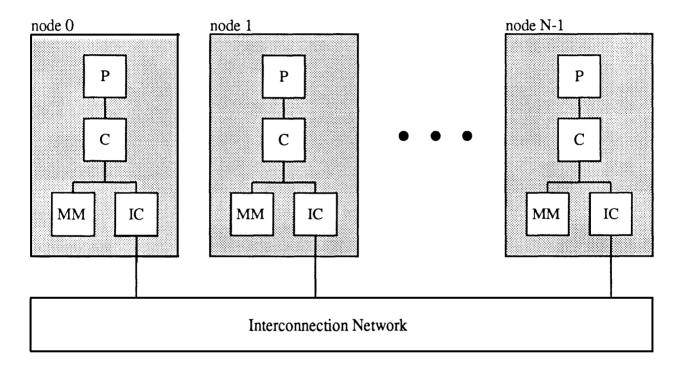

In order to have a starting point for our design, we must make some assumptions about the system for which the directory-based consistency scheme is intended. First and foremost, we assume the system is a shared-memory multiprocessor that uses a large number of high-performance **CPUs**. We assume that each processor is paired with its own cache. And finally, we assume that main memory is distributed across the processors. That is, part of the globally-shared main memory is physically local to each processor/cache pair. Therefore, the minimum latency to memory for a processor request is lower if the request is to a location that happens to be local than if the request is to a remote location. This system configuration is shown in Figure 2-1. We further assume the directory bits for each chunk of main memory are located with that chunk, i.e., the directory bits are distributed across the processor nodes along with main memory.

Figure 2-1: The basic system. Each node consists of a processor (P), cache (C), main memory (MM), and interconnect controller (IC).

A wide variety of networks satisfy our assumptions about the interconnect. We assume the network has only point-to-point capability, i.e., there is no hardware mechanism to implement broadcasts efficiently. Each message on the network is sent with a source and destination processor node number. We assume that messages between any two given nodes are delivered in the same order that they were sent. The interface at each node to the network is called the *interconnect controller* (IC). We assume it provides its node with reliable communication to and from the other nodes in the system.

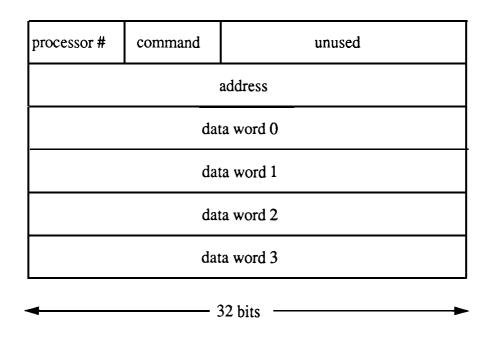

#### 3. Command Messages

The basic mechanism by which consistency is maintained in a directory-based protocol is the passing of commands in messages between the caches and the directories associated with main memory. A typical sequence

begins when the cache cannot satisfy a processor request without communicating with memory; an example is a cache miss. In this case the cache will send a command to a directory instructing it to supply the missing block. The directory may be able to do this directly, or it may need to take other action before responding, such as sending a command to another cache directing it to return its dirty copy of the block

Thus, we have two varieties of messages. The first type is cache-to-main-memory (abbreviated  $C\rightarrow MM$ ) commands, which are initiated by a cache any time it cannot immediately satisfy a processor's request. The second type is main-memory-to-cache (abbreviated  $MM\rightarrow C$ ) commands, which are issued by a directory to instruct caches to take some action before it can respond to a  $C\rightarrow MM$  command it has received.

A quick perusal of the possible cache events that can occur [1] shows that we need four different  $C\rightarrow MM$  commands:

- **readlnon-exclusive** (**readlnon-ex**). The cache issues this command on a read miss in order to get a copy of the block from main memory.

- read/exclusive (readlex). In the case of a write miss, the cache uses this command to get an exclusive copy of the block from main memory.

- exclusive (ex). When the cache encounters a write hit on a clean block, it must ask the directory for exclusive access to this block; it will then be the single cache with the dirty copy of the block.

- writeback. This command is used by the cache to write back a dirty block to main memory if, for example, it is replacing the block with another one.

As previously mentioned, a directory may need to have other caches take action when one of these  $C \rightarrow MM$  commands is received. The three  $MM \rightarrow C$  commands are as follows:

- *copyback*. This command tells the target cache to *copyback* the indicated block to main memory. The block need not be invalidated, however, This command is required when there is a read miss in a cache on a block that is dirty in another cache.

- flush. A cache receiving this command should copy the specified block back to main memory and invalidate the block. This case occurs when a cache has a dirty copy of the block and there is a write miss on the block in another cache.

- invalidate. This command should cause the receiving cache to invalidate the indicated block It is

issued when another cache requests exclusive access to a block, either through a read/ex or ex C→MM

command

These C→MM and MM→C commands are summarized in Table 3-1. Note that many of the commands require a **reply**, e.g., to return a block of data. We will modify and **refine** these commands and precisely define their replies later.

## 4. Avoiding Deadlock

There are several conditions that must be satisfied in the system to avoid the possibility of deadlock. A typical situation we must take care to avoid is one in which two nodes simultaneously send a message to each other and cannot continue until they receive a reply; neither node can reply because each is stuck waiting for a reply that will never come.

The key to avoiding these situations is to remember the worst-case sequence of transactions that can occur on a given block: a cache issues a C→MM command, and the directory has to issue multiple MM-X commands (to

#### **C**→**MM** commands

read/ex read/non-ex

writeback

MM→C commands

copyback flush invalidate

Table 3-1: Initial version of command messages.

caches other than the one that initiated the sequence) as a result; the target caches may then need to send replies back to the directory, which finally responds to the cache that issued the original request. We must ensure that there is no possibility of deadlock at each of the resources used in this worse-case scenario. In particular, we must make sure no messages become stuck (1) at a cache, (2) at a directory, and (3) in transit between a cache and a directory. We will examine each of these cases independently.

#### 4.1. Cache Deadlock

Notice that when a cache receives a MM→C command (i.e., copyback, flush, or invalidate), the cache never needs to issue another command to complete the requested action. That is, the actions required to carry out a MM→C command are self-contained in the destination cache. So the conditions sufficient to prevent deadlock at a cache degenemte to those necessary to ensure the cache eventually begins processing all commands it receives. In practice, there are only two reasons the cache might delay processing a command. First, if the CPU is accessing the cache, then the command must wait; however, the CPU will eventually complete its access, so this delay will not cause deadlock. Second, the cache may have issued an unrelated C→MM command command and awaits a reply. This situation is more dangerous.

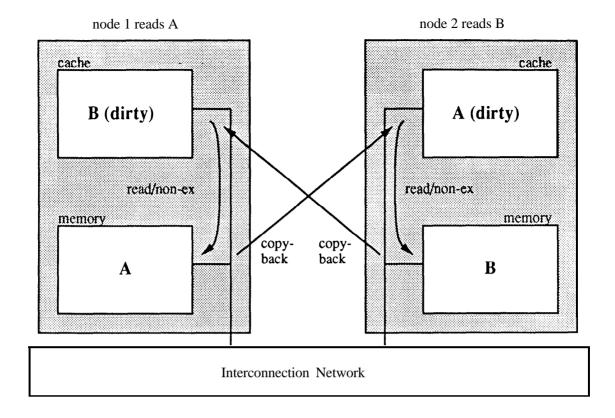

Consider an example, shown in Figure 4-1. There are two nodes, node 1 and node 2, and two data blocks, block A and block B. The directory information for blocks A and B resides in nodes 1 and 2, respectively. Block B is dirty in cache 1, and block A is dirty in cache 2. Now suppose processor 1 performs a read to block A, and at the same time, processor 2 performs a read to block B. Each cache sends an **read/non-exclusive** C $\rightarrow$ MM command to the appropriate directory and waits for the directory to return the data in a reply. Each **directory** issues a **copyback** MM $\rightarrow$ C command to the other node. But if these caches must put off the **copyback** until they receive the reply to **the read/non-exclusive** commands they sent, then they will wait forever, because neither reply can be returned by the directories until the **copyback** commands have been completed.

We can therefore state the condition that must be satisfied to prevent deadlock in the caches:

A cache controller cannot wait to process and respond to a MM→C command until after it has received

a reply from a pending C→MM request that it has issued.

Figure 4-1: Deadlock situation that demonstrates why a cache must not wait for a reply to the C→MM command it has sent before processing received MM→C commands.

## 4.2. Directory Deadlock

Referring back to the the worst-case sequence of transactions, there are two distinct processing phases a directory must deal with to fully complete a request. First, the directory must handle the  $C\rightarrow MM$  command request, which may include sending  $MM\rightarrow C$  commands to caches. Second, the directory must process the replies from those caches, which may include sending a reply to the cache that sent the original  $C\rightarrow MM$  command. Once access to the directory is gained, both of these processing phases are completed without blocking at the directory. We therefore need only ensure that all  $C\rightarrow MM$  commands and replies to  $MM\rightarrow C$  commands attain directory access.

Commands and replies from caches compete solely with each other for the directory resource. Replies from caches can always be handled immediately; however, there can be constraints on the  $C\rightarrow MM$  commands. For instance, a command for an address cannot be executed in the directory if a transaction is already pending for that address; otherwise, cache consistency will be compromised. The directory may therefore block on some  $C\rightarrow MM$  commands. It must be ensured that this blocking does not prevent replies to  $MM\rightarrow C$  commands from accessing the directory, since these replies are required to release the blocked command. We can state this condition as follows:

• A directory controller cannot delay processing replies to a MM→C command until after processing a C→MM command command that cannot be immediately processed.

#### 4.3. Transit Deadlock

Now that we have specified conditions sufficient to prevent deadlock at the cache and the directory, we need only assure that messages between them do not deadlock in transit. The route taken by a message includes both the channels of the interconnection network between nodes and the intra-node communication paths. Since the messages in the system are the only users of these communication resources, we can prevent deadlock by guaranteeing that no messages permanently block other messages. The network, for instance, must not be built so that a C $\rightarrow$ MM command holds the link between the cache and directory if this may prevent a resulting MM $\rightarrow$ C command to a different cache from reaching its destination. In our design we assume that all replies to a command require a separate transaction on the interconnection network. Not only is this assumption safe in terms of avoiding deadlock, but also consumes less network bandwidth since the network is not tied up needlessly during command processing. <sup>1</sup>

Within a node, the directory controller should either not see arriving  $MM \rightarrow C$  commands at all, or should be able to forward them to the cache regardless of the current state of the controller. Otherwise, deadlock may occur if each directory on two nodes sends a  $MM \rightarrow C$  command to the other node, for the commands may be blocked from the destination cache by the local directory. We can generalize the above concepts into a condition sufficient to prevent transit deadlock:

• The interconnection network must be non-blocking, and each hardware unit within a node cannot block messages intended for another unit in the same node.

# 5. Traffic Cop Problem

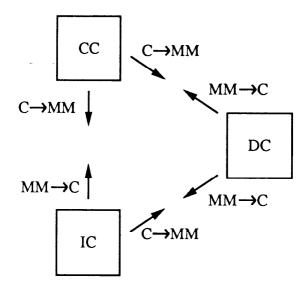

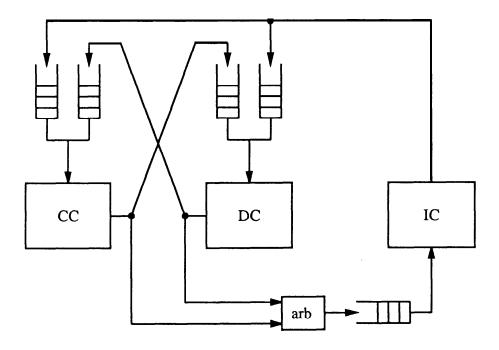

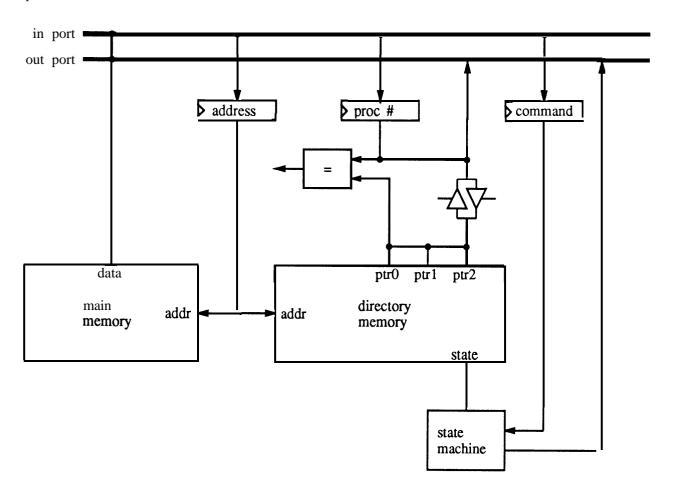

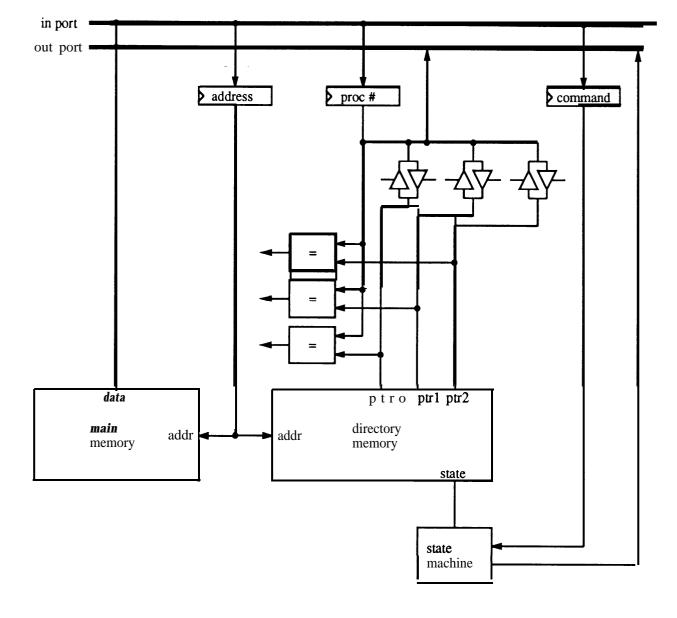

An important problem to solve is how to efficiently pass data between the major subsystems within each node. For our purposes we will consider three subsystems. The **directory controller (DC)** maintains the contents of the directory bits. The **interconnect controller (IC)** implements the interface between the node and the interconnection network. For our design we can view it abstractly as a mechanism that reliably sends and receives  $C \rightarrow MM$  and MM-42 commands. The **cache controller** (CC) maintains the internal cache directory (comprised of tags, valid bits, dirty bits, etc.) and satisfies memory requests from the processor.

Figure 5-1 shows the communication paths that must be supported within a node to transfer commands (and replies) between the controllers. The cache controller issues  $C\rightarrow MM$  commands, which may be directed to either the local directory or to a remote directory via the interconnect controller. Similarly, the  $MM\rightarrow C$  commands from the directory controller may go to the local cache or to remote caches. Finally, commands arriving at the node through the interconnect controller may go to the cache or the directory, depending on the command type  $(C\rightarrow MM \rightarrow C)$ . We call the problem of directing each of these messages to its destination efficiently **the traffic cop problem.**

<sup>&#</sup>x27;However, this assumption does result in a longer command latency since arbitration for the interconnect link must occur twice, once for the command and once for the reply. However, this additional arbitration & lay will be small compared to the total latency, and should therefore have negligible effect on the system performance.

Figure 5-1: Overview of the traffic cop problem.

#### 5.1. Message Queueing

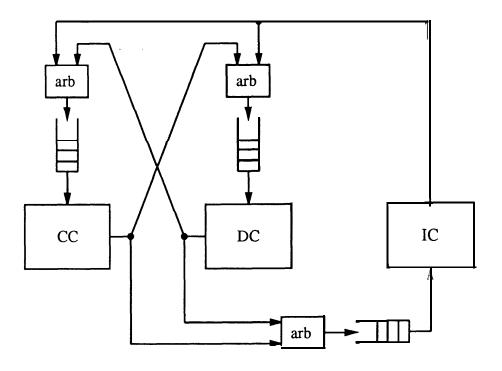

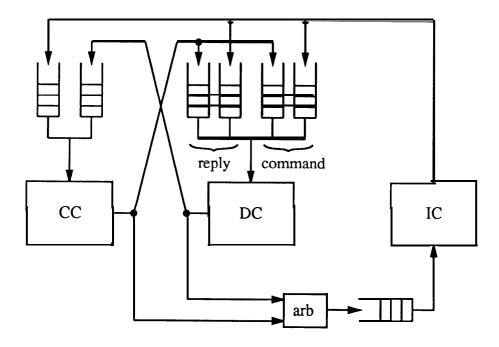

Because we do not want to halt a producing resource just because the consumer happens to be momentarily busy, we begin our design by placing a FIFO queue at the input to each of the controllers. This has additional benefits, as we will see shortly. Also notice that some sort of arbitration is needed on the input to these queues, since each queue is fed by two sources. For example, the directory controller must accept  $C \rightarrow MM$  commands from both the local cache and the interconnect controller. The resulting system is shown in Figure 5-2.

Let us further consider the arbitration on the input to the cache and the directory. Say the cache controller in a node prepares a command for the directory in the same node. It then gains access through the arbiter to the directory input queue since the interconnect controller currently has no commands for the directory. But as soon as it begins to transfer data into the queue, a C→MM command arrives at the interconnect controller. Now the interconnect controller cannot transfer the command to the directory input queue until the cache has completed moving its own command into the queue. There are several design options for the interconnect controller when this situation is encountered. The interconnect controller could abort the message, causing it to be sent again later. This is obviously not an attractive alternative since additional network traffic results from an operation that should be fairly innocuous, i.e., the transfer of data from a cache to the directory within a node. Another option is to buffer the incoming message locally in the interconnect controller, perhaps in its own FIFO queue. While this seems to be a reasonable design choice, it does add delay as well as some hardware complexity since incoming messages should be buffered in the interconnect controller only if the desired queue input is busy.

Our proposed design solves the problem as follows. Rather than try to implement buffering in the interconnect controller, we provide a separate input queue at the cache and directory for each of the input sources. This arrangement is shown in Figure 5-3. Note that the arbiters on the cache and directory queue inputs are eliminated, so commands to these controllers can be latched into the input queue immediately. Of course, the arbitration problem has really just been moved from the input of each queue to the output. But the problem is much simpler there, since neither of the arbitrating parties require "instant" processing as the interconnect controller does when an incoming command arrives. At the output, the consumer simply chooses to pick the next command from one queue or the other based on the queue empty/full information.

Figure 5-2: A solution to the traffic cop problem.

Figure 5-3: A modified configuration that replaces the arbiters on the inputs to the cache and directory controllers with separate input queues.

Note that we have left the arbiter for the interconnect controller input queue in the design, rather than replace it with two queues as well. This is because the two sources driving the arbiter, namely the cache and directory controllers, should be able to wait for the queue to become free without significant additional hardware complexity

or performance penalty. If it is found that this is not the case, then the double-queue solution can be used here as well.

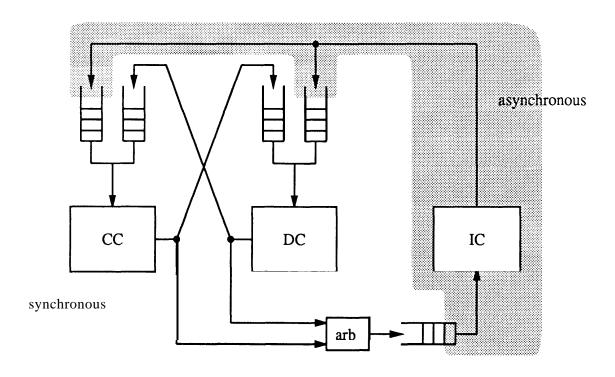

Another benefit comes from providing the cache and directory with separate queues to accept incoming messages from the interconnect controller. A likely implementation technology for the queues are the catalog FIFO memories based on fast static RAM technology. One feature of these parts is that there are separate data pins for the queue input and output, and the input and output ends of the queue can be controlled asynchronously with respect to each other. We can use this feature to our advantage if the interconnect in the system is asynchronous relative to the internal node, as is often the case. The FIFO memories can then provide the required asynchronous interface between the interconnect and the node. In other words, the interconnect controller would gate the data from the network directly into the directory and cache input queues rather than an internal buffer. Figure 5-4 shows the design again, highlighting the sections that are asynchronous relative to the processor clock.

Figure 5-4: Highlighting the parts of the system with asynchronous signals.

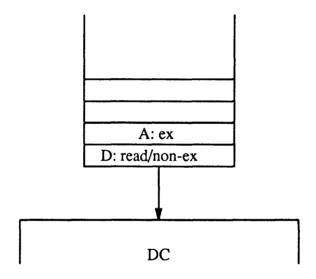

Unfortunately, the solution to the traffic cop problem shown in Figure 5-3 has a deadlock problem. Recall the section about preventing directory deadlock (Section 4.2). The condition for avoiding deadlock is that the directory cannot block replies from caches simply because a **C**→**MM** command is blocked. As we noted, the directory cannot proceed with a command if there is already another transaction pending for the same address. If this happens, the logical action for the directory is to temporarily stop pulling commands from the queue, i.e., block the queue. But if the queue is blocked, then the directory can receive no replies and the pending transaction that prevents the directory from proceeding will never complete. Blocking the queue violates the condition necessary to prevent directory deadlock.

In order to allow reply messages to bypass the blocked queue, we will provide two special **reply queues** on the input to the directory controller where replies are routed. Our revised (and final) solution to the traffic cop problem includes these extra queues for the directory controller as well as the original two **command queues** and is shown in

Figure 5-5. The mechanism works by encoding a **reply bit** in each message that indicates whether it is a command or a reply to a previous command. When a message arrives for the directory controller from the cache or interconnect controllers, it is gatedinto the corresponding command or reply queue depending on the value of the reply bit.

Figure **5-5:** Our final solution to the traffic cop problem includes separate queues on the input to the directory controller for replies and commands.

Finally, we must decide what should be done if a message arrives at a node for a queue that is full. One option is to let the message back up in the network by holding the communication link until the queue can accept input. This is feasible only if the network continues to allow other messages to get through to the node; otherwise, we have violated the condition for avoiding transit deadlock (see Section 4.3). An alternative strategy is aborting the message, allowing it to be sent again later. Since the queue will become full infrequently, the mechanism we choose to handle this case has negligible performance implications. We should implement whatever option is easiest, given the particular interconnection network in the system.

#### 5.2. Multiple Threads

An issue we have not considered up to **this** point is **single-threaded** versus **multiple-threaded** directory controllers. A single-threaded controller can have the transactions for no more than one  $C\rightarrow MM$  request pending at a given time. This restriction is not placed on multiple-threaded controllers. The advantage of multiple threads is that the directory can proceed with other  $C\rightarrow MM$  requests while waiting for caches to respond to  $MM\rightarrow C$  commands the directory issued for a different block. Although our design assumes a single-threaded directory controller, Section 8.5 will discuss the additional protocol and hardware support needed to implement multiple threads.

Let us again consider the reply queues of Figure 5-5 in the context of multiple threads. At first glance it appears that the reply queues are not necessary to prevent deadlock, because the directory does not stop processing commands from its input queue while it awaits a reply; therefore, a reply in the queue should eventually reach the

directory. Unfortunately, this argument is not entirely correct. While a multiple-threaded directory need not block its input queue whenever any transactions are pending (as does its single-threaded counterpart), it still must block the queue if any transactions *for the same address* as a new C→MM command are pending. Hence, deadlock is still possible, since a reply pertaining to a given address may get stuck in the queue behind an unrelated C→MM command for the same address.

As before, we can solve the deadlock problem by adding the reply queues **to** the multiple-threaded directory, and that may be the most desirable solution. Relative to the analogous case in a single-threaded controller, however, the directory input queue will block far less frequently. Perhaps commands and replies could use the same queue by having the directory discard the offending **C** $\rightarrow$ **MM** command rather than block it. The directory would then send a message to the slighted cache instructing it to retry its command. If this situation occurs infrequently then there should not be a noticeable effect on performance; furthermore, less hardware is required since we no longer need the reply queues.

#### 5.3. Routing

We have now defined the buses used to move messages between the subsystems in each node. Each subsystem receives its messages by gating them into its input queue from the bus. Message header bits are decoded to drive the control inputs of these queues. Queues receiving messages from the interconnect controller use a bit indicating whether the message is intended for the cache or the directory, and a bit that is set if the message is a reply (the aforementioned **reply bit**). Messages originating in the cache controller or directory controller may be intended for the local node or a remote node. The processor number from the message header must therefore be compared with the local processor number<sup>2</sup>; if they match, the local directory or cache queue latches the message data. Otherwise, the message is intended for a remote node, and the interconnect controller must **enqueue** the message.

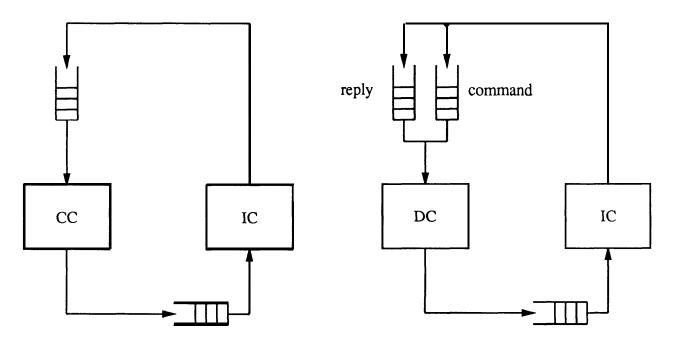

## 5.4. What Causes the **Traffic** Cop Problem?

As an aside, we note that the traffic cop problem is a manifestation of the system assumptions behind our design. Because the directory controller and cache controller are grouped together in a node, there are three resources per node (the cache controller, directory controller, and interconnect controller) that must communicate with each other. This implies that each controller must accept input from two sources; this is the cause of the traffic cop problem. Consider a system in which the memory and directory are not distributed across the processor nodes but instead communicate with all caches via the interconnection network. In such a system there are only two resources per node that need communicate with each other; the solution to the resulting traffic cop problem is much simpler and is shown in Figure 5-6. The simplicity in this system comes from the fact that no arbitration between two resources need occur within a node; all arbitration is handled at the interconnection network

#### 6. Command Definition

Earlier, we defined the commands necessary to implement directory-based cache consistency (see Table 3-1). This section will refine the definition of the commands to include the possible replies, to handle several subtle cases that occur, and to allow the proper implementation of a programming model of parallel execution.

<sup>&</sup>lt;sup>2</sup>The local processor number can either be held in a software-writable register or set by DIP switches.

cache unit: memory unit:

**Figure 5-6:** The solution to the traffic cop problem is simpler if the system has only two resources that must communicate on each node.

#### 6.1. Replies