## COMPUTER SYSTEMS LABORATORY

STANFORD UNIVERSITY STANFORD, CA 943054055

## THE ACCURACY OF TRACE-DRIVEN SIMULATIONS OF MULTIPROCESSORS

Stephen R. Goldschmidt John L. Hennessy

Technical Report No. CSL-TR-92-546

September 1992

This research has been supported by DARPA contract N00039-91-C-0138. Authors also acknowledge support from a Fannie and John Hertz Foundation Fellowship for Stephen Goldschmidt.

## THE ACCURACY OF TRACE-DRIVEN SIMULATIONS OF MULTIPROCESSORS

Stephen R. Goldschmidt and John L. Hennessy

Technical Report: CSL-TR-92-546

September 1992

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305-4055

#### **Abstract**

In trace-driven simulation, traces generated for one set of machine characteristics are used to simulate a machine with different characteristics. However, the execution path of a multiprocessor workload may depend on the ordering of events on different processors, which in turn depends on machine characteristics such as memory system timings. Trace-driven simulations of multiprocessor workloads are inaccurate unless the timing-dependencies are eliminated from the traces.

We measured such inaccuracies by comparing trace-driven simulations to direct simulations of the same workloads. The results were identical only for workloads whose timing dependencies were eliminated from the traces. The remaining workloads used either first-come first-served scheduling or non-deterministic algorithms; these characteristics resulted in timing-dependencies that could not be eliminated from the traces. Workloads which used task-queue scheduling had particularly large discrepancies because task-queue operations, unlike other synchronization operations, were not abstracted.

Two types of simulation results had especially large discrepancies: those related to synchronization latency and those derived from relatively small numbers of events. Studies that rely on such results should use timing-independent traces or direct simulation.

**Key Words and Phrases:** multiprocessors, performance evaluation, software instrumentation, trace-driven simulation

Copyright © 1992

by

Stephen R. Goldschmidt and John L. Hennessy

## **Contents**

| 1 | Background                                              | 1  |

|---|---------------------------------------------------------|----|

|   | 1.1 Principles of trace-driven simulation               | 1  |

|   | 1.2 Multiprocessor trace-driven simulation              | 1  |

|   | 1.3 Accuracy issues                                     | 2  |

|   | 1.4 Direct simulation                                   | 3  |

|   | 1.5 Related work                                        | 4  |

|   | 1.6 Goals of this work                                  | 4  |

| 2 | Techniques for dealing with timing-dependent trace-sets | 5  |

|   | 2.1 Abstracting locks and barrier synchronizations      | 5  |

|   | 2.2 Abstracting FCFS scheduling primitives              | 6  |

| 3 | Methodology                                             | 7  |

|   | 3.1 The Tango Lite Instrumentation System               | 7  |

|   | 3.1.1 Limitations of Tango Lite                         | 7  |

|   | 3.1.2 Overhead in Tango Lite                            | 8  |

|   | 3.2 Memory Simulator                                    | 8  |

|   | 3.2.1 Limitations of the simulator                      | 9  |

|   | <b>3.2.2</b> Tracing                                    | 9  |

|   | 3.3 Applications                                        | 10 |

|   | 3.3.1 Changes made to the applications                  | 10 |

|   | 3.3.2 Application characteristics                       | 11 |

| 4 | Results                                                 | 12 |

|   | <b>4.1</b> Cases with accurate trace-driven simulation  | 12 |

|   | <b>4.2</b> Error metrics                                | 13 |

|   | <b>4.3 Errors</b> with $\mathcal{G}_{ideal}$            | 13 |

|   | 4.3.1 Elapsed time                                      | 14 |

|   | 4.3.2 Parallel time vs. serial time                     | 14 |

|   | 433 Cycle counts                                        | 17 |

| 7 | Acknowledgments                                                            | 40 |

|---|----------------------------------------------------------------------------|----|

| 6 | Conclusions                                                                | 38 |

|   | 5.5 Differences between trace-generation environments                      | 37 |

|   | 5.4.7 Errors in C' – I and related results                                 | 37 |

|   | 5.4.6 Errors in $T_f$                                                      | 36 |

|   | 5.4.5 Errors in TLB latencies                                              | 36 |

|   | 5.4.4 Errors in $L_c$                                                      | 36 |

|   | 5.4.3 Errors in $L_{\mu}$                                                  | 36 |

|   | 5.4.2 Errors in $L_q$                                                      | 35 |

|   | 5.4.1 Errors in $L_d$                                                      | 34 |

|   | <b>5.4</b> Results with large errors · · · · · · · · · · · · · · · · · · · | 34 |

|   | 5.3 Results that were accurately simulated                                 | 34 |

|   | 5.2 The MP3D workload                                                      | 33 |

|   | 5.1 Cases with accurate trace-driven simulation.                           | 33 |

| 5 | Discussion                                                                 | 33 |

|   | 4.4.5 Address translation (TLB) latency                                    | 31 |

|   | 4.4.4 Memory reference latency                                             | 30 |

|   | 4.4.3 Synchronization latency                                              | 29 |

|   | <b>4.4.2</b> Cycle counts                                                  | 28 |

|   | 4.4.1 Elapsedtime                                                          | 27 |

|   | <b>4.4</b> Errors with $\mathcal{G}_{1/4}$                                 | 27 |

|   | 4.3.7 Address translation (TLB) latency                                    | 26 |

|   | 4.3.6 Memory reference latency                                             | 23 |

|   | <b>4.3.5</b> Synchronization latency                                       | 21 |

|   | 4.3.4 Instructions vs. idle cycles                                         | 18 |

## Chapter 1

## **Background**

Modem multiprocessor memory systems make extensive use of caches, buffers, and directories, any of which may be crucial to system performance. Analytic models cannot **deal** with the full complexity of such systems, so designers rely on simulation for insight into design trade-offs. Memory system and network designs are often evaluated using trace-driven simulation.

#### 1.1 Principles of trace-driven simulation

We define **an environment** to be a deterministic model of the characteristics of a machine. Simulation seeks to emulate the execution of a particular workload, w, in a particular environment, 7, the **target environment**.

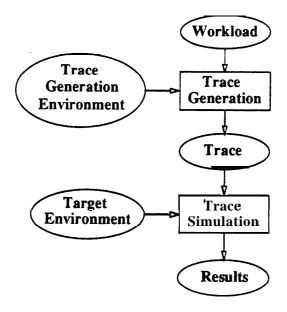

Trace-driven simulation is based on the divide-and-conquer principle; the problem of simulating the execution of w in T is divided into two subproblems: trace generation and trace simulation. The events that **occur** when w executes **in** a **trace generation environment** G are captured and recorded in a **trace**. The simulator reads the trace, and the results are taken to describe the behavior that would be observed if w were run in T. (See Figure 1.1.)

In this paper, we will consider memory system simulation only. In such simulations, the trace is composed primarily of memory references.

#### 1.2 Multiprocessor trace-driven simulation

Multiprocessors complicate trace-driven simulation. When tracing a multiprocessor workload, each processing element **(PE)** generates a logically-distinct trace. A multiprocessor memory/network simulator reads a **trace-set** consisting of one logical trace for each PE.

How does the simulator interleave memory references from different **PEs?** Following Bitar [2], we classify multiprocessor trace-driven simulation techniques into two types, **synchronous** and **asynchronous**.

In synchronous trace-driven simulation, the simulator preserves the reference sequence that occurred during trace generation. In practice, this technique is implemented in the trace generator, either by putting time-stamps in the traces or by merging references from different **PEs** into a single trace stream.

In asynchronous trace-driven simulation, the simulator adjusts the reference sequence to reflect differences between the reference latencies of  $\mathcal{G}$  and those of  $\mathcal{T}$ . Asynchronous TDS has been used, for example, by Eggers and Katz [5] to study the relative performance of two cache coherency protocols.

Figure 1.1: The trace-driven simulation process.

Both data and instruction references were recorded in their trace-sets. They assumed a nominal CPI of one, to which memory reference latencies were added by their simulator.

#### 1.3 Accuracy issues

The trace generation environment and the target environment should ideally be identical, but the costs and limitations of existing trace generation techniques usually make this impractical. Realistic traces can be generated by executing workloads with instrumented hardware (as in ATUM [1]) or instrumented software (as in TRAPEDS [12]). Hardware instrumentation produces traces that reflect the characteristics of the hardware used. These characteristics are unlikely to match those of 7. Software instrumentation offers greater flexibility, but is comparatively slow. Regardless of which technique is used, trace storage costs limit the number traces that can be stored. When evaluating a large number of target environments, a single trace generation environment is usually chosen, and the same traces are used to simulate each target environment. For these reasons, the trace-generation environment seldom matches the target environment This mismatch is a potential source of inaccuracies.

This study is concerned only with the inaccuracies that are caused by  $\mathcal{G} \neq 7$ . It is not concerned with inaccuracies can that arise from approximations made during trace generation and simulation. We therefore assume that the trace generator and simulator are both accurate, so that trace-driven simulation with  $\mathcal{G} = 7$  is accurate.

What conditions will ensure accurate trace-driven simulation if  $\mathcal{G} \neq T$ ?

$\mathcal{G}$  can influence the simulator only through the trace. If the workload were known to generate the same trace in both environments, accurate simulation would be assured This condition is satisfied in many uniprocessor simulations that do not time-stamp trace-events. For workloads in which memory latencies do not affect the sequence of memory references, environments that differ only in their memory latencies will generate identical traces.

Accurate trace-driven simulation can also be achieved by translating a trace generated in  $\mathcal G$  into the

trace that would have been generated in 7. For this reason, accurate simulation of a time-stamped trace is possible if the simulator compensates for the differences between the memory reference latencies of  $\mathcal{G}$  and 7 as it reads the trace. For example, suppose memory references in 7 always take one cycle longer than the corresponding references in  $\mathcal{G}$ . To translate a trace **from**  $\mathcal{G}$  into one for 7, one could simply increase each timestamp by the number of preceding memory references.

For many environments, the cost of translating the trace into one that is valid for 7 may be comparable to the cost of generating a new trace. For example, it would be costly to adjust time-stamps if the memory reference latencies of  $\mathcal{G}$  were so complex that they had to be simulated. Also, if the processor were to issue memory references out of order, the sequence of memory references generated by a basic block could depend on the environment. Asynchronous processes (such as interrupts) can introduce dependencies in the execution path itself. Such dependencies complicate accurate trace translation.

Certain workload features introduce timing-dependencies in the traces they produce. Consider a workload which (among other things) reads the elapsed time and formats it for output. The execution path through the formatting routine would then depend on the value of the elapsed time. The trace of the workload is therefore timing-dependent.

Multiprocessor workloads are particularly likely to have timing-dependencies, due to the presence of asynchronous interactions between processes. Such interactions include dynamic allocation, barrier synchronization, and unsynchronized read-write access to shared data.

Any workload which allocates shared resources on a first-come, first-served (FCFS) basis is likely to produce timing-dependent trace-sets. FCFS policies are commonly used to allocate tasks, loop iterations, memory, and access to critical-sections. The trace-set of such a workload is likely to depend on which resources are assigned to which PEs. Resource allocation depends on order in which PEs make their requests, which depends on the latencies of the preceding memory references made by each PE.

Barrier synchronizations also produce timing-dependent trace-sets if **PEs** spin while they wait at the barrier. Spins generate memory references, and the number of references generated depends on the relative completion times of the various **PEs** entering the barrier. Workloads that use FCFS allocation and barriers may produce timing-dependent trace-sets even if the results of the workload itself are not timing-dependent.

Some workloads allow unsynchronized access to shared data by different **PEs**. The trace-sets produced by such workloads will be timing-dependent if the order of the accesses affects the trace. For example, in simulated annealing algorithms, the final solution is an approximation. To permit greater parallelism, implementations of such algorithms often permit simultaneous accesses to the current optimum. Such workloads are likely to produce timingdependent traces.

When timing-dependencies are present, a small change to the environment can induce numerous changes to the execution path of a PE. These changes induce further changes, and so on. As a result, environments that differ in minor ways may generate radically different trace-sets. For instance, changing cache sixes can affect the number of misses occurring in each task. In workloads where tasks are assigned to **PEs** on a FCFS basis, this may impact the assignment of tasks to **PEs**, altering the large-scale communication patterns of the workload.

**In** Chapter 2, we will address the problem of accurate TDS in the presence of timing dependencies.

#### 1.4 Direct simulation

Direct simulation provides an alternative to trace-driven simulation. In direct simulation, memory references are simulated as they occur. No traces are required, and only one environment is involved.

The accuracy of direct simulation is limited only by approximations in the workload execution software (which corresponds to the trace-generation software in TDS) and in the simulator itself.

#### 1.5 Related work

In his critique [2], **Bitar** argued that trace-driven simulation is not generally valid for multiprocessor studies. After considering both asynchronous and synchronous trace-driven simulation, he concluded that multiprocessor trace-driven simulation techniques must be validated by analysis or low-level simulation. He showed that the inter-process interactions found in access-control algorithms are inaccurately modeled by trace-driven simulation. However, he did not connect the inaccuracies with timing dependencies, nor did he prove that the inaccuracies were ever great enough to be of practical concern.

In [3], we pointed out that the nondeterminis m in many parallel workloads makes accurate tracing difficult We emphasized that a trace-set obtained for one environment could represent an execution order that was impossible for the target environment. To address this problem, we presented the Tango simulation system, a flexible direct-simulation tool for studying shared-memory applications and environments.

In [7], Holliday and Ellis studied the amount of re-simulation required to create an accurate trace-set for one environment from a trace-set of another. Finding that traditional trace-sets were inadequate for accurate trace-driven simulation, they based their approach on intrinsic traces. (An intrinsic trace consists of the control-flow graph of the workload plus address and timing data for each basic block.) Their findings are difficult to apply to traditional trace-sets, which are composed of isolated events. They noted that traditional trace-sets can provide accurate simulation for some workloads (by abstracting the locks and barriers) but, beyond this, their work did not address the use of traditional trace-sets.,

In [8], Koldinger, Eggers, and Levy studied the effects of time dilation on trace generation. They introduced various degrees of time dilation into a software-based trace generation system. They found that time dilation had a slight impact on the accuracy of two simulation results: miss ratio and bus utilization. Errors **occured** only because their instrumentation system was unable to preserve the global order of memory references in the presence of time dilation. Modem instrumentation systems (such as Tango) have the ability to maintain this order. With such systems, time dilation need not be a source of error. Thus, the errors Koldinger, Eggers, and Levy observed were not intrinsic to trace-driven simulation.

#### 1.6 Goals of this work

We have seen that a connection exists between timing dependencies and the accuracy of trace-driven simulation.

In the next chapter, we will present a technique that permits accurate trace-driven simulation of multiprocessors in the presence of timing dependencies caused by locks and barriers. Our approach is based on the methods used by Eggers and Katz in [5]. We will discuss difficulties in dealing with timing-dependencies which affect large portions of the trace-set.

In the chapters that follow, we quantify the inaccuracies in actual trace-driven simulations and explain the observed behavior. We find that the inaccuracies are very small in most cases. Results related to synchronization latency have large inaccuracies, as do results based on small numbers of events. The workloads which use task-queue scheduling have particularly poor accuracy because the **timing-**dependencies caused by task-queue operations are difficult to eliminate.

## Chapter 2

# Techniques for dealing with timing-dependent trace-sets

In a multiprocessor environment, events occurring on different **PEs** are largely asynchronous; the ordering of memory references from different **PEs** is generally unconstrained The interleaving of memory references **from** different **PEs** will depend on the environment. Synchronous **TDS** generally cannot accurately simulate environments other than  $\mathcal{G}$ , because it must simulate memory references in the order they are **generated**.

On the other hand, for some workloads, asynchronous TDS can accurately simulate multiple environments with a single trace-set. In asynchronous TDS, the interleaving of memory references from different PEs is determined during simulation, based on the latencies associated with the target environment Without re-interpreting the workload, a simulator cannot make extensive changes to the execution paths of individual PEs, but many timing-dependencies have only limited impact on the execution path. The ability to eliminate these timing-dependencies from **the** trace-set by means of **abstraction** is the key to accurate trace-driven simulation. We now show how this abstraction is accomplished for locks and barrier synchronizations.

#### 2.1 Abstracting locks and barrier synchronizations

Suppose the only timing-dependency in w were caused by two **PEs** trying to acquire the same spin-lock: in 7,  $p_1$  gets the lock after spinning three times, but in G,  $p_2$  gets it after spinning once. The execution paths would be different, so the raw trace-sets must also differ.

However, if we could ignore the number of times each PE spins during lock acquisition, the trace-set would look the same in both environments. We can make the trace-set timing-independent by translating each lock-acquisition loop into an abstract "spin-loop" event. The environment-dependent features (the number of iterations) are thus eliminated from the trace-set, which is now valid for both environments.

Naturally, for this technique to work, the simulator must process the new "spin-loop" event properly; when it reads a "spin-loop" event from a trace, it must determine the correct number of iterations for the target environment. The simulator can do this by simulating spins until another process releases the lock.

The approach we have described is essentially the same as that used in [5]. It relies on two **seldom-**violated properties of the spin-loops used to implement locks:

• Spin-loops have few parameters. To simulate the loop, the simulator need only know the address of

the lock and the address of the start of the loop. This information can be embedded in the trace-set. (We assume that all spin-loops in the workload are implemented in exactly the same way.)

Spin-loops do not return a value, and their side-effects (changes to the state of the lock) usually

do not affect any address calculations in the workload outside of related spin-loops. The timingdependencies are thus limited to small portions the trace-set.

An application could violate the latter property if state of the lock were used for some purpose other than spinning. Such behavior might occur, for instance, in a workload that monitors its own locking patterns. Abstraction alone cannot handle such workloads correctly, because large portions of the trace-set could be affected.

Barrier synchronizations possess much the same properties as spin-loops. The effect of a barrier is to delay **each** PE by a different amount. If barrier entry is treated as an abstract trace **event**, these delays can be easily recomputed for each environment. (The simulator does this by simulating spins until **all** processes have entered the barrier.) Thus, the technique of abstracting **timing-dependencies from** the trace-set works for barriers as well as locks.

#### 2.2 Abstracting FCFS scheduling primitives

-Abstracting locks and barriers eliminates most of the timing-dependencies found in **statically-scheduled workloads**, that is, workloads in which, for a given input, the assignment of work to **PEs** is fixed. In **dynamically-scheduled workloads**, work is assigned to idle **PEs** on a first-come, first-served (**FCF** S) basis.

FCFS scheduling introduces timing dependencies. These dependencies can influence branch conditions and address computations over large portions of the workload. The fetch-and-add operation illustrates this problem. Fetch-and-add is commonly used to distribute iterations among **PEs** in a distributed loop; when a PE completes an iteration, it performs a fetch-and-add on a shared counter to determine the next iteration for **that** PE. While it is possible to abstract the fetch-and-add itself from the trace-set, the returned index is timing-dependent and affects the remainder of the trace in a complex fashion. It is typically used as an array index, and value read from the array can affect other data and/or branch addresses.

Such timing dependencies could be eliminated, at the cost of additional simulator complexity, if each iteration had a deterministic trace. The trace-generator could record the trace of each iteration in a separate file. The simulator could then assign iterations to **PEs** dynamically. This approach would allow accurate simulation of fetch-and-add in simple cases, however, we do not know of **any** simulators that have implemented it.

Shared queues and heaps pose a somewhat more complex problem than fetch-and-add operations. Like fetch-and-add operations, the values returned by queue operations may affect large portions of the trace-set. In addition, queues permit many possible operations, some of them quite complex. For example, the situation in which a PE tries to take work from an empty queue may be handled in many different ways, depending on the scheduling policies of the workload.

To summarize: the operations used in dynamic scheduling introduce trace-set timing-dependencies that are not localized. It is difficult to accurately simulate such workloads using conventional traces.

## Chapter 3

## Methodology

A major goal of this study is to evaluate the accuracy of trace-driven simulation. To this end, we simulated a simple shared-memory multiprocessor environment running various workloads. We obtained simulation results for this environment using two different trace-generation **environments**, one **idealized**, one similar to the target environment. We compared the results of these simulations to nominally "accurate" results obtained by **direct** simulation.

To eliminate errors due to approximations introduced by the instrumentation and simulator, **the** same a instrumentation and memory simulator were used for both the -trace-driven and direct simulations. The measured discrepancies therefore reflect approximations intrinsic **to** the trace-driven simulation techniques used.

The remainder of this chapter presents details of the instrumentation system, memory simulator, and workloads used.

#### 3.1 The Tango Lite Instrumentation System

The workloads were compiled into executable simulations using **Tango Lite**, an assembly-language instrumentation system for the MIPS processor architecture. Tango **Lite** allows a uniprocessor to perform direct simulation of a multiprocessor workload.

**Tango Lite** is a successor to the Tango simulation system described in [4, 6]. Unlike **Tango**, **Tango Lite** represents application processes **as** light-weight threads executing in a common virtual address space. This change eliminates the need to call to operating system's scheduler, allowing much faster simulation.

**Tango Lite** instruments application code with calls to the simulator at strategic points during execution, such as loads, stores, and synchronization events. It also supports a distributed notion of time, in which each thread has an independent simulation clock. **Tango Lite** supports the scheduling of application threads in such a way that events from different threads are simulated in the correct temporal order.

#### 3.1.1 Limitations of Tango Lite

**Tango Lite has several limitations** which affect the accuracy its results:

• Tango Lite does not instrument the operating system kernel. (The applications we study are computate-intensive; the kernel should have relatively little impact on their performance.)

- Tango **Lite** can only instrument those portions of the run-time libraries that **are** not used by its own run-time system. Uninstrumented library ♣◆■順◆★□■• are treated as atomic operations.

- Most of the library code used by the applications in this study was instrumentable. The math library (libr) was instrumented, as was much of the C run-time library (libc). The estimated fraction of cycles spent in uninstrumented functions ranged from 0.16% of total cycles (in Barnes) to 14% (in LocusRoute). The uninstrumented portions of the run-time library included functions that provide output formatting (such as printf), memory allocation (malloc), and file I/O (fopen).

- Because the application and the simulator share a common address space, the addresses of application data are displaced by simulator data and by expansion of the application code by the instrumentation.

- Techniques to correct for such displacements are known (see [12]), but we have not implemented than for **Tango Lite**, **feeling** that **the additional** cost of these **features was not justified**. **Since** application data tend to be fairly contiguous in **memory**, **we** expect **the effects** of such displacement to be minor.

- Because **Tango Lite** instruments at the assembly-language level, it perturbs the reordering phase of the assembler. As a result, fewer delay slots in the application code can be filled, **inflating** the instruction counts somewhat. The order of independent data references within a basic block may also be perturbed.

**Because these** limitations **affect** both the trace-driven and direct simulations, they do not contribute to the discrepancies reported in Chapter 4.

#### 3.1.2 Overhead in Tango Lite

The execution overhead of Tango **Lite** can be substantial. Fortunately, time dilation does not affect results obtained from Tango **Lite-based** simulations because (unlike most prior trace generation systems for multiprocessors [13]) event order in Tango **Lite** is determined by event-driven simulation. Thus, while simulation overhead limits the problem sizes that can be reasonably simulated, it has no effect on the accuracy of trace generation and simulation.

Instrumentation of the applications at data references and basic blocks typically increased application static size by a factor of four and uniprocessor execution time by a factor of 45. However, these figures do not include the memory system simulator. This instrumentation overhead was insignificant compared to the cost of simulating the memory system. In this study, memory simulation typically increased execution times by another factor of 17 over the execution time of the **instrumented** application with no simulator. Thus, the net slowdown factor was roughly 750.  $(45 \times 17 = 765.)$

#### 3.2 Memory Simulator

We used a single memory system simulator for both trace generation and simulation. The simulator computes reference latencies for a hypothetical shared-memory multiprocessor with snoopy caches. Each PE has a fully-associative TLB and a direct-mapped cache. Writes pass through the cache and are **broadcast** on the bus, where they **invalidate any corresponding** copies in other caches. (For the target **environment**, T, we used a **TLBs** with 28 entries and caches with 1024 4-word blocks.) The simulator also has an option allowing it to simulate an ideal memory system which satisfies all references in a single cycle.

In this study, all synchronizations except task-queues were treated as abstract operations. Task-queues are implemented slightly differently by each application, so they are much more difficult to abstract.

#### 3.2.1 Limitations of the simulator

The simulator makes a number of simplifying assumptions about the environment:

- Pipelining is not simulated, and data accesses precede the corresponding instruction fetches, rather than following them, as they would in a real machine.

- Memory references associated with synchronization are filtered out, to avoid distorting the cache

miss rates. Similarly, TLB faults are treated as idle time. As a result, synchronizations and TLB

faults do not cause any memory references.

- We use an idealized synchronization model that assumes negligible communication delay between

PEs. Thus, for instance, there is is no delay between the release of a lock and acquisition by a

waiting PE.

- A trivial physical-to-virtual page mapping is implemented in the TLB. Contiguous virtual addresses always have contiguous physical addresses.

- Interference from DMA and interrupts are not simulated.

Because these limitations affect both trace-driven and **direct** simulations, they do not contribute to the discrepancies reported in Chapter 4.

#### 3.2.2 Tracing

We optimized the tracing system to reduce the time- and space-requirements for trace generation:

- To eliminate the need for an explicit process ID in each trace record, separate trace files were generated for each PE.

- Explicit time-stamps were eliminated by recording instruction references in the traces. Bach instruction ideally takes one cycle, so the simulator can determine the number of cycles between two data references events by counting the number of intervening instructions and adding latencies due to **TLB** faults and cache misses. (This technique was inspired by the methodology of [5].)

- To further reduce trace size, consecutive instruction references were encoded into a single trace

record and combined with any following data reference. (This technique is particularly effective

with Tango Lite because it turns out that each instrumentation point generates only a single trace

record.)

- Writing a trace-set to disk and then reading it back introduces substantial overhead, so we developed a buffering system to pass trace data directly from the trace generator to the simulator using fixed-size shared memory buffers, one for each simulated PE. Semaphores were used to synchronize the reading and writing of these buffers. Such a scheme may encounter deadlock because different PEs generate trace data at different rates. The simulator automatically detected deadlock conditions, and simulations that aborted due to deadlock were re-run using disk-based traces.

#### 3.3 Applications

The application codes that make up the workloads in this study were derived primarily from the SPLASH suite described in [11].

The SPLASH suite consists of six applications: one in FORTRAN (Ocean) and five in C (Cholesky, LocusRoute, MP3D, PThor, and Water). Each application is a program of significant size and complexity. All except Cholesky solve complete problems in scientific simulation or computer-aided design. The applications were explicitly parallelized using m4 macros based on the monmacs[9] macro library. <sup>1</sup>

Since many timing-dependencies are associated with dynamic scheduling, the scheduling algorithms used by the applications were particularly important to this study. Three of the original SPLASH applications (MP3D, Ocean, and Water) use static task scheduling; the remainder use taskqueues. We also introduced an alternate version of MP3D, called Dynamic MP3D. The Dynamic MP3D application is identical to MP3D except that it schedules loops dynamically, rather than statically.

We further supplemented SPLASH with a new application, called **Barnes**, which uses the **Barnes**-Hut algorithm to solve *n*-body problems similar to those arising in astrophysics. (**Barnes** has since been added to the SPLASH suite.) The **Barnes code is** interesting because of its unusual scheduling technique [10]. On the first iteration, it distributes tasks dynamically, using a distributed loop. On successive iterations, it partitions work among **PEs** using deterministic heuristics that tend to equalize the amount of work assigned to each PE. For comparison, we introduced a second version of this application, named **Dynamic Barnes**, which uses the distributed loop on every iteration.

In the end, a total of nine applications were used: three with static scheduling and six with dynamic scheduling.

#### 33.1 Changes made to the applications

The SPLASH applications were written for a vitual-memory model which gives each process a private copy of all variables not declared "shared." (This follows **the semantics** of **the fork** system call.) However, the **Tango Lite** instrumentation system is threads-based. Threads provide a shared virtual address space, which is inconsistent with the model assumed in SPLASH. We therefore had to port the applications to the shared virtual-memory model. This was done by manually editing each application to replicate statically-allocated data that would be modified during parallel computation.

Most of the synchronizations in the applications were coded using **monmacs**, allowing **Tango Lite** to identify them and treat them as abstract operations. A few synchronizations were written as spin-loops in the original codes. Wherever possible, these synchronizations were converted to standard macros. The only remaining synchronizations were task-queue operations, found **in Cholesky, LocusRoute**, and **PThor**. Special instrumentation was added by hand to these applications to delimit the spins, allowing **Tango Lite** to recognize them as synchronization.

Throughout this study, the applications were simulated to completion; both parallel and serial **computatations** were simulated. To keep simulation costs reasonable, the problem sizes we used were (except in the case of **MP3D**) somewhat smaller than those used in [11].

Official SPLASH bug fixes through August 28, 1991 were incorporated into the codes used in this study.

<sup>&</sup>lt;sup>1</sup>Monmacs was developed by the Advanced Computing Research Facility at Argonne National Laboratories.

#### 3.3.2 Application characteristics

Table 3.1: Application characteristics with 10 PEs.

|                |                           | Synch. cycles | I-fetches | D-reads  |      | writes   |      |

|----------------|---------------------------|---------------|-----------|----------|------|----------|------|

| Application    | Problem size              | millions      | millions  | millions | % sh | millions | % sh |

| ocean          | 62 x 62 grid              | 0.9           | 34.6      | 9.4      | 95.7 | 3.2      | 89.2 |

| Water          | 2 steps/4 x 4 x 4 lattice | 25.8          | 51.5      | 8.5      | 37.4 | 4.3      | 4.9  |

| MP3D           | 30 steps/5K particles     | 25            | 47.5      | 10.1     | 71.4 | 5.3      | 52.2 |

| Dynamic MP3D   | 30 steps/5K particles     | 2.0           | 48.2      | 10.4     | 69.7 | 5.1      | 53.4 |

| Barnes         | 10 steps/l28 bodies       | 18.8          | 61.5      | 12.0     | 63.5 | 7.5      | 35.4 |

| Dynamic Barnes | 10 steps/l28 bodies       | 8.8           | 61.0      | 12.0     | 63.4 | 7.5      | 35.5 |

| Cholesky       | lshp.O                    | 88.8          | 44.5      | 11.5     | 90.6 | 4.0      | 78.8 |

| LocusRoute     | 2 steps/bnrE.grin         | 1.5           | 25.3      | 5.0      | 69.9 | 2.2      | 43.5 |

| PThor          | 500 steps/risc processor  | 53.9          | 74.3      | 17.2     | 75.2 | 5.8      | 50.3 |

Table 3.1 summarizes the synchronization and reference behavior of the applications. The measurements in this table are from simulations of the target environment (described in Section 3.2) with 10 PEs.

The "% sh" figures indicate the fraction of references of each type which were to shared addresses. The sharing fractions in the table are higher than those reported in [ 1 1]. This is due to data that were originally private to each PE, but were replicated in shared memory when the applications were ported to the shared virtual-memory model.

## **Chapter 4**

## **Results**

This chapter describes the experiments we performed and the behavior we observed

We evaluated the accuracy of asynchronous trace-driven simulation using two different trace-generation environments (G's) to simulate the target environment, T. We chose the bus-based memory system described in Section 3.2 for our target environment. In each trace-generation environment, we simulated the nine parallel applications described in Section 3.3, varying the number of simulated **PEs**, p, from 1 to 10. Of the 90 possible workloads for each trace-generation environment, only 85 were actually simulated. (The Ocean application could not be simulated with p = 3, 5, 7, 8, or 9 **PEs**. Ocean constrains p to be either 1 or an even number that divides g - 2, where g is the grid size. Our choice of g = 62 limited us to p = 1, 2, 4, 6, or 10 **PEs**.)

The trace-generation environments we chose typify two approaches to trace generation. For our first set of experiments, we generated traces with an idealized environment, hereafter denoted by  $\mathcal{G}_{ideal}$ .  $\mathcal{G}_{ideal}$  models an idealized memory system capable of satisfying any number of simultaneous references in a single cycle. It exemplifies the trace-generation environments used in studies in which traces are generated by software instrumentation. The target environment, T, was fairly complex, so the differences between  $\mathcal{G}$  and  $\mathcal{T}$  were substantial.

For the second set of experiments, we chose a more complex trace-generation environment, hereafter denoted by  $\mathcal{G}_{1/4}$ . This environment was identical to  $\mathcal{T}$  except that its caches were only 1/4 as large (256 blocks). Such minor differences between the trace-generation and target environments might be found in studies that use hardware instrumentation to generate traces.

Among the 85 workloads we simulated, there were 22 that gave completely accurate TDS results in both trace-generation environments. These workloads are described in Section 4.1. The results for the remaining workloads are organized by trace-generation environment. Section 4.2 defines metrics for assessing simulation accuracy. The experimental data for  $\mathcal{G}_{\text{ideal}}$  are presented in Section 4.3, and those for  $\mathcal{G}_{1/4}$  may be found in Section 4.4. The patterns that emerge will be discussed and explained in Chapter 5.

#### 4.1 Cases with accurate trace-driven simulation

The trace-driven results and the nominal results agreed perfectly for 22 workloads. In the remaining 63 workloads, agreement between TDS and nominal results was the exception rather than the rule.

The workloads with accurate **TDS** were identical in both trace-generation environments, namely:

• workloads with a single PE (p = 1) and

• workloads where the application was Ocean or Water.

These workloads illustrate -important properties of **TDS** which will be discussed in Section 5.1. However, we exclude them from the data presented in the following sections.

#### 4.2 Error metrics

Our evaluation of TDS accuracy is based on discrepancies ("errors") between the trace-driven simulation results and nominal results. (Because the simulations are deterministic, we present data from a single simulation of each workload in each environment.)

In individual workloads, we quantify the discrepancies as a percentage of the nominal value. More precisely, given a nominal result,  $x_{nom}$ , and the corresponding TDS result,  $x_{tds}$ , we define the error:

$$\epsilon rr(x) = \begin{cases} (x_{\text{tds}} - x_{\text{nom}})/x_{\text{nom}} \times 100\%. & \text{if } x_{\text{nom}} > 0; \\ 0\%. & \text{if } x_{\text{tds}} = x_{\text{nom}} = 0. \end{cases}$$

E rr(x) exaggerates positive errors, resulting in skewed error distributions. When making statistical tests, we compensate for this skew by applying a logarithmic transformation **to** x, obtaining **the normalized error**,  $n \epsilon rr(x) = \ln(x_{\text{tds}}/x_{\text{nom}})$ .

For many results,  $|\epsilon rr(x)|$  was not **significantly** correlated with the number of **PEs**. We therefore tabulate **the mean error magnitude** for each application:

mean

$$|\epsilon rr(x)| = \frac{1}{9} \sum_{v=2}^{10} |\epsilon rr(x)|$$

Since the mean error magnitude obscures the signs of the errors, we append a "+" or a "-" to the mean magnitude (to indicate the sign of the mean) in cases where the sign is **significant**. Significance is determined by means of a one-sided f-test with  $\alpha = 0.05$ . (The t-test assumes normally-distributed data, so we apply the test to  $n \epsilon rr(x)$  rather than  $\epsilon rr(x)$ .)

When comparing the contributions of different components of a result to its error, we use the magnitude of the difference between the TDS and nominal values of the component,  $|x_{i,tds} - x_{i,nom}|$ , denoted  $|\Delta(x_i)|$ .

#### 4.3 Errors with $\mathcal{G}_{ideal}$

We now present data from simulations of 63 traces generated in the  $\mathcal{G}_{ideal}$  environment.

This section is divided into subsections dealing with different simulation results. In Section 4.3.1, we present error data for elapsed tune. In Section 4.3.2, we decompose the elapsed time to distinguish the parallel and serial stages. In Section 4.3.3, we compare the errors in the elapsed time to errors in the cycle count. In Section 4.3.4, we decompose the cycle count into instructions and idle cycles. We find that timing errors (including elapsed time, parallel time, and cycle counts) were primarily due to errors in the simulation of idle time. We then analyze the three sources of idle time: Section 4.3.5 presents data on synchronization latency errors, Section 4.3.6 deals with errors in memory reference latencies, and Section 4.3.7 deals (briefly) with address-translation latency.

#### 4.3.1 Elapsed time

We start by considering the elapsed time,  $T_{\epsilon}$ , measured by trace-driven simulation  $Err(T_{\epsilon})$  is particularly important because it is tied directly to  $\epsilon rr(S)$ , the error in the overall **speedup**. <sup>1</sup>

The majority of the  $T_{\epsilon}$  errors were small or insignificant;  $|\epsilon| rr(T_{\epsilon})|$  was < 0.2% for 52.% of the workloads. The largest  $T_{\epsilon}$  error was +2.03% (for **Dynamic Barnes**, with eight **PEs**) and the overall mean  $|\epsilon| rr(T_{\epsilon})|$  was only 0.41% (N = 63).

It is **difficult** to account for the  $T_{\epsilon}$  errors in individual workloads because  $T_{\epsilon}$  is influenced by numerous minor perturbations of the simulated execution path. To make sense of the data, some organization is needed. An analysis of variance (ANOVA) test on  $n\epsilon \, rr(T_{\epsilon})$  showed that  $\epsilon rr(T_{\epsilon})$  did not depend on p any more than could be accounted for by chance. We therefore organized the data on an **application-by**-application basis.

Table 4.1 reports the mean and extreme  $|\epsilon| rr(T_{\epsilon})|$  for each application.

| MP3D         0.03 %         -0.09%           Dynamic MP3D         0.08%+         +0.13%           Barnes         0.03%-         -0.07%           Dynamic Barnes         1.33 %+         -12.03%           Choleskp         0.63%         -1.72%           LocusRoute         0.45%         i- 1.40% | The state of the s |                                    |                                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|

| Dynamic MP3D       0.08%+       +0.13%         Barnes       0.03%-       -0.07%         Dynamic Barnes       1.33 %+       -12.03%         Choleskp       0.63%       -1.72%         LocusRoute       0.45%       i- 1.40%                                                                          | Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mean $ \epsilon rr(T_{\epsilon}) $ | $\max  \epsilon rr(T_{\epsilon}) $ |  |  |

| Barnes         0.03%-         -0.07%           Dynamic Barnes         1.33 %+         -12.03%           Choleskp         0.63%         -1.72%           LocusRoute         0.45%         i- 1.40%                                                                                                   | MP3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.03 %                             | -0.09%                             |  |  |

| Dynamic Barnes         1.33 %+         -12.03%           Choleskp         0.63%         -1.72%           LocusRoute         0.45%         i- 1.40%                                                                                                                                                  | Dynamic MP3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.08%+                             | +0.13%                             |  |  |

| Choleskp         0.63%         -1.72%           LocusRoute         0.45%         i- 1.40%                                                                                                                                                                                                           | Barnes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.03%-                             | -0.07%                             |  |  |

| <b>LocusRoute</b> 0.45% i- 1.40%                                                                                                                                                                                                                                                                    | <b>Dynamic Barnes</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.33 %+                            | -12.03%                            |  |  |

|                                                                                                                                                                                                                                                                                                     | Choleskp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.63%                              | -1.72%                             |  |  |

| <b>PThor</b> 0.34%+ +0.54%                                                                                                                                                                                                                                                                          | LocusRoute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.45%                              | i- 1.40%                           |  |  |

|                                                                                                                                                                                                                                                                                                     | PThor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.34%+                             | +0.54%                             |  |  |

Table 4.1: Elapsed Time Errors with  $\mathcal{G}_{ideal}$  for 2 to 10 PEs.

We partition the applications into two groups based on the size of  $|\epsilon rr(T_{\epsilon})|$ . The *large-error* group, containing **Choleskp, Dynamic Barnes, LocusRoute**, and **PThor**, consists of applications with mean  $|\epsilon rr(T_{\epsilon})| > 0.2\%$ . The **small-error** group, containing **MP3D**, **Barnes**, and **Dynamic MP3D**, consists of applications with mean  $|\epsilon rr(T_{\epsilon})| < 0.1\%$ . The ratio between the variances of  $n \in T_{\epsilon}$  for the two groups was 190, indicating that the distinction between the two groups was fairly great.

The signs of the  $T_{\epsilon}$  errors were biased toward the positive side. Whereas  $\epsilon \, rr(T_{\epsilon})$  was positive for 45 workloads, it was negative for only 18. (In other words, trace-driven simulation exaggerated the elapsed time five times for every two times that it understated it.) Four of the applications showed a significant bias in  $n \, \epsilon \, rr(T_{\epsilon})$ : three were biased toward positive errors and one (Barnes) was biased toward negative errors.

#### 4.3.2 Parallel time vs. serial time

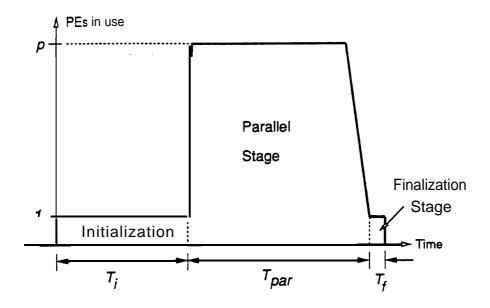

To determine the source of the errors in  $T_{\epsilon}$ , we decompose  $T_{\epsilon}$  into three components:

- the duration of the (serial) initialization stage,  $T_i$ ,

- the duration of the parallel stage,  $T_{pa}$ , and

$$\epsilon rr(S) = (\frac{100\%}{\epsilon rr(T_e) + 100\%} - 1) \times 100\%.$$

<sup>&</sup>lt;sup>1</sup>Because  $S = (T_{e,n=1})/T_{e}$ , and  $T_{e,tds,p=1} = T_{e,eds,p=1}$ , it follows from the definition of err(x) that:

Figure 4.1: Idealized workload execution profile.

• the duration of the (serial) finalization stage,  $T_f$ .

Figure 4.1 illustrates this decomposition for an an idealized workload.

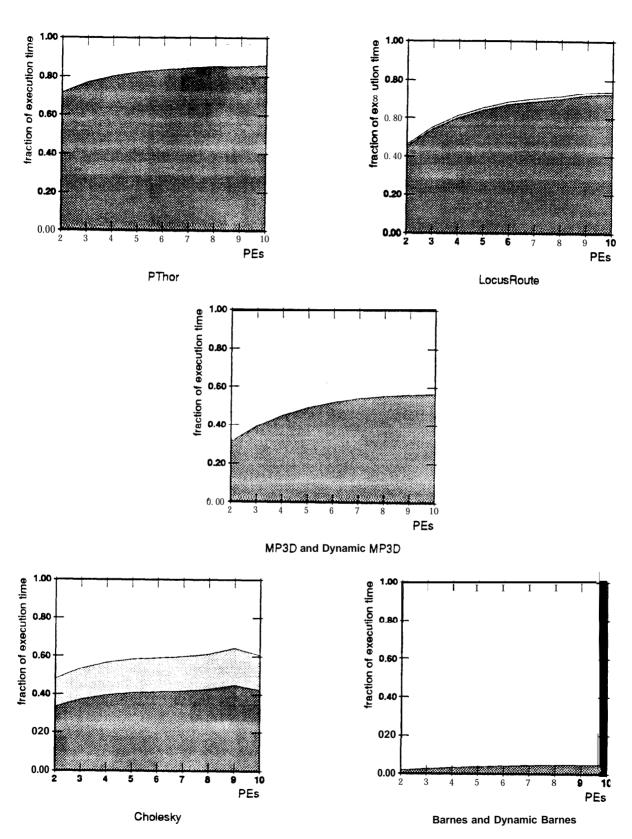

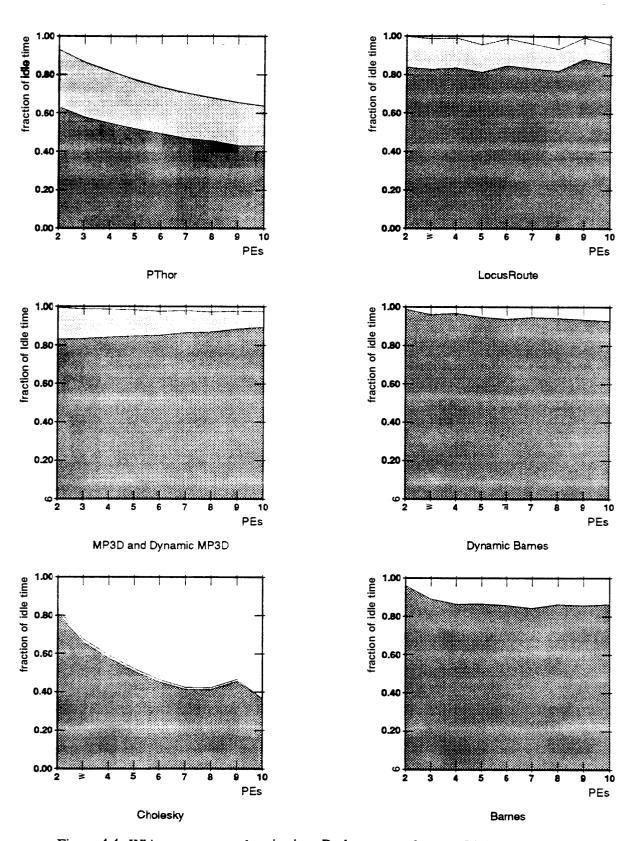

The proportions of these components depended strongly on both the application and the number of **PEs** simulated. In particular, the parallel fraction tended to decrease as the number of **PEs** grew. Figure 4.2 (on the next page) shows the decomposition of  $T_{\epsilon}$  for each workload.

We are primarily interested in the parallel stage, since that is the stage that would dominate in simulations of full-scale workloads. However, for the problem sixes we used, a **significant** portion of each  $T_{\epsilon}$  was due to the serial stages. The serial fraction,  $(T + T_f)/T_{\epsilon}$ , ranged from 1.6% to 85.7%, and  $T_{\epsilon} + T_f$  represented more than half of  $T_{\epsilon}$  for 56. % of the workloads. Despite their importance to the elapsed time, the serial stages do not seriously distort our error measurements; they simply dilute errors in the parallel stage. To support this claim, we present Table 4.2, which **summarizes** the effect of trace-driven simulation on the duration of each stage.

Table 4.2: Stage Duration Errors with  $\mathcal{G}_{ideal}$  for 2 to 10 PEs.

| Application    | mean | $ \epsilon rr(T_i) $ mean $ \epsilon rr(T_{par}) $ | mean $ err(T_f) $ |

|----------------|------|----------------------------------------------------|-------------------|

| MP3D           | 0%   | 0.05%                                              | 10.1%             |

| Dynamic MP3D ( | ) %  | 0.16%+                                             | 8.83%             |

| Barnes         | 0%   | 0.03%                                              | 8.12%             |

| Dynamic Barnes | 0%   | 1.39%+                                             | 6.01%-            |

| Cholesky       | 0%   | 3.20%                                              | 3.81%             |

| LocusRoute     | 0%   | 1.34%                                              | 0.45%             |

| PThor          | 0%   | 1.93%+                                             | 549.%             |

The initialization stage, which made up the bulk of the serial time, was accurately simulated for all workloads. The finalization stage, meanwhile, was greatly distorted.  $T_f$  exceeded 0.1% of  $T_\epsilon$  in only two applications: **Cholesky** and **LocusRoute**. The finalization stage was too short to noticeably **affect**  $\epsilon rr(T_\epsilon)$ . In all 63 workloads, the parallel stage contributed more to  $\epsilon rr(T_\epsilon)$  than the finalization stage.

Figure 4.2: White areas = parallel. Dark gray = initialization. Light  $\mathbf{gray} = \mathbf{finalization}$ .

We should therefore expect the  $T_{par}$  errors to be slightly inflated versions of  $\epsilon \, rr(T_{\epsilon})$ . This is exactly what we observe in our data. The signs of the  $\epsilon \, rr(T_{\epsilon})$  and  $\epsilon \, rr(T_{par})$  agreed in every workload, and  $|\epsilon \, rr(T_{par})|$  always exceeded  $|\epsilon \, rr(T_{\epsilon})|$ . The largest  $T_{par}$  error was - 18.9% (for Cholesky with six PEs) and the overall mean  $|\epsilon \, rr(T_{par})|$  was 1.16% (N = 63).

The distinction between the two groups of applications is even clearer from the  $T_{par}$  errors than it was from  $\epsilon \, rr(\, T_{\epsilon} \,)$ . The ratio of the group variances of  $n \, \epsilon \, rr(\, T_{pa\, r} \,)$  was 1600, as opposed to 190 for  $n \, \epsilon \, rr(\, T_{\epsilon} \,)$ . Each of the four large-error applications had one or more workloads with  $|\epsilon \, rr(\, T_{pa\, r} \,)\,| > 2\%$ , but among the small-error applications  $|\epsilon \, rr(\, T_{pa\, r} \,)\,|$  never exceeded 0.3%.

The  $T_f$  errors were larger than the  $T_{pa}$ , errors in 41 out of 63 workloads.  $|Err(T_f)|$  exceeded 10% in 16 out of 63 workloads. The  $T_f$  errors in PThor were especially remarkable. The largest  $T_f$  error was 4850.%, for PThor with two processors. This one workload was responsible for most of the  $err(T_f)$  in PThor. All but one of the remaining PThor workloads had  $err(T_f) = 0$ .

Negative  $T_f$  errors outnumbered positive ones by **30**: **26**, and **Dynamic Barnes** was the only application which showed significant sign-bias in  $\epsilon rr(T_f)$ .

For the remainder of this report, it is important to remember that errors are reported for complete workloads, including the initialization stage. For larger workloads, the initialization stage would be insignificant, so many of the errors would be larger by a factor of two or so.

#### 4.3.3 Cycle counts

The cycle count, C, is another important simulation result, closely related to  $T_{\bullet}$ . We define C to be the sum (over all PEs) of cycles consumed by the workload. C includes idle cycles (latencies due to synchronization, memory references, and address translation) but not the cycles consumed by inactive PEs during serial stages of the computation. In to Figure 4.1,  $T_{\epsilon}$  is the length of the curve along the z-axis, while C corresponds to the area under the curve. We can approximate the area by  $T_{\epsilon} + (p-1)T_{par}$ , so C is closely related to both  $T_{\epsilon}$  and  $T_{par}$ .

Table 4.3 summarizes the effect of trace-driven simulation on C'.

|                | - 1000                  |                 |  |  |

|----------------|-------------------------|-----------------|--|--|

| Application    | mean $ \epsilon rr(C) $ | $\max  err(C) $ |  |  |

| MP3D           | 0.04%                   | -0.12%          |  |  |

| Dynamic MP3D   | 0.13%+                  | <i>10.25</i> %  |  |  |

| Barnes         | 0.03%                   | - <b>0.07</b> % |  |  |

| Dynamic Barnes | 1.38%+                  | +2.11%          |  |  |

| Cholesky       | <b>10.2</b> %-          | - 18.2%         |  |  |

| LocusRoute     | 1.19%                   | -3.23%          |  |  |

| PThor          | 1.08%+                  | +2.39%          |  |  |

Table 4.3: Cycle Count Errors with  $\mathcal{G}_{ideal}$  for 2 to 10 PEs.

Except for the **Cholesky** workloads, err(C') resembled  $err(T_{par})$  and, to a lesser extent,  $err(T_{\epsilon})$ . There was a mild (r = 0.422) correlation between nerr(C) and  $nerr(T_{\epsilon})$  and a slightly stronger one [r = 0.4971 between nerr(C') and  $nerr(T_{par})$ . In 49 out of 63 workloads, err(C') fell somewhere between  $err(T_{\epsilon})$  and  $err(T_{par})$ . **The** largest C error was -18.2% (for **Cholesky** with ten **PEs**) and the overall mean |err(C')| was 2.00% (N = 63).

The applications fell into the **same** groups as before, and the ratio of the normalized error variances was 5200.

The sign of err(C) was biased toward the positive side by a **40**: 23 margin.

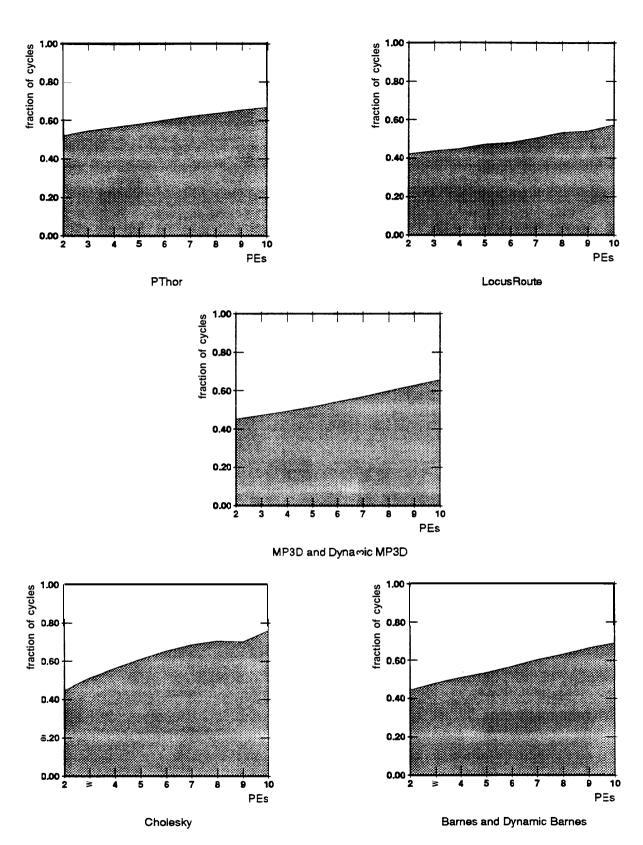

#### 4.3.4 Instructions vs. idle cycles

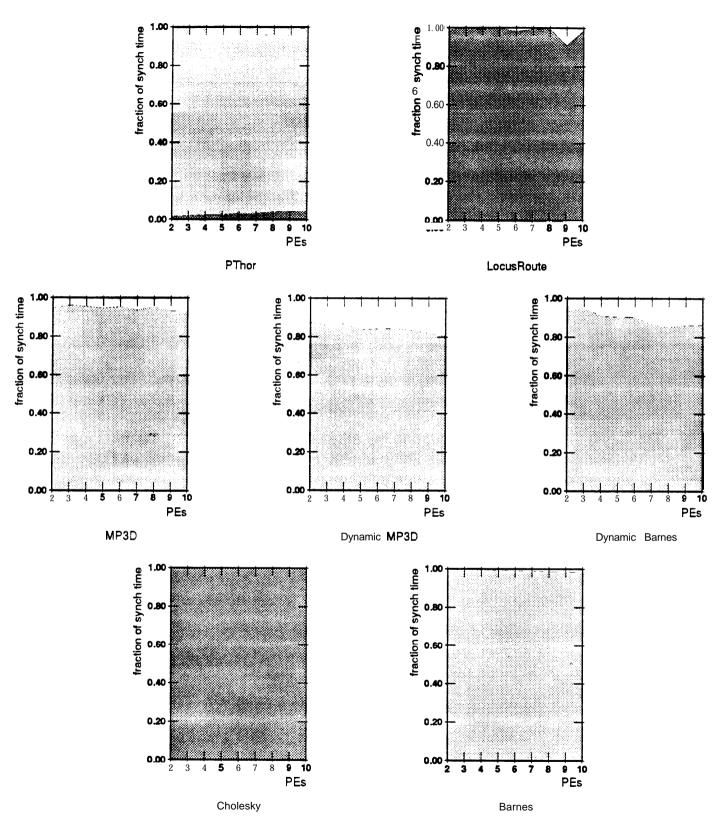

We now decompose C as the sum of the dynamic instruction count, I, and the number of idle cycles, C - I. This is possible because all instructions execute in a single cycle, and we do not count instructions that **perform** synchronization.

Figure 4.3 illustrates this decomposition of C for each workload. Idle time represented 42.1% to 75.8% of C in our workloads, and the idle fraction, (C - I)/C, grew at a fairly uniformly rate with respect to the number of **PEs**. The plot of idle fraction versus p was similar for all seven applications.

Table 4.4 presents our measurements of the errors in  $\boldsymbol{I}$  and  $C - \boldsymbol{I}$ .

| Table 4.4: | Cvcle | Count | Errors | with $G_{idea}$                        | for | 2 1 | to | 10 | PEs. |

|------------|-------|-------|--------|----------------------------------------|-----|-----|----|----|------|

| 1 44010    |       |       |        | ······································ | 1   | _   |    |    |      |

| Application    | mean $ \epsilon rr(I) $ | mean $ \epsilon rr(C-I) $ |

|----------------|-------------------------|---------------------------|

| MP3D           | 0.03%                   | 0.10%                     |

| Dynamic MP3D   | 0.04%                   | 0.24%+                    |

| Barnes         | 0.00%                   | 0.05 %                    |