# SYNTHESIS TECHNIQUES FOR BUILT-IN SELF-TESTABLE DESIGNS

LaNae Joy Avra

CRC Technical Report No. 94-6 (CSL TR 94-633) July 1994

## CENTER FOR RELIABLE COMPUTING

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, CA 94305-4055

Copyright © 1994 by LaNae Joy Avra All Rights Reserved

# SYNTHESIS TECHNIQUES FOR BUILT-IN SELF-TESTABLE DESIGNS

## A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

LaNae Joy Avra

June 1994

## **ABSTRACT**

Hardware synthesis techniques automatically generate a structural hardware implementation given an abstract description of the behavior of the design. Many different hardware designs can implement a given behavioral description, a subset of which also meet specified requirements such as cost, performance, and testability. Existing synthesis techniques typically use minimum cost or maximum performance as the primary criteria for selecting the best hardware implementation. This dissertation describes new synthesis techniques whose primary objective is to satisfy requirements associated with a specific built-in self-test (BIST) architecture.

The use of BIST techniques (design techniques that allow a circuit to test itself) has long been recognized as a means to reduce system life cycle test and maintenance costs. BIST provides shorter test times and allows the use of low-cost test equipment during all stages of the product life: production test, acceptance test, field maintenance, and failure diagnosis. However, hardware overhead, performance degradation, and increased design time are often cited as reasons for the limited use of BIST. When BIST techniques are used, they are often added after the system logic has been designed. At this point, system logic features that may increase BIST overhead or reduce the effectiveness of the BIST operation are expensive to change.

This dissertation describes new synthesis techniques that address two of the major issues associated with BIST: 1) implementation costs due to increased design time, area overhead, increased power consumprtion, and performance degradation and 2) test effectiveness due to system logic design decisions. Our synthesis procedures use criteria associated with the specified BIST architecture to guide the generation of the system logic, allowing for design decisions that reduce BIST overhead and improve BIST effectiveness. In particular, the primary objective of our synthesis techniques is to generate low-cost, built-in self-testable designs that are free of the types of system bistable dependencies that can reduce the effectiveness of the embedded, multiple input signature registers (MISRs) that are used to perform BIST operations.

One type of system bistable dependency that can be a problem for BIST occurs in a self-adjacent register, where the register inputs are a function of its outputs. To address this problem, we have developed a high-level synthesis technique that minimizes the number of self-adjacent registers in the generated design without increasing the latency of the design. Some system bistable dependencies provide opportunities for sharing BIST and scan logic with system logic, reducing the area and improving the performance of the design. We show that introducing certain, beneficial types of *scan dependence* in the design can increase logic sharing opportunities and can improve BIST effectiveness. Other BIST design techniques attempt to avoid all types of scan dependence. We have developed a logic synthesis technique that analyzes the system bistable dependencies, then arranges the bistables in the MISR to maximize beneficial

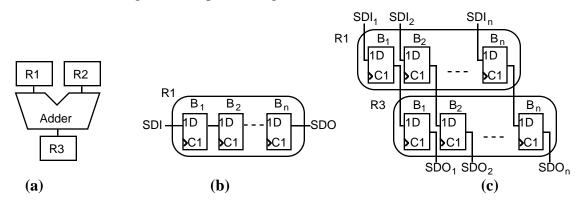

scan dependence. For data path logic, we have developed a new scan path architecture, called *orthogonal scan path*, for which the shift direction is orthogonal to the shift direction in traditional scan paths. We show that using an orthogonal scan path increases the number of beneficial scan dependencies between data path logic bistables. We have implemented our synthesis-for-BIST techniques in a computer-aided design system, which serves as a platform for experimentation with existing and future synthesis-for-test techniques.

## **ACKNOWLEDGMENTS**

I express my deepest appreciation to my adviser, Edward J. McCluskey, for his guidance, support, and instruction during my time at Stanford. His suggestions have greatly enhanced both the technical content and the presentation of this dissertation, and his enthusiasm for learning and for teaching have been a constant source of inspiration.

I am most grateful to my colleagues at the Center for Reliable Computing who have provided many hours of discussions, manuscript editing, and companionship: Piero Franco, Hong Hao, Siyad Ma, Samy Makar, Samiha Mourad, Rob Norwood, Nirmal Saxena, Alice Tokarnia, and Nur Touba. I especially wish to thank the CRC visitors who have worked so diligently on the Odin software: Jean-Charles Giomi, Francoise Martinolle, Laurent Gerbaux, Dave Brokaw, and Gian Luigi Sartori. Their contributions have greatly improved the quality and usefulness of the tool. Many thanks, also, to Siegrid Munda for her expert administrative support.

I would like to thank my associate adviser, Giovanni De Micheli, for his useful comments and suggestions for developing the high-level synthesis algorithms. Thanks, also, to the members of his group that provided support and technical advice: David Ku, Michiel Ligthart, Polly Siegel, and Jerry Yang.

I greatly appreciate the industry feedback and software donations provided by Dave Coelho and Rick Lazansky of Vantage Analysis Systems, Inc., and Jacob El Ziq of Compass Design Automation.

Finally, I wish to thank my family. I thank my husband, Rick, for his support, encouragement, and technical advice. His expertise in the design, validation, testing, and manufacturing of VLSI chips provided invaluable real-world perspective to the material in this dissertation. I am grateful to both Rick and my daughter, Tamsin, for their patience, understanding, and unconditional love, without which this work would not have been possible. Thanks, also, to my parents for instilling in me the self-confidence necessary to pursue my goals and for providing me with every opportunity to learn.

This work was supported in part by Digital Equipment Corporation, Low-End Diagnostics Group, and in part by the Innovative Science and Technology Office of the Strategic Defense Initiative Organization and administered through the Office of Naval Research under Contract Nos. N00014-85-K-0600 and N00014-92-J-1782, and in part by the National Science Foundation under grant Nos. MIP-8709128 and MIP-9107760.

## **TABLE OF CONTENTS**

| Αł | ostrac                                   | t                                            | i   |  |  |

|----|------------------------------------------|----------------------------------------------|-----|--|--|

| A  | know                                     | ledgments                                    | iii |  |  |

| Li | st of T                                  | Γables                                       | vi  |  |  |

| Li | st of I                                  | llustrations                                 | vii |  |  |

| 1  | Intr                                     | oduction                                     | 1   |  |  |

|    | 1.1                                      | Motivation                                   | 1   |  |  |

|    | 1.2                                      | Contributions                                | 3   |  |  |

|    | 1.3                                      | Outline                                      | 4   |  |  |

| 2  | Em                                       | bedded BIST Architectures                    | 5   |  |  |

|    | 2.1                                      | Parallel BIST Architecture                   | 6   |  |  |

|    | 2.2                                      | Circular BIST Architecture                   | 12  |  |  |

|    | 2.3                                      | Reconfigurable Register Design               | 13  |  |  |

| 3  | Allocation and Binding for Parallel BIST |                                              |     |  |  |

|    | 3.1                                      | High-Level Synthesis Tasks                   | 17  |  |  |

|    | 3.2                                      | Register Conflict Graph                      | 18  |  |  |

|    | 3.3                                      | Implementation and Results                   | 20  |  |  |

|    | 3.4                                      | Contributions                                | 22  |  |  |

| 4  | Syn                                      | thesis for Scan Dependence                   | 24  |  |  |

|    | 4.1                                      | Scan Dependence                              | 25  |  |  |

|    | 4.2                                      | Synthesis for Scan Dependence                | 28  |  |  |

|    | 4.3                                      | Implementation and Results                   | 30  |  |  |

|    |                                          | 4.3.1 Area and Delay Results                 | 31  |  |  |

|    |                                          | 4.3.2 Fault Simulation Results               | 34  |  |  |

|    | 4.4                                      | Contributions                                | 35  |  |  |

| 5  | Sca                                      | n Dependence in Data Path Logic              | 36  |  |  |

| -  | 5.1                                      | Orthogonal Scan Path Architecture            | 37  |  |  |

|    | 5.2                                      | Scan Dependence Functions in Data Path Logic | 37  |  |  |

|    | 5.3                                      | Results                                      | 39  |  |  |

|    | 5.4                                      | Contributions                                | 40  |  |  |

| 6  | Synthesis-for-Test Design System41       |                                              |     |  |  |

|    | 6.1                | Overview41                      |  |  |  |  |

|----|--------------------|---------------------------------|--|--|--|--|

|    | 6.2                | Design System Input and Output  |  |  |  |  |

|    |                    | 6.2.1 VHDL Descriptions         |  |  |  |  |

|    |                    | 6.2.2 Component Library         |  |  |  |  |

|    | 6.3                | Data and Control Flow Graphs    |  |  |  |  |

|    | 6.4                | High-Level Synthesis Techniques |  |  |  |  |

| 7  | Concluding Remarks |                                 |  |  |  |  |

| Re | References         |                                 |  |  |  |  |

## **LIST OF TABLES**

| Table 2-1 | Test session register configurations for design example in [Hudson 87] 8                              |

|-----------|-------------------------------------------------------------------------------------------------------|

| Table 3-1 | Register binding algorithm for parallel BIST register conflict graph21                                |

| Table 3-2 | Comparison of synthesis procedures on Tseng [Tseng 86] and DiffEq [Paulin 89a] data flow descriptions |

| Table 4-1 | Area and delay for shaded logic in Fig. 4-3 based on data in [LSI 91] 28                              |

| Table 4-2 | Scan dependence classification of decomposed Boolean equations29                                      |

| Table 4-3 | Bistable characteristics for circular BIST benchmark circuits                                         |

| Table 4-4 | Area and overhead for area-optimized circular BIST benchmark circuits 32                              |

| Table 4-5 | Delay and overhead for delay-optimized circular BIST benchmark circuits. 33                           |

| Table 4-6 | Layout area overhead for area-optimized circular BIST benchmark circuits.33                           |

| Table 4-7 | Fault simulation results for circular BIST benchmark circuits                                         |

| Table 5-1 | System equations for data path registers that benefit from scan dependence.38                         |

| Table 5-2 | Data path design examples with orthogonal scan path and circular BIST 40                              |

| Table 6-1 | Example VHDL behavioral description                                                                   |

| Table 6-2 | Example VHDL structural description of data path logic generated by Odin.44                           |

## **LIST OF ILLUSTRATIONS**

| Figure 1-1 | Test scenario for life cycle of integrated circuit part.                                           | . 1            |

|------------|----------------------------------------------------------------------------------------------------|----------------|

| Figure 1-2 | Built-in self-test configuration.                                                                  | . 2            |

| Figure 2-1 | Parallel BIST architecture                                                                         | . 7            |

| Figure 2-2 | Self-adjacent register implemented with CBILBO                                                     | 9              |

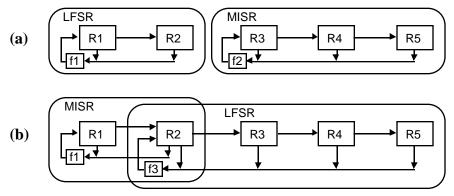

| Figure 2-3 | LFSR and MISR configurations for Fig. 2-1                                                          | 11             |

| Figure 2-4 | Circular BIST architecture                                                                         | 13             |

| Figure 2-5 | Reconfigurable register                                                                            | 14             |

| Figure 2-6 | MISR error capture capabilities                                                                    | 15             |

| Figure 3-1 | High-level synthesis example                                                                       | 17             |

| Figure 3-2 | Register conflict graph example                                                                    | 19             |

| Figure 3-3 | Testability conflict edges                                                                         | 20             |

| Figure 4-1 | Embedded MISR with scan dependence                                                                 | 25             |

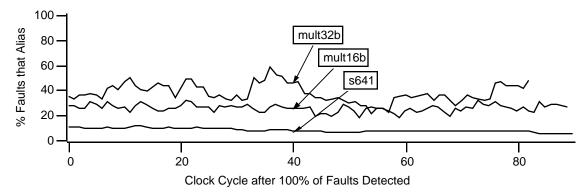

| Figure 4-2 | Fault simulation results of BIST operation of circular BIST circuits with maximum scan dependence. | 26             |

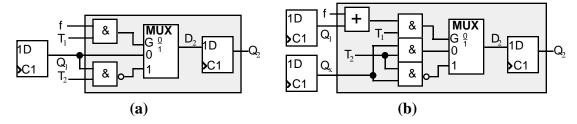

| Figure 4-3 | Scan dependence solutions for $Z2 = Q1 + f$                                                        | 28             |

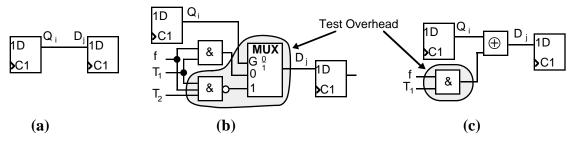

| Figure 4-4 | Beneficial scan dependence implementations                                                         | 29             |

| Figure 5-1 | Orthogonal scan path example                                                                       | 37             |

| Figure 5-2 | Live variable motion                                                                               | 10             |

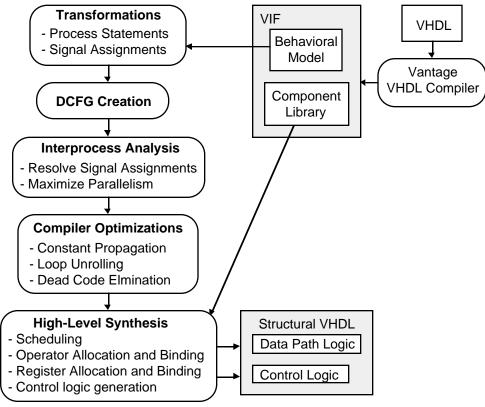

| Figure 6-1 | Odin design system overview.                                                                       | 12             |

| Figure 6-2 | DCFG example                                                                                       | 15             |

| Figure 6-3 | Data flow graphs                                                                                   | <del>1</del> 6 |

| Figure 6-4 | High-level synthesis example                                                                       | 18             |

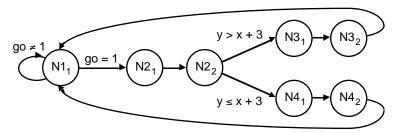

| Figure 6-5 | Control logic state machine description for Fig. 6-2.                                              | 19             |

## 1 INTRODUCTION

## 1.1 MOTIVATION

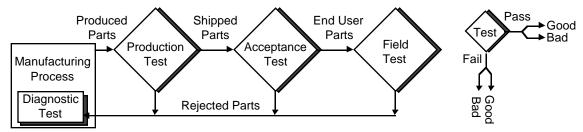

An integrated circuit part such as a chip, multi-chip module, board, or system must be thoroughly tested in order to determine whether or not it is defective. Different types of tests are applied to the part at various times in its life cycle to detect different types of failures. For example, the part manufacturer applies production tests to the part to determine whether or not there are manufacturing defects, whereas the end user applies field tests to identify failures caused by stressful conditions in the operating environment (e.g., radiation, vibration) or reliability problems within the part (e.g., electromigration). Figure 1-1 illustrates a possible test scenario that encompasses the entire life cycle of an integrated circuit part. In the first phase of testing, the manufacturer applies production tests in order to prevent parts with manufacturing defects from being shipped to the customer. Next, the customer applies acceptance tests to determine whether or not the parts should be placed in field operation. Acceptance tests identify parts that have been damaged during shipping, or parts that don't meet customer specifications. Parts that pass acceptance testing are then assembled into systems and placed into field operation. Field tests are applied to a system that has failed in the field in order to identify the defective component parts that must be replaced. For each testing phase in this particular scenario, diagnostic tests are applied to rejected parts to determine the cause of failure in an effort to improve the manufacturing process.

**Figure 1-1** Test scenario for life cycle of integrated circuit part.

The goal in any test scenario is to apply the most rigorous tests possible, tests for which the number of good parts that fail, but most importantly, the number of bad parts that pass (called *test escapes*) are minimized. The quality of a test is a function of how many of the targeted failures are detected by the test, how well the targeted failures represent actual defects, and how easily the part can be tested. As integrated circuit parts become more and more complex, dense, and inaccessible, rigorous testing becomes less feasible unless design practices are used that allow for easier testing. These design practices, called *design-for-testability (DFT)* techniques, simplify the test development task by constraining the design to easy-to-test structures, thereby making it easier to generate and apply tests that detect all of the targeted failures. However,

rigorous testing can still be impractical due to the expensive external test equipment required to apply the tests.

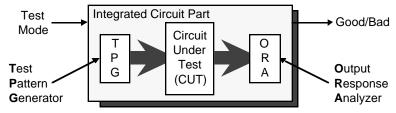

Built-in self-test (BIST) is a DFT technique that allows a part to test itself. BIST techniques such as those described in [McCluskey 85], [McCluskey 86], [Bardell 87], and [Abramovici 90] have long been recognized as a means to reduce life cycle test and maintenance costs by embedding external tester features, such as *test pattern generation (TPG)* and *output response analysis (ORA)*, into the part that contains the *circuit under test (CUT)* (Fig. 1-2). BIST can provide shorter test times than externally-applied tests and allows the use of low-cost test equipment during all stages of the product life including system debug, production test, field maintenance, and failure diagnosis. Even though industry use of BIST techniques is becoming more common [Gelsinger 86], [Lake 86], [Nozuyama 88], [Ratiu 90], [Starke 90], [Bardell 91], [Illman 91], [Preissner 92], [Sinaki 92], [Yokomizo 92], [Bonnenberg 93], [Broseghini 93], [Gage 93], [Langford 93], [Patel 93], area overhead, performance degradation, and increased design time are often cited as reasons for the limited use of BIST.

**Figure 1-2** Built-in self-test configuration.

Traditional design methods separate the tasks of system logic design (design of the logic that implements the normal operation of the part) and BIST logic design. During the initial stages of design, system logic issues take priority over BIST issues such as selection of the most appropriate BIST technique for the system logic, BIST logic implementation, and evaluation of the BIST operation. As the design progresses, time-to-market pressures often cause the postponement of BIST design until the end of the design process at which point little time is available to address BIST issues, and any mistakes made are expensive to fix. Automated *BIST synthesis* techniques, where BIST logic is added or a BIST architecture is selected after the system logic has been designed [Abadir 85], [Zhu 88], are valuable in that they reduce the design time and the number of design mistakes by automating the BIST logic design process. Unfortunately, earlier system logic design decisions can reduce the effectiveness and increase the overhead of the implemented BIST technique.

Hardware synthesis techniques automatically generate a structural hardware implementation given an abstract description of the behavior of the part. Many different hardware designs can implement a given behavioral description, a subset of which also meet specified requirements such as cost, performance, and testability. Current research in hardware synthesis techniques

(e.g., [Brayton 87], [McFarland 88], [De Micheli 94]) typically focuses on the use of minimum area or maximum performance as the primary criteria for selecting the best hardware implementation. Some synthesis-for-testability techniques attempt to generate the lowest-cost, highest-performance implementation that also meets certain specified testability requirements such as irredundant combinational logic [Hachtel 89], [Bryan 89] or robustly delay-fault testable logic [Devadas 90], [Jha 92]. Testable logic is a necessary, but not sufficient, condition for highquality BIST operation. This dissertation describes new synthesis-for-BIST techniques that have the primary objective of satisfying requirements associated with a specific BIST architecture when generating the system logic structural implementation. Cost is minimized and performance is maximized to the extent that BIST requirements are not compromised. These new synthesis techniques address two of the major issues associated with generating self-testable designs: 1) increased implementation costs due to added design time, area overhead, and performance degradation, and 2) reduced self-test effectiveness due to system logic design decisions. Considering BIST issues during system logic synthesis allows for the generation of system logic that is optimized for a particular BIST architecture and that can be more effectively tested by the BIST operation.

## 1.2 CONTRIBUTIONS

This dissertation describes new synthesis techniques that use the requirements of the implemented BIST architecture to guide the synthesis of the system logic in order to improve the effectiveness of the self-test operation and to reduce the BIST logic overhead. In developing these new techniques, we have focused on embedded BIST architectures because they provide opportunities for the sharing of system and test logic. Logic sharing makes it possible to reduce the area overhead of the BIST logic and improve the performance of the generated design. In particular, the following are the contributions of this dissertation:

- We have developed and implemented a *new register allocation and binding algorithm* for high-level synthesis that generates designs with a minimum number of self-adjacent registers [Avra 91]. This technique is used for parallel BIST architectures.

- We have formalized the concept of *scan dependence* in embedded BIST architectures and have presented fault simulation data showing that, if ignored, scan dependence can significantly reduce the effectiveness of the BIST operation [Avra 94a].

- We have identified certain types of scan dependence that can be beneficial to the design and have developed *new output response analysis (ORA) structures* that take advantage of them [Avra 93], [Avra 94a].

- We have developed and implemented a *new synthesis for scan dependence technique* that maximizes the amount of beneficial scan dependence in the design [Avra 93], [Avra 94a].

- We have developed a *new scan path architecture* that increases the amount of beneficial scan dependence in data path logic [Avra 92].

- We have implemented a *synthesis-for-test computer-aided design tool* that includes the synthesis techniques described in this dissertation and generates a self-testable design given a behavioral VHDL description of the design [Avra 90], [Avra 94b].

## 1.3 OUTLINE

This dissertation is organized as follows. In Sec. 2, we describe in detail the operation and implementation of two embedded BIST architectures: parallel BIST and circular BIST. Parallel BIST is the target BIST architecture of the synthesis technique described in Sec. 3, and circular BIST is the target architecture of the synthesis techniques described in Secs. 4 and 5. We also describe a register design that can be used in the parallel and circular BIST architectures. We use this register design to illustrate the BIST concepts and design techniques presented in the remainder of the dissertation. In general, each section discussing the contributions of this dissertation (Secs. 3-6) is a summary of material previously published by the author and included in Appendices I-IV. Section 3 contains a description of a high-level synthesis technique that generates the system logic for a parallel BIST architecture. In Sec. 4, we define scan dependence and illustrate its advantages and disadvantages with a simple example. We then describe a synthesis technique that arranges the system bistables into MISRs such that beneficial scan dependence is maximized. We illustrate the technique using the circular BIST architecture. In Sec. 5, we show that beneficial scan dependence can be increased in data path logic when an orthogonal scan path configuration is used. Section 6 is an overview of the synthesis-for-test computer-aided design tool the implements the described synthesis techniques. The tool is intended to be a platform for experimentation with existing and future test synthesis and synthesis-for-test techniques. Section 7 concludes this dissertation.

## **2 EMBEDDED BIST ARCHITECTURES**

BIST techniques are implemented by including a *test pattern generator (TPG)* and *output response analyzer (ORA)* in the part (e.g., chip, multi-chip module, board) that contains the *circuit under test (CUT)*. During BIST operation, the TPG applies test patterns to the inputs of the CUT and the ORA captures the response of the CUT to those test patterns. Typically, the TPG and ORA are implemented such that they automatically generate patterns and analyze responses at test time so that the test pattern and test response storage requirements are minimized. *Embedded* BIST architectures use reconfigurable system bistables to implement both the normal system operation and the BIST TPG and ORA operations. Since the BIST logic is combined with the system logic, opportunities exist for synthesis technique to generate hardware that can be shared by both the system and test operations, resulting in improved performance and reduced cost. However, in addition to system logic issues such as performance and cost, the synthesis technique must be capable of addressing issues that affect the quality of the BIST operation, issues such as self-test time, and TPG and ORA effectiveness. We discuss these issues in this section.

Most BIST architectures use pseudo-random pattern generators such as linear feedback shift registers (LFSRs) or weighted random pattern generators [Waicukauski 89] to perform TPG operations. The TPGs are called *pseudo-random* because, while they generate patterns with characteristics that are similar to randomly-generated patterns, their behavior is deterministic. The test is therefore repeatable, and the results of the test can be compared with expected results. In order to test for all possible combinational faults (e.g., single and multiple stuck-at faults) within an n-input cone of combinational logic in the CUT, where a cone of logic is delimited by starting at a combinational logic output (either a primary output or a bistable input) and tracing backwards through the gates to each input (either a primary input or a bistable output), a TPG must be capable of applying all 2<sup>n</sup> possible test patterns. To test for pattern-dependent faults [Hao 91], delay faults, or faults that cause combinational logic to behave sequentially, the TPG may be required to generate multiple sequences of the 2<sup>n</sup> possible patterns. Faults that affect more than one cone of logic (e.g., a bridging fault between the inputs of two logic gates that are in different cones) can be detected if a single TPG covers multiple cones. We evaluate the TPGs generated by our synthesis techniques in terms of their ability to generate 2<sup>n</sup> different test patterns for each *n*-input cone of logic. Even though it may be determined that not all of the  $2^n$ test patterns need to be applied during BIST operation, it is difficult to determine a priori which subset of test patterns will be required to provide a high fault coverage test for each CUT. Therefore, the TPGs must be designed such that they could generate all 2<sup>n</sup> different test patterns if necessary. This is known as the "philosophy of possible exhaustion" [Bardell 87]. Also, if all

2<sup>n</sup> test patterns can be generated, one can use probabilistic models, based on the number of test patterns applied and the detectabilities of the faults in the CUT, to estimate the fault coverage provided by the TPG [McCluskey 88], thus avoiding expensive and time-consuming fault simulations.

An ideal ORA is capable of analyzing the response of each test pattern applied to the CUT. In practice, of course, this is not feasible for a built-in ORA. Instead, most BIST architectures use ORAs, such as *multiple-input signature registers (MISRs)*, that compact the test response, resulting in a loss of information. Thus, under certain error conditions, the test response of a faulty CUT may be indistinguishable from the test response of a fault-free CUT, a phenomenon known as *aliasing*. Our synthesis techniques assume that MISRs are used as the ORAs in the implemented BIST architecture and attempt to minimize the amount of aliasing in those MISRs.

In this section, we describe two embedded BIST architectures, parallel BIST and circular BIST, and discuss BIST-related synthesis issues for each. In Sec. 2.1, we describe parallel BIST, emphasizing often-overlooked implementation complexities that must be addressed by the synthesis technique so that it generates a design that performs a high-quality BIST operation. The synthesis technique described in Sec. 3 generates designs with parallel BIST architectures. The synthesis techniques described in Secs. 4 and 5, though applicable to all BIST architectures that use embedded MISRs, generate designs that use the circular BIST technique. We describe the assumed circular BIST architecture in Sec. 2.2. In Sec. 2.3, we describe one possible implementation of a reconfigurable register design for embedded BIST architectures. The register is configured as a normal parallel load register for system operation. During BIST operation, it is configured as either a maximum-length LFSR for test pattern generation or as a MISR for output response analysis.

## 2.1 PARALLEL BIST ARCHITECTURE

The parallel BIST architecture [Konemann 80] is an embedded BIST architecture in which system registers are reconfigured to perform either LFSR or MISR operations during BIST. The *built-in logic block observer (BILBO)* register [Konemann 79] is often used to implement the system registers in parallel BIST architectures. A possible implementation of the BILBO register is described in detail in Sec. 2.3. Variations of the parallel BIST architecture are discussed in [McCluskey 81], [Krasniewski 85], [Hudson 87].

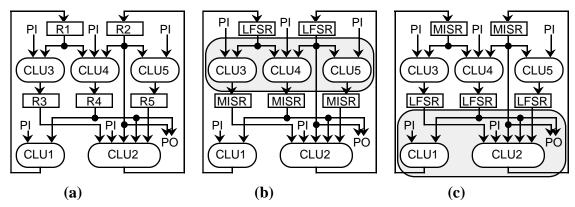

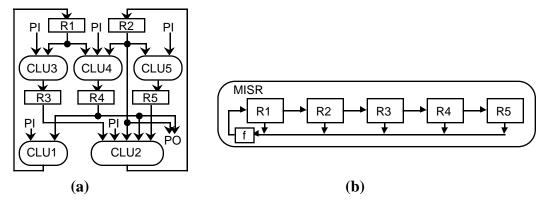

Figure 2-1 illustrates how the parallel BIST architecture is used to test a block of data path logic that consists of five registers (*R1-R5*), five combinational logic units (*CLU1-CLU5*), primary input signals (*PI*), and primary output signals (*PO*). During normal operation (Fig. 2-1a), the system registers are configured to load data from the outputs of the CLUs. Prior to performing BIST operation, the system bistables must begin in a known state. This can be

accomplished by configuring the registers into a scan path and shifting in known data or by configuring the registers to perform a reset operation. During BIST operation, the registers are configured as either LFSRs or MISRs. At each clock cycle, pseudo-random test patterns are applied to the inputs of the CLUs by the LFSRs at the same time that the test results (the outputs of the CLUs) are compacted in the MISRs. Figures 2-1b and 2-1c represent two different *test sessions* of the BIST operation, where each test session consists of a unique mapping of registers to LFSRs and MISRs. *CLU3*, *CLU4*, and *CLU5* are tested during the first test session (Fig. 2-1b), and *CLU1* and *CLU2* are tested during the second test session (Fig. 2-1c). After each test session, the registers are configured into a serial shift path so that the test results can be shifted out and compared with expected results. This comparison can be performed either by external test equipment or by BIST control logic that may be included as part of a test access port controller [IEEE 90]. The BIST control logic also generates signals that control the configuration of the system registers.

**Figure 2-1** Parallel BIST architecture: (a) normal operation; (b) first test session configuration; (c) second test session configuration.

One advantage of the parallel BIST architecture is that it supports at-speed self-test operation: a new test pattern is applied to the CUT at each clock cycle. At-speed operation means that the parallel BIST technique may be able to detect some delay faults. Another advantage of this technique is that, since each system register can be reconfigured as either an LFSR or a MISR, multiple CLUs can be tested in parallel, reducing the total self-test time.

We define an ideal parallel BIST architecture as one for which the system bistables can be arranged into LFSRs and MISRs such that, for each n-input CLU in the design,  $2^n$  different test patterns can be applied to the CLU inputs during the same test session that the CLU outputs are captured in a MISR. Unfortunately, due to the inter-connectedness of the system bistables in typical designs, many test sessions may be required to test all of the CLUs in an ideal parallel BIST architecture. For example, register interconnection data and test session configurations for a twenty-three register, parallel BIST design is provided in [Hudson 87]. This information is

shown in a different form in Table 2-1, which lists which registers, numbered 1 through 23, are configured as LFSRs and MISRs for each test session. We assume that any CLU feeding a register that is configured as a MISR during a given test session is tested during that test session. For example, during test session 10, the CLUs that feed registers 9 and 16 are tested by test patterns supplied by registers 10, 12, and 17. Registers 9, 16, 10, and 12 in Table 2-1 could be interconnected in the same manner as registers *R4*, *R3*, *R1*, and *R2*, respectively, in Fig. 2-1a. The design requires a minimum of twelve different test sessions, where an average of 1.75 registers are configured as MISRs and 13.9 registers are configured as LFSRs in each test session. The high number of test sessions corresponds to the low degree of self-test parallelism in the design.

**Table 2-1** Test session register configurations for design example in [Hudson 87].

| <b>Test Session</b> | MISRs    | LFSRs                                             |

|---------------------|----------|---------------------------------------------------|

| 1                   | 3,13*,17 | 1,2,4,5,6,7,8,9,10,11,12,14,15,16,19,20,21,22,23  |

| 2                   | 19,20*   | 1,2,4,5,6,7,8,9,10,11,13,14,15,16,21,22,23        |

| 3                   | 23*      | 1,2,4,5,6,7,8,9,10,11,12,13,14,15,16,19,20,21,22  |

| 4                   | 6*,10*   | 1,2,4,5,7,8,9,11,13,14,15,16,19,20,21,22,23       |

| 5                   | 5*,11*   | 1,2,4,6,7,8,9,10,13,14,15,16,20,21,22,23          |

| 6                   | 4,12*    | 1,2,3,7,8,9,10,11,13,14,15,16,17,19,20,21,22,23   |

| 7                   | 18       | 1,2,4,6,7,8,9,10,11,12,13,14,15,16,19,20,21,22,23 |

| 8                   | 14*      | 1,2,4,7,8,9,10,11,13,15,16,20,21,22,23            |

| 9                   | 7*,8*    | 1,2,9,10,13,14,15,16,20,21,22,23                  |

| 10                  | 9,16     | 10,12,17                                          |

| 11                  | 1*       | 13,20,21,23                                       |

| 12                  | 2*,15*   | 1,13,14,16,20,21,22,23                            |

<sup>\*</sup>Self-adjacent register configured as a MISR during test.

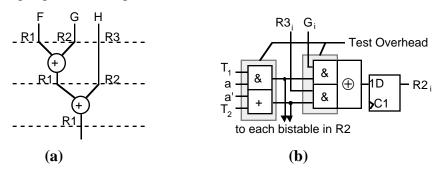

One of the barriers to implementing an economical parallel BIST architecture is self-adjacent registers. A *self-adjacent register*, marked with an asterisk in Table 2-1, is one in which at least one output of the register feeds through either a direct connection or combinational logic to at least one input of the same register (see register *R2* in Fig. 2-1a). If the self-adjacent register is configured as an LFSR in order to supply test patterns to the CLU during BIST operation, the response of the CLU cannot be observed. A self-adjacent register that is implemented with a *concurrent built-in logic block observer (CBILBO)* design as described in [Wang 86] is able to simultaneously perform both the LFSR and MISR operations because it has two sets of bistables. CBILBO register operation for a self-adjacent register is illustrated in Fig. 2-2. During normal operation, only one of the sets of CBILBO bistables is used (Fig. 2-2a). During BIST operation, the set of bistables that drives the system logic is configured into an LFSR, and the other set of

bistables is configured into a MISR. Unfortunately, the prevalence of self-adjacent registers combined with the higher hardware overhead for CBILBOs (CBILBO registers are approximately 1.75 times the size of BILBO registers) greatly increases the BIST overhead for the design in Table 2-1. When CBILBOs are not used, a self-adjacent register can be configured as a MISR during BIST operation. The MISR then provides test patterns to the CLU at the same time that it captures the response of the CLU (e.g., register *R2* configured as a MISR in Fig. 2-1c). Since the state of the self-adjacent MISR depends upon its previous state and the CLU, there is no guarantee that it can generate an exhaustive set of test patterns for the CLU. Also, the CLU can adversely affect the output response capabilities of the self-adjacent MISR, as was noted by Hudson [Hudson 87] for the case when a shift operation is implemented in the CLU. We discuss the effect of the CLU on the MISR output response capabilities in detail in Sec. 4.

**Figure 2-2** Self-adjacent register implemented with CBILBO: (a) normal operation; (b) BIST operation.

In an effort to solve this problem, high-level synthesis techniques have been proposed that generate data path logic with a minimum number of self-adjacent registers [Avra 91], [Papachristou 91], [Mujumdar 92]. These synthesis techniques are among the first to use BIST criteria to guide the high-level synthesis of the system logic. High-level synthesis techniques that only consider area and performance during synthesis tend to generate system logic with a large number of self-adjacent registers. For example, five of the eight registers in the *Tseng* example generated by the synthesis technique described in [Tseng 86] and four of the five registers in the *DiffEq* example generated by the synthesis technique described in [Paulin 89a] are self-adjacent. The synthesis technique described in [Avra 91] generated system logic with only one self-adjacent register for both of these examples. For both examples, when CBILBO registers are used for the self-adjacent registers, the synthesis-for-BIST technique generated lower-cost parallel BIST implementations than the synthesis techniques that do not consider BIST.

Another implementation difficulty of the ideal parallel BIST architecture is determining the arrangement of system bistables into LFSRs during each test session so that each CLU tested during that test session could receive an exhaustive set of test patterns. The simplest arrangement is to configure each n-bit system register as a maximum-length LFSR, which

generates  $2^n$ -1 different test patterns (logic can easily be added to the LFSR so that it generates all  $2^n$  different patterns [McCluskey 86]). This is not an acceptable solution, however, when a single CLU is fed by multiple system registers (see *CLU2* in Fig. 2-1). In this case, the total number of different test patterns, P, that can be applied to the CLU is the least common multiple of the periods of the individual LFSRs. For n maximum-length LFSRs, where LFSR i has  $b_i$  bistables and  $b_1 \le b_2 \le ... \le b_n$ :

$$\begin{array}{lll} (2^{b_n} \mbox{--}1) & \leq & P & \leq & (2^{b_1} \mbox{--}1) \ (2^{b_2} \mbox{--}1) \ (2^{b_3} \mbox{--}1) \ ... \ (2^{b_{n-1}} \mbox{--}1) \\ & P & < & 2^{b_1 + b_2 + b_3 + ... + b_{n-1}} \end{array}$$

The maximum value for P can only be achieved when the periods of the n LFSRs are mutually prime. In data path logic, where a single CLU is often fed by n b-bit system registers, we have the worst-case scenario:

$$P = 2^b - 1 << 2^{nb}$$

A better solution for providing a nearly exhaustive set of test patterns to each CLU is to configure the bistables on the inputs of each CLU being tested during a given test session into a single, maximum-length LFSR. Figure 2-3 illustrates this solution by showing one way to configure the registers of Fig. 2-1 into LFSRs and MISRs for each of the two required test sessions. During the first test session (Fig. 2-1b and 2-3a), registers R1 and R2 are configured into a single maximum-length LFSR in order to provide an exhaustive set of test patterns to CLU4. Registers R3, R4, and R5 are configured into a MISR to capture the output responses of CLU3, CLU4, and CLU5. During the second test session (Fig. 2-1c and 2-3b), R2, which is implemented with a CBILBO register, is configured with R3, R4, and R5 into a single LFSR in order to test CLU2. The second set of R2 bistables are configured with R1 into a MISR, which captures the output responses of CLU1 and CLU2. The signal lines in Fig. 2-3 represent the additional interconnections required for BIST operation. Each block of feedback logic (f1, f2, f3)and f3) consists of a tree of one or more exclusive-OR gates that implements the polynomial of the associated LFSR or MISR. The arrangement of the registers during BIST operation ( $R1 \rightarrow$  $R2 \rightarrow R3 \rightarrow R4 \rightarrow R5$ ) was chosen because it minimizes the amount of BIST interconnection and feedback logic.

**Figure 2-3** LFSR and MISR configurations for Fig. 2-1: (a) first test session; (b) second test session.

Unfortunately, the parallel BIST architecture illustrated in Fig. 2-3 can, in practice, be extremely complicated and costly to implement. In our discussion, we have ignored how to configure LFSRs to drive the input signals (primary input signals and control signals) of the data path logic during BIST operation. Considering these signals could greatly complicate the configurations of the LFSRs during each test session, particularly if a single state machine generates all of the control signals for the data path logic. Also, Fig. 2-1 is a relatively simple data path design example. More complicated data path designs, or non-BIST scan path arrangement requirements, such as minimizing test time for deterministic stuck-at tests as described in [Gupta 91] and [Narayanan 92], could greatly increase both the hardware overhead and the total self-test time for the parallel BIST architecture. Table 2-1 provides a hint of how complicated the parallel BIST architecture could be for a real design. For example, test session seven in Table 2-1 shows that the combinational logic feeding register 18 is fed by the outputs of 19 different registers. When these 19 registers are configured into a single, maximum-length LFSR, 2<sup>b</sup>-1 different test patterns are applied to the CLU, where b is the total number of bistables in the 19 registers. Subsets of these 19 registers must be combined with other registers to create the LFSRs for the remaining eleven test sessions. As the number of test sessions increases, the BIST control logic and the LFSR interconnection logic for the design can become very complicated.

The synthesis technique described in Sec. 3 addresses one of the implementation difficulties of parallel BIST architectures by generating system logic that has a minimum number of self-adjacent registers. However, the data in Table 2-1 shows that complicated register interconnections in the system logic can greatly complicate the LFSR configurations required for a parallel BIST architecture. This issue must be addressed by synthesis techniques before extensive use of the parallel BIST architecture is practical. To that end, we have investigated more simple TPG and ORA configuration schemes, such as those found in the circular BIST

architecture. The circular BIST architecture is described in Sec. 2.2 and new synthesis techniques for this architecture are described in Secs. 4 and 5.

## 2.2 CIRCULAR BIST ARCHITECTURE

Circular BIST is a low overhead, embedded BIST architecture that provides at-speed self-test operation. Circular BIST has lower area overhead than parallel BIST because it has simpler BIST control logic and interconnection logic, which also simplifies and speeds the implementation process. The circular BIST architecture was first introduced as simultaneous self-test (SST) by Bardell and McAnney [Bardell 82]. It was later described in slightly different forms by Stroud [Stroud 88] and Krasniewski [Krasniewski 89]. Figure 2-4 illustrates the circular BIST architecture for the data path logic in Fig. 2-1a. During BIST operation, all system bistables are configured into a single MISR as shown in Fig. 2-4b. At each clock cycle during BIST operation, the outputs of all CLUs in the design are captured in a single MISR, and the outputs of the MISR provide test patterns to the CLUs. The circular BIST architecture requires little BIST control logic since there is only one test session during which a single MISR simultaneously performs the TPG and ORA operations. The problems of register self-adjacency and LFSR configuration discussed in Sec. 2.1 for the parallel BIST architecture are not applicable to circular BIST. However, since the CLUs in the circular BIST architecture are simultaneously tested by a single, self-adjacent MISR, the pattern generation and response analysis capabilities of self-adjacent MISRs must be analyzed to ensure an effective self-test operation. These issues are discussed in Sec. 4.1 and are addressed by our synthesis for scan dependence techniques described in Secs. 4.2 and 5.

Since slightly different versions of the circular BIST architecture have been described in [Bardell 82], [Stroud 88], and [Krasniewski 89], we state here our assumptions concerning the circular BIST architecture implemented in our synthesized designs. First, we assume that all bistables in the design are included in the MISR during BIST operation. Other architectures ([Krasniewski 89], [Stroud 88]) allow some bistables to be configured in the normal mode during BIST operation in order to reduce the BIST overhead, but there is evidence that this can reduce the observability of the logic feeding those bistables [Kim 88]. Second, we assume that every system bistable is an edge-triggered flip-flop that can be configured to perform normal, shift, and MISR operations. A reset mode of operation is optional since the bistables can be controlled through the shift mode of operation. Using flip-flops simplifies the discussion of the synthesis techniques. Similar synthesis techniques can be applied if the double-latch, level-sensitive scan design method is used to implement the system bistables as described in [Bardell 82], but we do not discuss these techniques in this dissertation. Finally, we assume that the MISR feedback logic is simply a direct connection from the output of the last bistable in the MISR to the input of

the first bistable. A reconfigurable register design that supports these operations is described in Sec. 2.3.

Figure 2-4 Circular BIST architecture: (a) normal operation; (b) BIST register configuration.

## 2.3 RECONFIGURABLE REGISTER DESIGN

The distinguishing characteristic of embedded BIST architectures is that the system bistables can be configured to perform both normal operation (parallel load) as well as test operations such as serial shift, TPG, and ORA. The test operations that must be supported by each bistable depend upon the embedded BIST architecture used. The Circular Self-Test Path architecture [Krasniewski 89], for example, does not require that the system bistables perform a serial shift operation. The built-in logic block observer (BILBO) register [Konemann 79] is often used in embedded BIST architectures and implements normal, synchronous reset, serial shift, TPG, and ORA modes of operation.

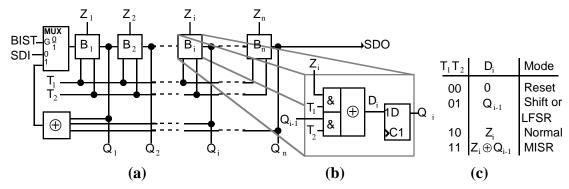

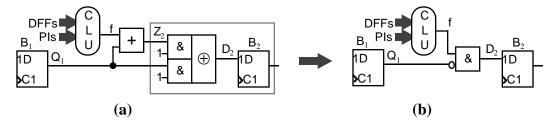

Figure 2-5 illustrates a reconfigurable register design that can be used for both the parallel BIST and circular BIST architectures. The register implementation is not necessarily optimal. Its purpose is to more easily illustrate the BIST operations. In Secs. 4 and 5, we use Fig. 2-5 to illustrate scan dependence and our synthesis techniques. Figure 2-5a shows the register configuration, where each bistable in the register is implemented as shown in Fig. 2-5b. The bistable could also be implemented with a dual-port latch, such as the design specified for the SST technique [Bardell 82]. The  $Q_{i-1}$  input to the first bistable (bistable  $B_1$ ) in the register is determined by BIST mode select signal BIST, and is either the scan data input (SDI) signal for shift operation or the output of the MISR feedback logic for MISR operation or LFSR operation. For circular BIST architectures, since a separate TPG operation is not required, signal BIST can be replaced by signal  $T_1$ , resulting in four possible modes of operation: reset, shift, normal, and MISR. Test mode select signals  $T_1$  and  $T_2$  determine the D input to each bistable in the register, as specified in Fig. 2-5c, where  $Z_i$  is the system logic input to bistable  $B_i$ .

**Figure 2-5** Reconfigurable register: (a) bistable interconnections; (b) reconfigurable bistable; (c) modes of operation.

For circular BIST architectures and for parallel BIST architectures with self-adjacent registers that are not implemented with CBILBOs (i.e., for self-adjacent MISRs), the MISR operation must simultaneously provide both sufficient test patterns and accurate output response analysis. It has been proven that, when the Z inputs are independent of the state of an n-bit MISR, the MISR generates test patterns that are similar in behavior to random patterns [Krasniewski 89], [Kim 88]. Specifically, as P goes to infinity, where P is the number of test patterns applied during BIST operation, the probability of the MISR being in any one of the  $2^n$  possible states is  $2^{-n}$ . The Z inputs to a self-adjacent MISR, however, are a function of the state of the MISR. Simulation results presented in [Kim 88] and [Stroud 88] indicate that the MISR test pattern characteristics are not significantly different from random patterns when the Z inputs depend upon the state of the MISR. It is not clear whether a MISR implemented with a primitive polynomial [Kim 88] produces any better patterns than a MISR implemented with a single  $Q_n$  feedback connection [Krasniewski 89].

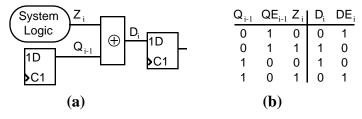

Figure 2-6a shows a portion of the reconfigurable register during MISR operation to illustrate its error capture capabilities. During MISR operation, the input to each bistable,  $D_i$ , is the exclusive-OR of the output of the previous bistable in the MISR,  $Q_{i-1}$ , and the system logic input to the bistable,  $Z_i$ . At each clock cycle, an error in either  $Z_i$  or  $Q_{i-1}$  is observable at  $D_i$  (i.e., captured in bistable  $B_i$ ) regardless of the state of the error-free signal. Figure 2-6b is a truth table for signals  $D_i$  ( $D_i = Q_{i-1} \oplus Z_i$ ) and  $DE_i$  ( $DE_i = QE_{i-1} \oplus Z_i$ ), where  $QE_{i-1}$  is the faulty version of signal  $Q_{i-1}$ . Figure 2-6b shows that, regardless of the state of signal  $Z_i$ ,  $D_i$  differs from  $DE_i$ , so when  $Z_i$  is fault-free, an error in  $Q_{i-1}$  is always captured in bistable  $B_i$ . Because the exclusive-OR operation is symmetric, the same is true when  $Q_{i-1}$  is fault-free and  $Z_i$  is faulty. However, errors in both signals  $Z_i$  and  $Q_{i-1}$  in a single clock cycle are not observable at  $D_i$ . Thus, once captured in a bistable of the MISR, an error is transferred from one bistable ( $Q_{i-1}$ ) to the next ( $Q_i$ ) at each clock cycle as long as it is not masked by a simultaneous error in the corresponding system logic

input signal  $Z_i$ . In addition, the error may be transferred to other bistables in the MISR through the MISR feedback logic or, if the MISR is self-adjacent, through the system logic.

Figure 2-6 MISR error capture capabilities: (a) MISR configuration; (b) error response.

## 3 ALLOCATION AND BINDING FOR PARALLEL BIST

The interconnection of system logic registers can greatly affect the area overhead of parallel BIST architectures and the effectiveness of the TPGs and ORAs as was shown in Sec. 2.1. System register interconnect is an issue that must be addressed during high-level synthesis, when variables in the behavioral description are mapped to specific registers in the structural description. Little work has been done in the area of high-level synthesis-for-testability. Recently, high-level synthesis algorithms for non-scan and partial-scan architectures have been given [Lee 93]. These algorithms are not well-suited for parallel BIST architectures, however, because they favor the generation of self-adjacent registers since self-adjacent bistables, which can occur in self-adjacent registers, are considered easier to test by sequential automatic test pattern generation tools [Cheng 89]. High-level synthesis procedures that discourage the generation of self-adjacent registers are described in [Avra 91], [Papachristou 91], and [Mujumdar 92]. The technique described in [Papachristou 91] generates data path logic with no self-adjacent registers, but may increase the latency of the functional operation in order to do this. The module and register binding algorithm given in [Mujumdar 92] discourages, but does not prevent, the generation of self-adjacent registers.

This section provides an overview of our high-level synthesis-for-BIST technique, first described in [Avra 90], that takes as input a scheduled data flow description of the system logic and, without increasing the latency of the description, generates a parallel BIST data path structure with a minimum number of self-adjacent registers. A more detailed description of the technique is given in [Avra 91]. The synthesis procedure consists of first mapping the input data flow description to a register conflict graph. The nodes of the graph are then colored using a node coloring algorithm that is guided by design implementation costs such as interconnection area and multiplexer size. Finally, the colored graph is mapped to hardware. A simple constraint imposed on the register conflict graph prevents the register binding algorithm from creating self-adjacent registers in the generated data path logic, thereby reducing the area overhead of the parallel BIST architecture when self-adjacent registers are implemented with CBILBO registers. We also incorporate a novel register allocation technique that allows the register binding algorithm increased flexibility in synthesizing an efficient hardware implementation.

Section 3.1 is background material and provides an overview of the operations performed during high-level synthesis. In Sec. 3.2, we describe the register conflict graph, focusing on the features that make our high-level synthesis procedure unique. Section 3.3 describes the register binding algorithm that is implemented in our synthesis tool and compares designs generated by our tool with designs generated by other synthesis techniques. Section 3.4 summarizes our contributions in high-level synthesis for parallel BIST.

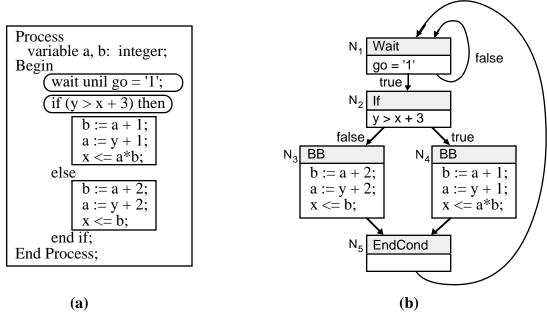

## 3.1 HIGH-LEVEL SYNTHESIS TASKS

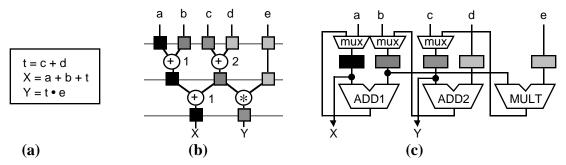

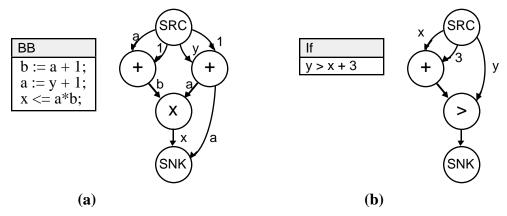

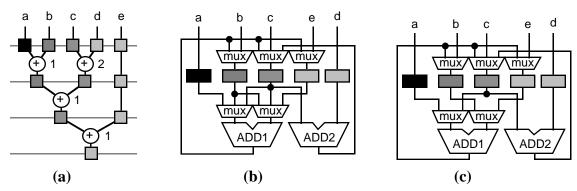

Register binding is one of several tasks performed during high-level synthesis. We use Fig. 3-1 to illustrate the high-level synthesis operations of scheduling, allocation, and binding. More detailed information on these and additional high-level synthesis operations can be found in [De Micheli 94]. High-level synthesis operations are typically applied to a data flow graph (Fig. 3-1b) that represents a behavioral description of the system operation (Fig. 3-1a). Nodes and edges in the data flow graph correspond to operations and variables, respectively, in the behavioral description. Scheduling consists of assigning the operations in the data flow description to execute in certain clock cycles. For example, Fig. 3-1b shows that two addition operations are performed in the first clock cycle, while one addition and one multiplication are performed in the second clock cycle. Clock cycle boundaries in Fig. 3-1b are delimited by dotted lines. The scheduling algorithm may generate a schedule that, given a hardware constraint, executes in a minimum number of clock cycles or that, given a timing constraint, requires a minimum number of function blocks to perform the operations in the behavioral description. Allocation consists of determining the number of hardware resources necessary to implement the data flow description. Two addition function blocks (for  $+_1$  and  $+_2$ ), one multiplication function block, and five registers (represented by squares on the edges of the graph) have been allocated for the data flow graph in Fig. 3-1b. During binding, operations in the data flow graph are mapped to specific instances of hardware function blocks (ADD1, ADD2, and MULT in Fig. 3-1c), variables that exist at clock cycle boundaries are mapped to registers (rectangles in Fig. 3-1c), and multiplexers and buses are generated to accommodate the required flow of data. Our register allocation and binding techniques differ from existing techniques in two ways: 1) we incorporate a simple constraint in the binding of variables to registers such that the number of self-adjacent registers is minimized, and 2) to compensate for this constraint, we incorporate a register allocation technique that increases the flexibility of the register binding procedure.

**Figure 3-1** High-level synthesis example: (a) data flow description; (b) scheduled, bound data flow graph; (c) data path logic.

## 3.2 REGISTER CONFLICT GRAPH

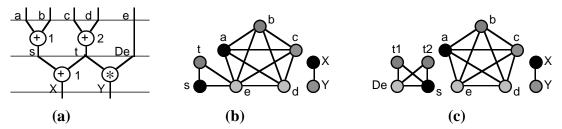

Our register allocation and binding operations are applied to a register conflict graph data structure. Each node in the register conflict graph represents an edge from the data flow graph that crosses a clock cycle boundary. An edge between two nodes in the register conflict graph indicates that the two variables associated with those nodes cannot be stored in the same register. Register binding consists of assigning a color to each of the nodes in the register conflict graph such that adjacent nodes have different colors. All nodes with the same color can be mapped to the same register in the final implementation. This is analogous to the techniques described in [Tseng 86] and [Paulin 89b], where a register compatibility graph is created, clique partitioning is performed, and all nodes in the same clique are assigned to the same register. Figure 3-2b illustrates the typical conflict graph-based register allocation and binding procedures for the data flow graph of Fig 3-1b. Figure 3-2a is the same data flow graph as Fig. 3-1b except that the register binding information (colored squares on clock cycle boundaries) has been removed. Nine nodes, corresponding to data flow graph variables a, b, c, d, e, s, t, X, and Y, are created in the register conflict graph. Edges are added between nodes whose variables cannot be assigned to the same register. For example, variables a, b, c, d, and e all exist at the first clock cycle in the data flow graph and must therefore all be assigned to different registers, so their nodes form a clique in the register conflict graph. One possible coloring of the register conflict graph is shown in Fig. 3-2b, where the different colors correspond to different registers in the structural implementation.

We define register allocation as the method used to determine how many nodes to create in the register conflict graph. Our register allocation procedure is illustrated in Fig. 3-2c and is unique in that it creates multiple nodes in the register conflict graph for a single variable in the data flow graph under three conditions: delayed values, multiple targets, and multiple sources. We do this in order to increase the flexibility of the register binding algorithm in mapping variables to non-self-adjacent registers. For the delayed values situation, a node is added to the register conflict graph for each clock cycle in a variable's lifetime. This means that the variable could be transferred from one register to another rather than held in a single register for its entire lifetime as most register allocation techniques require. The delayed values allocation scheme is illustrated by nodes e and De in Fig. 3-2c, which both represent variable e from the data flow description. Note that there is no edge between nodes e and s since they exist at different clock cycles, but there is an edge between nodes De and s. The delayed values consideration is an extension of the technique first introduced in [Paulin 89b], where it was shown that when a register is allocated for the first clock cycle of a variable's lifetime, and another register is allocated for the remaining clock cycles of its lifetime, interconnect cost can sometimes be reduced. Multiple targets means that a node is added to the register conflict graph for each

output of an operation that crosses a clock cycle boundary. For example, nodes t1 and t2 in Fig. 3-2c both represent the variable t in Fig. 3-2a. Node t1 represents the input to the addition operation, and node t2 represents the input to the multiplication operation. No edge is added between nodes t1 and t2 because they could be assigned to the same register since they represent the same variable. *Multiple sources*, which is not shown in Fig. 3-2c, is similar to multiple targets except that a node is added to the conflict graph for each operation input that represents a single variable. This situation occurs when the input to an operation is assigned a value in multiple, mutually-exclusive branches of a conditional statement. The multiple sources situation is described in detail in [Avra 91].

**Figure 3-2** Register conflict graph example: (a) data flow graph from Fig. 3-1b; (b) typical register conflict graph; (c) our register conflict graph.

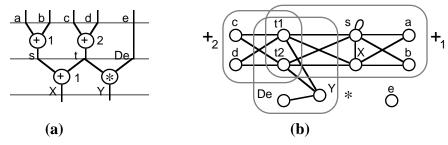

Conflict edges are edges in the register conflict graph that specify that the variables associated with the adjacent nodes cannot be assigned to the same register. We call the edges shown in the register conflict graphs in Fig. 3-2 schedule conflict edges because the conflict that exists between the adjacent nodes is due to the schedule specified for the data flow graph. Schedule conflict edges therefore maintain the functionality of the system logic. Our register binding algorithm is unique in that we include an additional type of conflict edge in the register conflict graph that maintains the testability of the generated system logic. Testability conflict edges are added between two nodes when one node represents a variable that is an input to a function block and the other node represents a variable that is an output of the same function block. For example, Fig. 3-3b is the register conflict graph for Fig. 3-3a, showing just the testability conflict edges for the three function blocks,  $+_1$ ,  $+_2$ , and \*. Note that an edge is added between nodes a and s and between nodes a and X because both s and X are outputs of the same function block. Node e has no adjacent testability conflict edges because it is not an input or an output of any function block. Testability conflict edges require that the inputs and the outputs of a function block be assigned to different registers, and this guarantees that no self-adjacent registers will be synthesized. One situation requires the use of a self-adjacent register: when two operations in consecutive clock cycles in the data flow graph are assigned to a single function block and the output of one operation is the input to the other (see variable s in Fig. 3-3a). In this case, the node that is associated with both the input and the output of the function block is

identified by a self-edge in the register conflict graph and must be assigned to a CBILBO register.

**Figure 3-3** Testability conflict edges: (a) data flow graph; (b) register conflict graph with testability conflict edges.

Cost edges are weighted edges that are added between certain compatible nodes (nodes that do not already have a conflict edge between them) in the register conflict graph, and are used to guide the graph coloring algorithm toward the lowest-cost design. A positive weight is assigned to the cost edge if it is not advantageous to assign the same color to the adjacent nodes, and a negative weight is assigned if it is advantageous. For example, negative-weight cost edges are added between nodes a and t1, and between b and t1 in Fig. 3-3b because they represent variables that are inputs to a single function block  $(+_1)$  in two different clock cycles. Interconnection and multiplexer cost will be lower if these two variables are assigned to the same register.

## 3.3 IMPLEMENTATION AND RESULTS

We have implemented our register allocation and binding algorithm for parallel BIST designs in the synthesis tool described in Sec. 6. Given a behavioral VHDL [IEEE 88] description of the design, the tool first creates a data flow graph, then performs scheduling and operation allocation and binding as described in Sec. 6.4, and then creates the register conflict graph as described in Sec. 3.2. We have implemented a modified version of the Brelaz node coloring algorithm [Turner 88] to perform the register binding operation. The pseudo-code for our register binding algorithm is given in Table 3-1. The algorithm attempts to color the nodes in the register conflict graph with the minimum number of colors in order to minimize the number of registers in the generated design. Since solving the general node coloring problem is NP-complete, we use heuristics to sort the uncolored nodes, then color the node with the highest priority. The node to be colored is assigned the same color as a node that is adjacent via the lowest, negative-weight cost edge. If the node to be colored has no adjacent negative-weight cost edges, the algorithm tries to assign it the same color as a non-adjacent node. After a node is colored, the characteristics of the adjacent, uncolored nodes are updated, and all of the uncolored nodes are sorted to find the next node to color.

**Table 3-1** Register binding algorithm for parallel BIST register conflict graph.

Color\_Nodes (Register Conflict Graph)

While (Some Nodes Uncolored) do

Sort Uncolored Nodes According to:

1. Has Self-Adjacent Constraint Edge

2. Has Least Number Available Colors

3. Has Most Constraint Edges

4. Has Least Sum Of Cost Edges

Select Highest-Priority Node

Color With Lewest Cost Adjacent Color

Color With Lowest-Cost Adjacent Color Update Uncolored, Adjacent Nodes end While

The data path logic in Fig. 3-1c was generated by applying the register binding algorithm in Table 3-1 to the data flow graph in Fig. 3-1b. As shown by the self-edge in Fig. 3-3b, node s must be assigned to a self-adjacent register, so the register binding algorithm selected node s to color first. The register associated with node s (and nodes s and s since they were assigned the same color) is implemented as a CBILBO register and is the only self-adjacent register in the generated design.

Table 3-2 compares the results of our register allocation and binding technique, called *RALLOC*, with the results published in [Tseng 86], [Pangrle 88], [Paulin 89a], and [Papachristou 91] for two design examples, *Tseng* [Tseng 86] and *DiffEq* [Paulin 89a]. The design cost estimates of the synthesized hardware are based on the number of self-adjacent (*SA*) registers, non-self-adjacent (*NSA*) registers, multiplexer inputs (*mux*), interconnections (*int*), and control signals (*ctl*), and are computed as follows:

$$cost_1 = 14 \cdot (NSA \text{ reg}) + 14 \cdot (SA \text{ reg}) + mux + int + ctl$$

$cost_2 = 20 \cdot (NSA \text{ reg}) + 35 \cdot (SA \text{ reg}) + mux + int + ctl$

For the first design cost estimate,  $cost_1$ , all registers have the same cost. This represents the cost of data path logic with no BIST or scan circuitry. The second design cost estimate,  $cost_2$ , represents the cost of a parallel BIST implementation of the data path logic. In this case, non-self-adjacent registers are implemented with the register design shown in Fig. 2-5a, which is estimated to be approximately 20 times the cost of a multiplexer input, and self-adjacent registers are implemented with the higher-cost CBILBO register.

The goal of the synthesis techniques presented in [Tseng 86], [Pangrle 88], and [Paulin 89a] is to minimize the area of the generated data path logic. Since they do not consider testability during the synthesis process, their implementations, understandably, have a higher number of self-adjacent registers, which partially accounts for the higher values for cost<sub>2</sub> in Table 3-2. Both our synthesis technique and the technique described in [Papachristou 91] attempt to minimize the cost of the design while preventing the generation of self-adjacent registers. By comparing our

technique with techniques that do not consider testability, we show the difference between *synthesis-for-BIST*, where the design is optimized for a particular BIST architecture, and *BIST synthesis*, where BIST circuitry is added to a design that has been synthesized for area and performance.

For both examples in Table 3-2, our technique generated the lowest-cost parallel BIST implementation  $(cost_2)$ . Our technique also generated designs with the minimum number of registers, showing that the additional testability constraint edge in the register conflict graph did not require an increase in the number of registers for these examples. The  $cost_1$  column in Table 3-2 shows that, if parallel BIST is not implemented, the costs of the data path designs generated by our technique are comparable to the costs of the other designs.

**Table 3-2** Comparison of synthesis procedures on *Tseng* [Tseng 86] and *DiffEq* [Paulin 89a] data flow descriptions.

| Name                 | NSA reg | SA reg | mux | int | ctl | cost <sub>1</sub> | cost <sub>2</sub> |

|----------------------|---------|--------|-----|-----|-----|-------------------|-------------------|

| Tseng                |         |        |     |     |     |                   |                   |

| [Tseng 86]           | 3       | 5      | 15  | 31  | 23  | 181               | 304               |

| [Pangrle 88]         | 4       | 3      | 11  | 26  | 18  | 153               | 240               |

| [Papachristou<br>91] | 8       | 0      | 12  | 28  | 20  | 172               | 220               |

| RALLOC               | 4       | 1      | 16  | 29  | 21  | 136               | 181               |

| DiffEq               |         |        |     |     |     |                   |                   |

| [Pangrle 88]         | 1       | 5      | 17  | 34  | 23  | 158               | 269               |

| [Paulin 89a]         | 1       | 4      | 19  | 35  | 24  | 148               | 238               |

| RALLOC               | 4       | 1      | 22  | 38  | 27  | 157               | 202               |

## 3.4 CONTRIBUTIONS

We have developed and implemented a new register allocation and binding technique that generates data path logic optimized for the parallel BIST architecture given a scheduled, operation-bound data flow description of the design. A simple testability constraint edge added to the register conflict graph is used to guarantee that the generated data path logic has a minimum number of self-adjacent registers. This testability requirement can be easily adapted to existing register allocation and binding procedures. We have also developed and implemented new techniques for register allocation (delayed values, multiple targets, and multiple sources) that provide the register binding procedure increased flexibility in synthesizing an efficient hardware implementation while minimizing the number of self-adjacent registers.

Results show that, when the parallel BIST architecture is used, addressing register self-adjacency during high-level synthesis results in a lower-cost design. For both examples evaluated, our technique synthesized the lowest-cost, parallel BIST design. In addition, for both

examples, if parallel BIST is not implemented, the costs of the data path designs generated by our technique are comparable to the costs of the other designs. This shows that, even if BIST and scan circuitry is not included in the design, minimizing the number of self-adjacent registers during synthesis does not necessarily increase, and may even reduce, the cost of the generated data path logic.

## 4 SYNTHESIS FOR SCAN DEPENDENCE

Performance degradation, area overhead, and *test transparency* (the fraction of defects not detected by the test) are three issues that must be addressed when synthesizing a built-in self-testable design. The register allocation and binding technique described in Sec. 3 reduces the area overhead of a parallel BIST design without increasing test transparency or the number of clock cycles required to execute the data path function. However, since there is additional BIST logic associated with each system register in the data path, the clock period may have to be increased, resulting in slower performance. In this section, we describe a new synthesis technique, applied to the bistables in the design, that relies on the sharing of system logic and test logic to reduce the area and improve the performance without increasing the test transparency of BIST architectures, such as circular BIST and parallel BIST, that make use of embedded MISRs. This technique was first described in [Avra 93]. A more detailed description of the technique is given in [Avra 94a].

The goal of our synthesis technique is to arrange the system bistables into scan paths so that some of the BIST and scan logic is shared with the system logic. Logic sharing is possible when scan dependence is introduced in the design. Other BIST design techniques attempt to avoid all types of scan dependence because it can increase the test transparency of embedded MISRs. We show that introducing certain types of scan dependence in embedded MISRs can reduce the overhead and the test transparency, and we describe a synthesis technique that maximizes the amount of this beneficial scan dependence. The synthesis technique first analyzes the CUT feeding the MISR, then based on the CUT function, it modifies the MISR function in order to reduce the amount of aliasing during BIST operation. We have implemented this synthesis technique in our synthesis-for-test design tool (described in Sec. 6) and we present fault simulation, layout area, and delay results for circular BIST versions of benchmark circuits that have been synthesized with our technique.

Section 4.1 provides a formal definition of scan dependence and includes design examples that illustrate its advantages and disadvantages. In Sec. 4.2, we describe design techniques for beneficial scan dependence and show how to introduce it in the design by arranging the system bistables into MISRs. Section 4.3 contains fault simulation and overhead results of several benchmark circuits generated with our synthesis technique and optimized for the circular BIST architecture described in Sec. 2.2. Section 4.4 summarizes our contributions in the area of scan dependence.

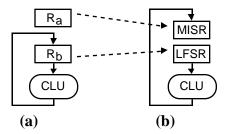

## 4.1 SCAN DEPENDENCE

A system bistable  $B_i$  that can be reconfigured to perform scan operation is *scan dependent* if and only if its system logic input signal,  $Z_i$ , is functionally dependent on the bistable that immediately precedes it in the scan path. For example, assume that the system logic input to bistable  $B_5$  is the function  $Z_5 = Q_1 Q + Q_2 Q_4$ . If any of the bistables  $B_1 - B_4$  immediately precede  $B_5$  in the scan path, bistable  $B_5$  is scan dependent on that preceding bistable. If, however, bistable  $B_6$  immediately precedes  $B_5$  in the scan path,  $B_5$  is not scan dependent since  $Z_5$  is not a function of  $Q_6$ . Bhatia [Bhatia 93] showed that scan dependence can be used to reduce the area overhead of certain types of scan architectures. We showed in [Avra 93] that some types of scan dependence can be used to reduce the overhead and improve the effectiveness of embedded BIST architectures.