# Center for Reliable Computing

# TECHNICAL REPORT

# Testing Digital Circuits for Timing Failures by Output Waveform Analysis

#### Piero Franco

94-9

(CSL TR # 94-637)

September 1994

# **Center for Reliable Computing**

**ERL 460**

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, California 943054055

#### **Abstract:**

This technical report contains the text of Piero Franco's thesis "Testing Digital Circuits for Timing Failures by Output Waveform Analysis". The thesis appendices have appeared as CRC Technical Reports 94-4 and 94-5, and are not included here.

#### **Funding:**

This work was supported in part by the Chamber of Mines of South Africa, in part by the Innovative Science and Technology Office of the Strategic Defense Initiative Organization and administered through the Office of Naval Research under Contracts No. N00014-85-K-0600 and N00014-92-J-1782, in part by the National Science Foundation under Grants No. MIP-8709128 and No. MIP-9107760, and in part by Hughes Aircraft Co.

# **ABSTRACT**

Delay testing is done to ensure that a digital circuit functions at the designed speed. Delay testing is complicated by test invalidation and fault detection size. Furthermore, we show that simple delay models are not sufficient to provoke the longest delay through a circuit. Even if all paths are robustly tested, path delay testing cannot guarantee that the circuit functions at the desired speed.

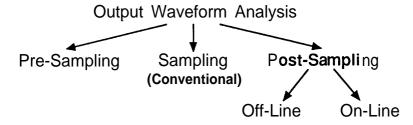

Output Waveform Analysis is a new approach for detecting timing failures in digital circuits. Unlike conventional testing where the circuit outputs are sampled, the waveform between samples is analyzed. The motivation is that delay changes affect the shape of the output waveform, and information can be extracted from the waveform to detect timing failures. This is especially useful as a Design-for-Testability technique for Built-In Self-Test or pseudo-random testing environments, where delay tests are difficult to apply and test invalidation is a problem.

Stability Checking is a simple form of Output Waveform Analysis. In a fault-free circuit, the outputs are expected to have reached the desired logic values by the time they are sampled, so delay faults can be detected by observing the outputs for any changes after the sampling time. Apart from traditional delay testing, Stability Checking is also useful for on-line or concurrent testing under certain timing restrictions. A padding algorithm was implemented to show that circuits can be efficiently modified to meet the required timing constraints.

By analyzing the output waveform before the sampling time, circuits with timing flaws can be detected even before the circuit fails. This is useful in high reliability applications as a screening technique that does not stress the circuit, and for wear-out prediction.

A symbolic waveform simulator has been implemented to show the benefits of the proposed Output Waveform Analysis techniques. Practical test architectures have been designed, and various waveform analyzers have been manufactured and tested. These include circuits implemented using the Stanford BiCMOS process, and a design implemented in a 25k gate Test Evaluation Chip Experiment.

# **ACKNOWLEDGMENTS**

This dissertation describes a new approach for detecting timing failures in digital circuits performed at Stanford University. I am deeply grateful to my advisor, Prof. Edward J. McCluskey, without whose guidance and support this work would not have been possible. I am also grateful to Prof. Giovanni De Micheli, my associate advisor, and Prof. Dwight. G. Nishimura, my committee chairman, for reading my dissertation, and Prof. Oyekunle Olukotun for being the final member of my committee.

I would like to thank my colleagues at the Center for Reliable computing for their help: LaNae Avra, Hong Hao, Siyad Ma, Samy Makar, Samiha Mourad, Rob Norwood, Nirmal Saxena, Alice Tokamia, and Nur Touba. I also thank Siegrid Munda for her administrative support, and often "helping me catch the DHL truck."

I would like to thank Dr. E. Eichelberger for helpful discussions in the early phase of this work.

I thank the Center for Reliable and High-Performance Computing, University of Illinois at Urbana-Champaign, for their hospitality during my stay.

I would like to thank the many people who contributed to the Test Evaluation Chip Experiment. In particular, I would like to thank Robert Stokes for his work on the architectural and detailed design of the Test Chip, and Mike Sarvian for his help in writing and debugging the test program.

I wish to thank Mamma, Papà, Laura, Nonna and Pamela for their love, support, encouragement, understanding, and patience. I dedicate this dissertation to them.

I am grateful to the Chamber of Mines of South Africa for making it possible for me to come to Stanford, and supporting me for the first year.

This work was also supported in part by the Innovative Science and Technology Office of the Strategic Defense Initiative Organization and administered through the Office of Naval Research under Contracts No. N00014-85-K-0600 and N00014-92-J-1782, in part by the National Science Foundation under Grants No. MIP-8709128 and No. MIP-9107760, and in part by Hughes Aircraft Co.

Major funding and support for the Test Evaluation Chip Experiment has been provided by Hughes Aircraft Co., LSI Logic, and Digital Testing Services.

# TABLE OF CONTENTS

|    | Abs  | tract                                     | i   |

|----|------|-------------------------------------------|-----|

|    | Ack  | nowledgments                              | ii  |

|    | Tab  | le of Contents                            | iii |

|    | List | of Tables                                 | vi  |

|    | List | of Illustrations                          | vii |

| Ch | apte | er 1. Introduction                        |     |

|    | 1.1  | Background                                | 1   |

|    | 1.2  | Output Waveform Analysis                  | 2   |

|    | 1.3  | Overview of Dissertation                  | 4   |

| Ch | apte | er 2. Testing for Delay Faults            |     |

|    | 2.1  | Early Work in Delay Fault Testing         | 5   |

|    | 2.2  | Delay Fault Definitions                   | 9   |

|    | 2.3  | Review of Delay Fault Testing             | 12  |

|    |      | 2.3.1 Direct Approaches                   | 12  |

|    |      | 2.3.2 Indirect Approaches                 | 15  |

|    | 2.4  | Inaccurate Delay Modeling                 | 16  |

|    |      | 2.4.1 Modeling Gate Delay                 | 16  |

|    |      | 2.4.2 Three-Pattern Delay Tests           | 17  |

|    |      | 2.4.3 Need For Three-Pattern Tests        | 20  |

|    |      | 2.4.4 Experiment                          | 21  |

|    |      | 2.4.5 Possible Solutions                  | 23  |

|    | 2.5  | Output Waveform Analysis                  | 24  |

| Ch | apte | er 3. Post-Sampling Waveform Analysis     |     |

|    | 3.1  | Description                               | 26  |

|    | 3.2  | Implementation                            | 29  |

|    |      | 3.2.1 Design Considerations               | 29  |

|    |      | 3.2.2 Timing Diagrams                     | 30  |

|    |      | 3.2.3 Architecture for Stability Checking | 32  |

|    |      | 3.2.4 Stability Checker Implementations   | 33  |

|    |      | 3.2.4.1 Intuitive Designs                 | 34  |

|    |      | 3.2.4.2 Formal Design Level Output        | 34  |

|        | 3.2.4.3 Formal Design Pulse Output                   | 36 |

|--------|------------------------------------------------------|----|

|        | 3.2.4.4 Ad-hoc Designs                               | 36 |

|        | 3.2.4.5 Switching (Short-Circuit) Current Design     | 38 |

|        | 3.2.4.6 Bridging Current Design                      | 38 |

| 3.3    | Compatibility With Sampling And Bist                 | 39 |

|        | 3.3.1 Combined Stability Checking and BIST           | 39 |

|        | 3.3.2 Aliasing                                       | 41 |

| 3.4    | Testing Stability Checkers                           | 41 |

| 3.5    | Results                                              | 42 |

| 3.6    | Conclusion                                           | 45 |

| Chapte | er 4. On-Line Delay Testing                          |    |

| 4.1    | Introduction                                         | 46 |

| 4.2    | On-Line Stability Checking                           | 47 |

|        | 4.2.1 Off-line Delay Testing by Stability Checking   | 47 |

|        | 4.2.2 Reduced On-Line Checking Period                | 48 |

| 4.3    | Implementing On-Line Stability Checking              | 49 |

|        | 4.3.1 Architecture for Stability Checking            | 50 |

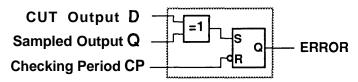

|        | 4.3.2 Stability Checker Design                       | 51 |

| 4.4    | Performance Evaluation                               | 55 |

|        | 4.4.1 Limitations                                    | 55 |

|        | 4.4.2 Common Failure Modes                           | 55 |

|        | 4.4.3 Performance Comparison with Other Techniques   | 57 |

| 4.5    | Padding Short Paths                                  | 58 |

|        | 4.5.1 Timing-Optimized Circuits                      | 59 |

|        | 4.5.2 Custom Cells for Padding Short Paths           | 59 |

|        | 4.5.3 Padding Example Using Logic Synthesis Tool     | 61 |

|        | 4.5.4 Algorithm for Padding Short Paths              | 64 |

| 4.6    | Extensions                                           | 67 |

|        | 4.6.1 Stability Checking versus Final-Value Checking | 67 |

|        | 4.6.2 Multiple Checking Periods                      | 67 |

|        | 4.6.3 Self-Timed Clock Frequency                     | 68 |

|        | 4.6.4 Software Stability Checking                    | 68 |

|        | 4.6.5 VHDL Synthesis                                 | 69 |

| 17     | Conclusion                                           | 70 |

| Cnapte | er 5. Pre-Sampling Waveform Analysis               |      |

|--------|----------------------------------------------------|------|

| 5.1    | Description                                        | 71   |

|        | 5.1.1 Delay Flaws                                  | 72   |

|        | 5.1.2 Delay Faults                                 | 72   |

|        | 5.1.3 Waveform Analysis Functions                  | 73   |

| 5.2    | Integration                                        | 74   |

|        | 5.2.1 Integration Over Whole Cycle                 | 74   |

|        | 5.2.2 Integration Over Part of Cycle               | 77   |

|        | 5.2.3 Enhanced Integration                         | 78   |

|        | 5.2.4 Fault Coverage Examples                      | 79   |

| 5.3    | Implementation                                     | 82   |

|        | 5.3.1 Design Considerations                        | 82   |

|        | 5.3.2 Parallel Implementation                      | 83   |

|        | 5.4.3 Serial Implementation                        | 84   |

| 5.4    | Conclusion                                         | 86   |

| Chapte | er 6. Test Chip Experiment                         |      |

| 6.1    | Overview of Experiment                             | 87   |

|        | 6.1.2 Tests Applied                                | 87   |

|        | 6.1.2 Test Chip                                    | 88   |

| 6.2    | Experimental Results                               | 89   |

|        | 6.2.1 Test Comparisons                             | 89   |

|        | 6.2.2 Chip Speed Measurement                       | 89   |

|        | 6.2.3 "ROB" CUT Propagation Delay Measurements     | 90   |

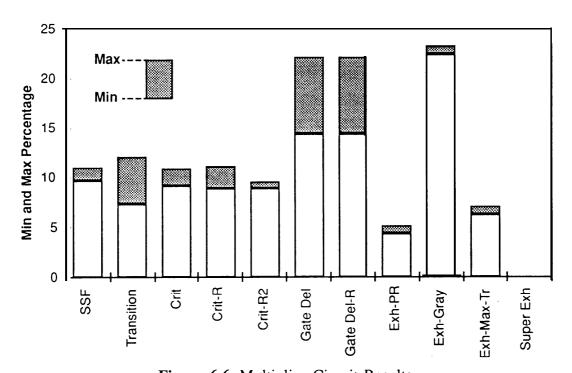

|        | 6.2.4 "MULT6SQ" CUT Propagation Delay Measurements | 93   |

| Chapte | er 7. Concluding Remarks                           |      |

| 7.1    | Contributions                                      | 95   |

| 7.2    | Future                                             | 96   |

|        |                                                    |      |

| Refere | nces                                               | . 98 |

# LIST OF TABLES

| Table | Title                                                       |      |

|-------|-------------------------------------------------------------|------|

| 2.1.  | Delay Fault Models                                          | 17   |

| 2.2.  | 3-input NAND3 Delays                                        | 20   |

| 2.3.  | Percentage of Gates with Equal Longest Paths for Two Inputs | . 21 |

| 3.1.  | Functional Description of Stability Checker                 | 28   |

| 3.2.  | Average Number of Transitions per Node per Vector           | 43   |

| 4.1.  | Comparison of Transistor Counts                             | 55   |

| 4.2.  | Synopsys Results for ALU 18 i                               | 63   |

| 4.3.  | Greedy Padding Algorithm                                    | 65   |

| 4.4.  | Results for Greedy Padding Algorithm                        | 66   |

| 4.5.  | VHDL Process Statements                                     | 69   |

| 6.1.  | Tests Applied to Robust CUT                                 | 91   |

| 6.2.  | Tests Applied to 6x6 Multiplier                             | 93   |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                              |      |

|--------|--------------------------------------------------------------------|------|

| 1.1.   | Output Waveform Analysis Classes                                   | . 3  |

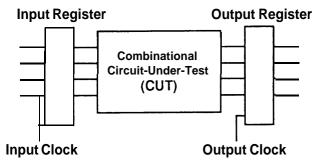

| 2.1.   | Hardware Model                                                     | 6    |

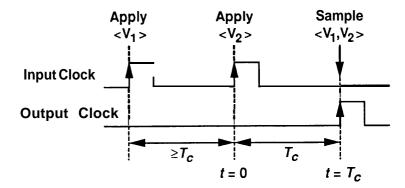

| 2.2.   | Waveforms for Delay Testing                                        | 7    |

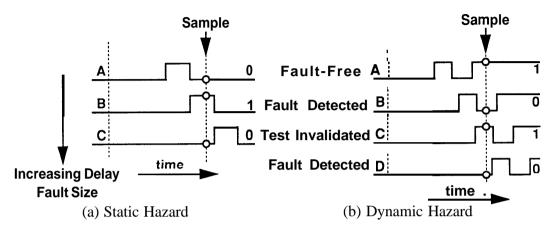

| 2.3.   | Test Invalidation by Hazards                                       | 8    |

| 2.4.   | Delay Fault Detection can Depend on Size                           | . 8  |

| 2.5.   | Short and Long Path Delay Faults                                   | 9    |

| 2.6.   | Relation Between Delay Fault Models                                | 12   |

| 2.7.   | NAND2 Gate Simulated                                               | 18   |

| 2.8.   | Simulation of (A,B)                                                | 19   |

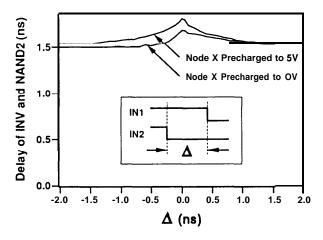

| 2.9.   | Delay of INV and NAND2 as a Function of Shift in Input Transitions | . 20 |

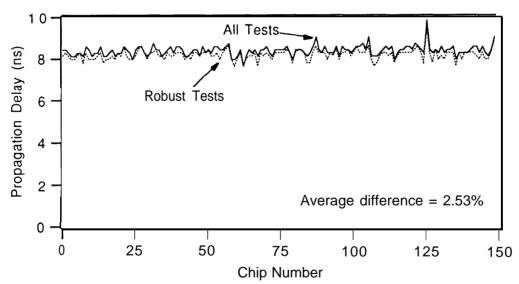

| 2.10.  | Graph of Maximum Propagation Delay of All Tests and Robust Tests   | . 22 |

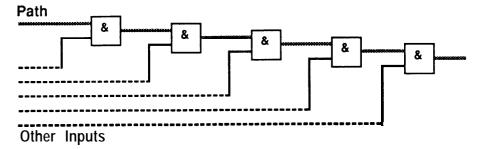

| 2.11.  | Path Under Test                                                    | 24   |

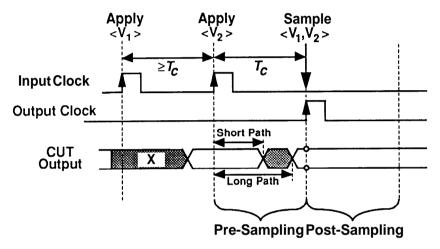

| 2.12.  | Output Waveform Analysis                                           | 25   |

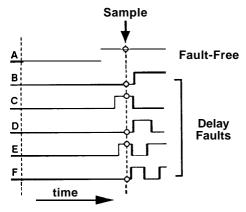

| 3.1.   | Waveforms with Delay Faults                                        | 26   |

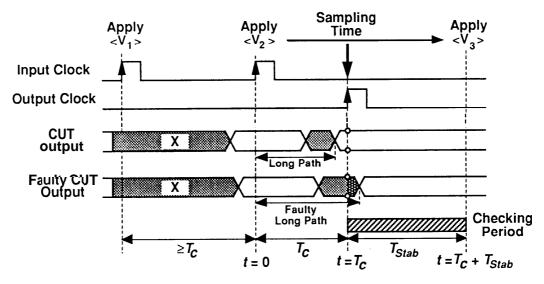

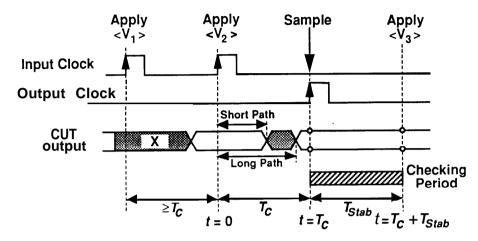

| 3.2.   | Stability Checking Waveforms                                       | 27   |

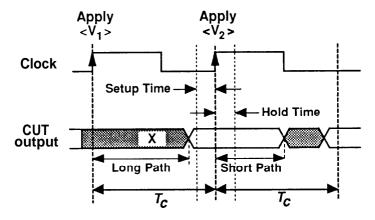

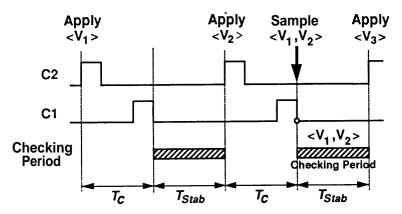

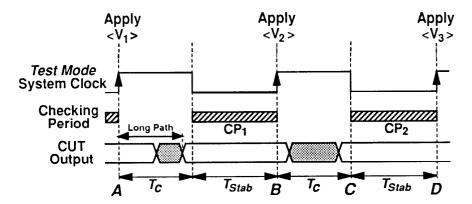

| 3.3.   | Timing Waveforms for Flip-Flop Designs                             | 30   |

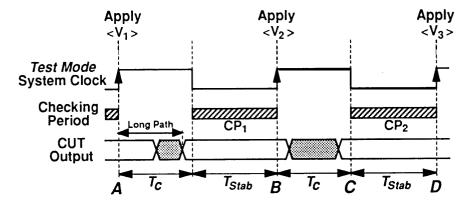

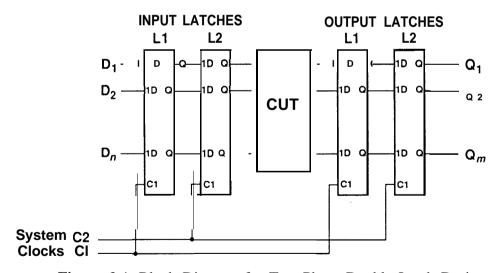

| 3.4.   | Block Diagram for Two-Phase Double Latch Designs                   | 31   |

| 3.5.   | Test Mode Timing Waveforms for Two-phase Designs                   | 32   |

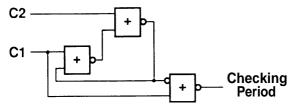

| 3.6.   | Generating Checking Period for Two-phase Designs                   | 32   |

| 3.7.   | Block Diagram of Stability Checking Architecture                   | 33   |

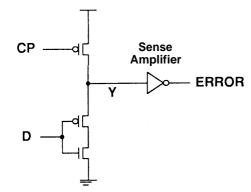

| 3.8.   | Conceptual Implementation of Stability Checker                     | 34   |

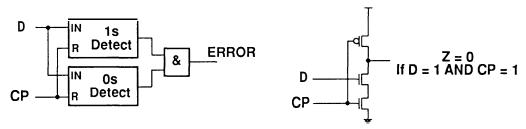

| 3.9.   | (a) Intuitive Design, (b) l s Detector Implementation              | 34   |

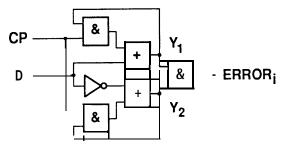

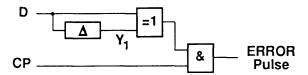

| 3.10.  | Gate-Level Stability Checker Design                                | 35   |

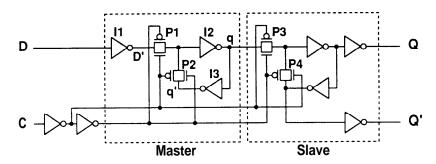

| 3.11.  | Master-Slave D Flip-Flop (FD1 [LSI 91])                            | 35   |

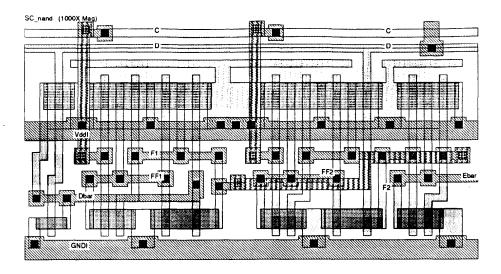

| 3.12.  | NAND Layout of Stability Checker Design in Fig. 3.10               | 36   |

| 3.13.  | Pulse Output Stability Checker Design                              | 36   |

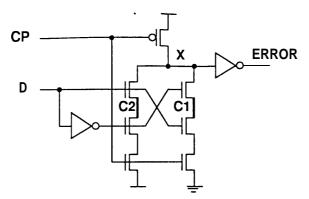

| 3.14.  | Dynamic Stability Checker                                          | 37   |

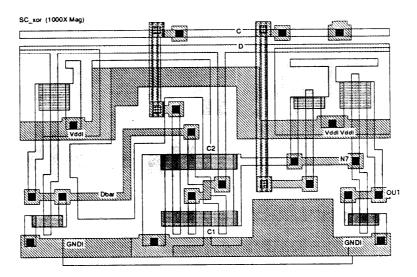

| 3.15.  | Layout for Dynamic Stability Checker in Fig. 3.14                  | 37   |

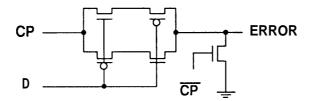

| 3.16.  | Efficient XOR Checker Design                                       | 37   |

| 3.17.  | Switching Current-Type Stability Checker                           | 38   |

| 3.18.  | Timing Waveforms for Flip-Flop Designs                             | 39   |

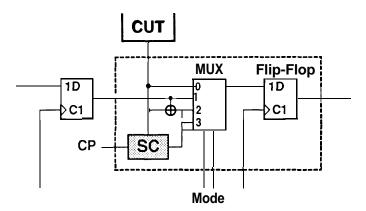

| 3.19.  | Modified BILBO Cell                                                | 40   |

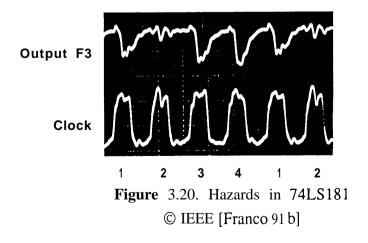

| 3.20.  | Hazards in 74LS 18 1                                               | 42   |

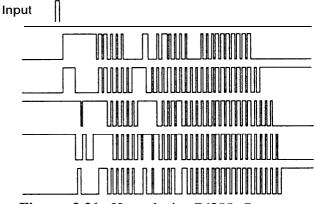

| 3.21.  | Hazards in C6288 Outputs                                           | 43   |

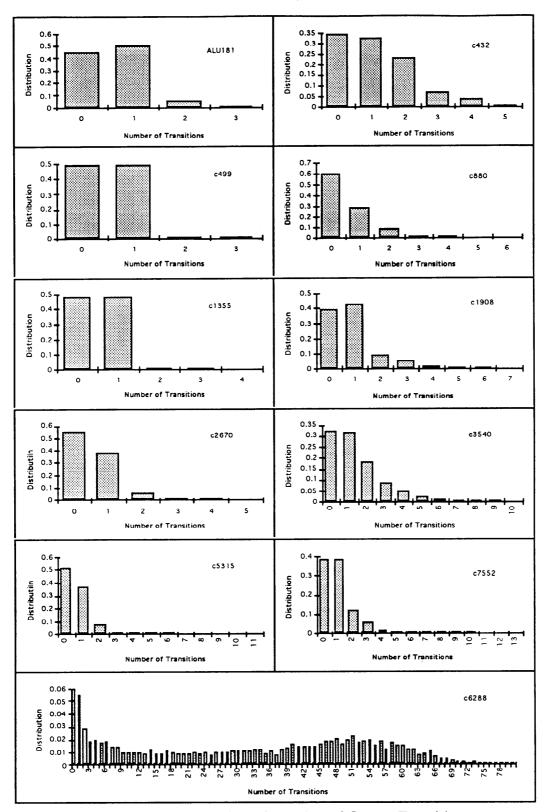

| 3.22.  | Distribution of Number of Output Transitions                       | 44   |

| Figure | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

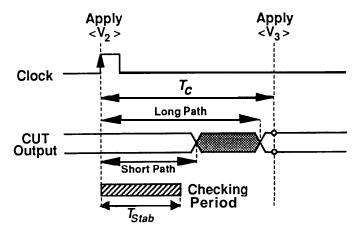

| 4.1.   | , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48 |

| 4.2.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

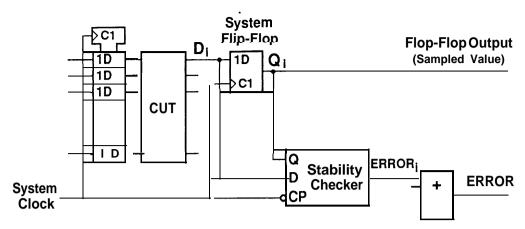

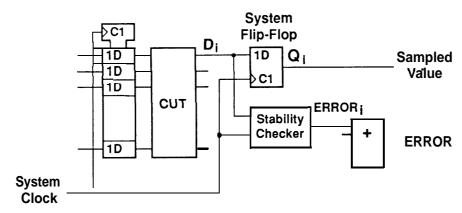

| 4.3.   | Block Diagram of On-Line Stability Checking Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

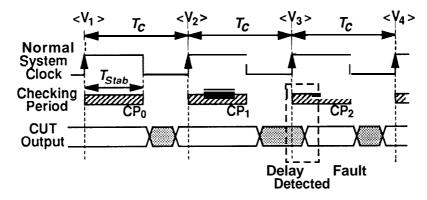

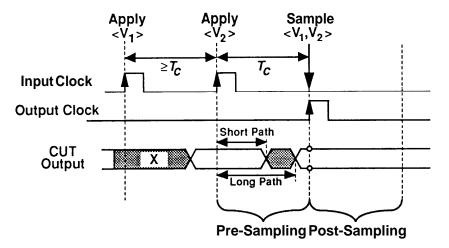

| 4.4.   | Timing Waveforms for On-Line Stability Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |

| 4.5.   | - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - 112 - | 51 |

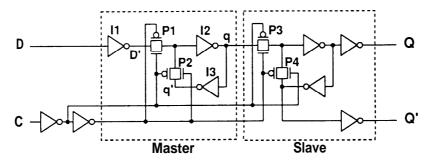

| 4.6.   | Master-Slave D Flip-Flop (FD1 [LSI 91])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

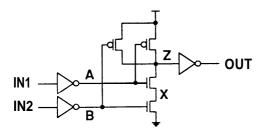

| 4.7.   | Modified Master of Flip-Flop with Stability Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

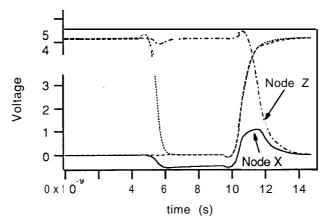

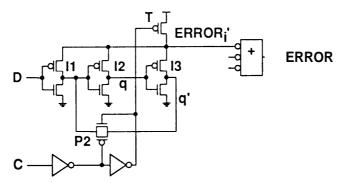

| 4.8.   | Spice Simulations for Modified Stability Checking Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

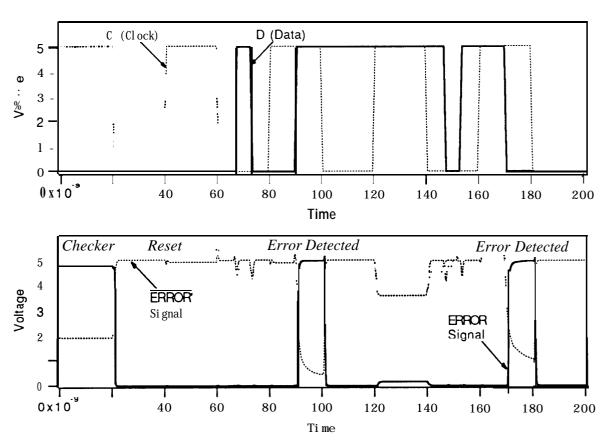

| 4.9.   | Combined Scan and Stability Checking Flip-flop Master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

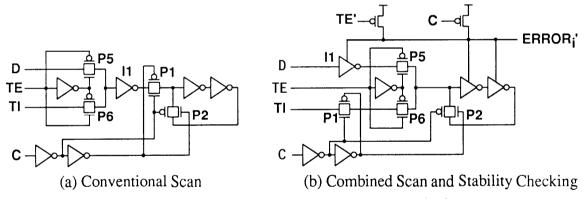

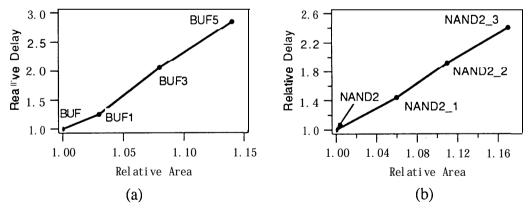

| 4.10.  | Delay versus Area for LSI Standard Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59 |

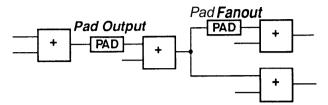

| 4.11.  | Two Types of Padding Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

| 4.12.  | (a) CMOS3 Buffer and Derivatives, (b) CMOS3 NAND2 and Derivatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60 |

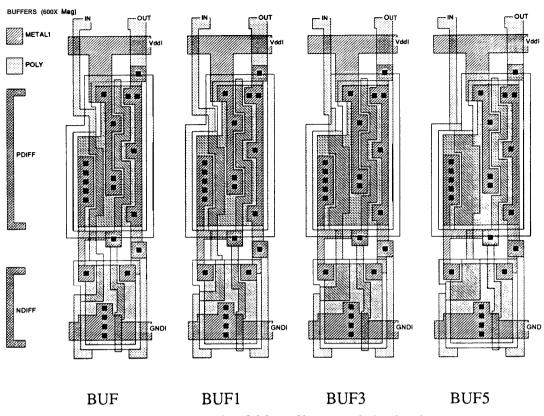

| 4.13.  | The CMOS3 Buffer, and 3 Derivatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61 |

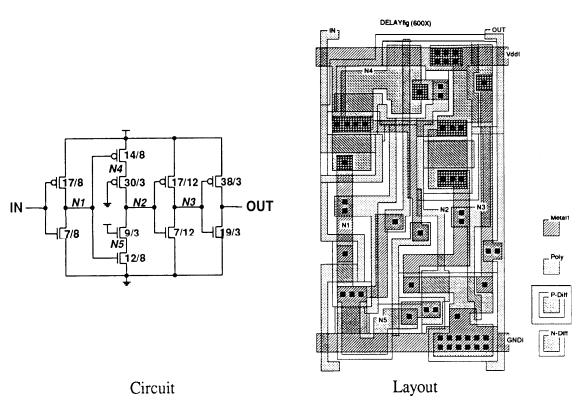

| 4.14.  | DELAY Cell in CMOS3 Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62 |

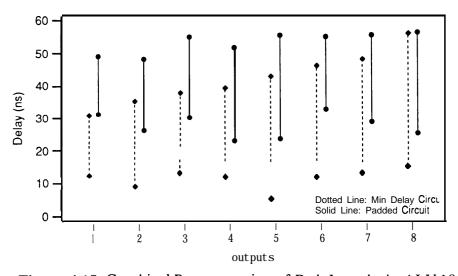

| 4.15.  | Graphical Representation of Path Lengths in ALU 18 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63 |

| 5.1.   | Output Waveform Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71 |

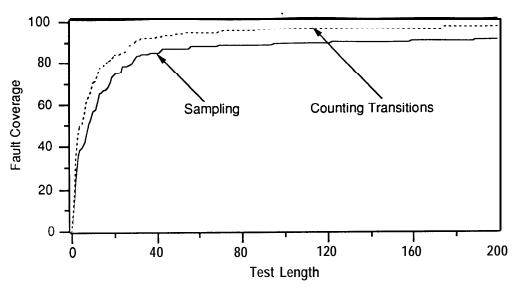

| 5.2.   | Fault Coverage for ALU 18 1 for Sampling and Counting Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74 |

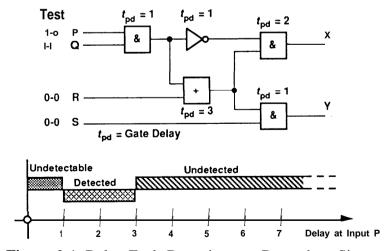

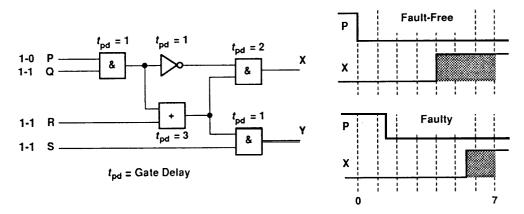

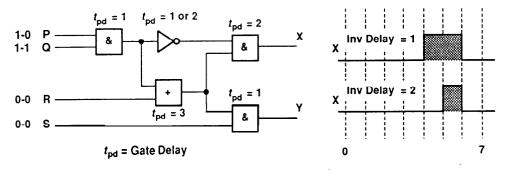

| 5.3.   | Slow-to-Fall Fault at Input P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |

| 5.4.   | Inverter Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

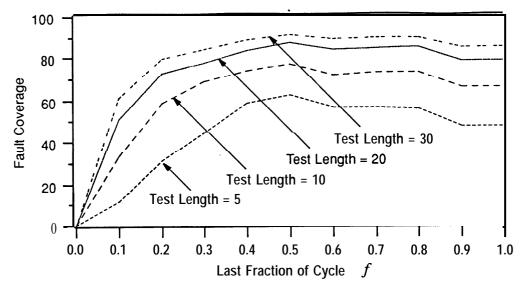

| 5.5.   | Fault Coverage for ALU 18 1 Integrating Over Last Part of Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78 |

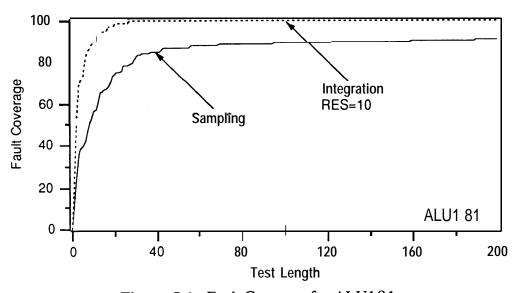

| 5.6.   | Fault Coverage for ALU 18 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79 |

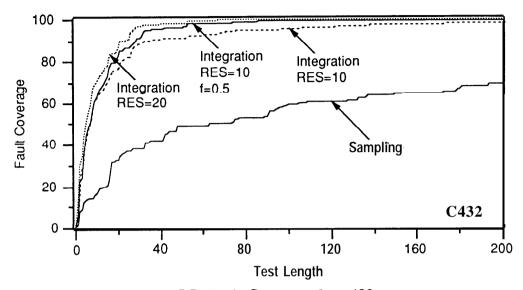

| 5.7.   | Fault Coverage for c432                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

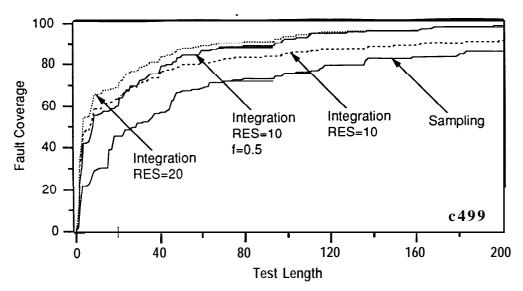

| 5.8.   | Fault Coverage for c499                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81 |

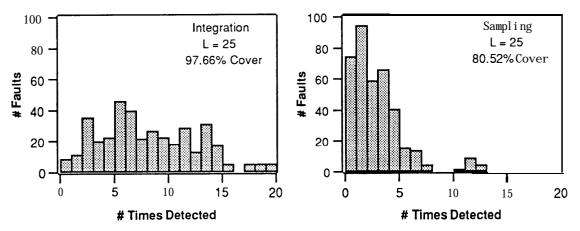

| 5.9.   | Distribution of Number of Patterns that Detect a Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81 |

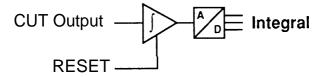

| 5.10.  | Conceptual Integrator Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82 |

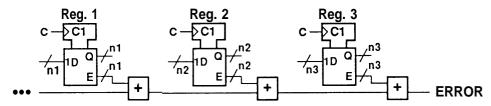

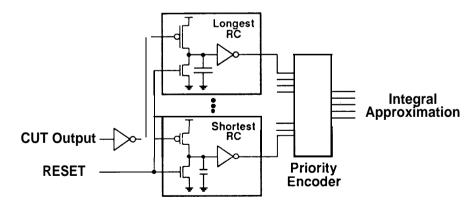

| 5.11.  | Parallel Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83 |

| 5.12.  | Serial Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 84 |

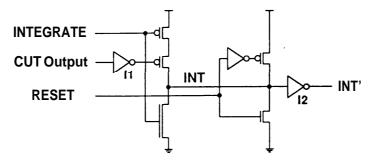

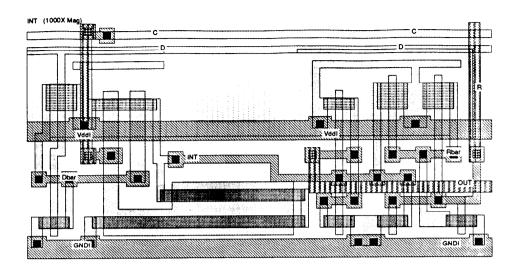

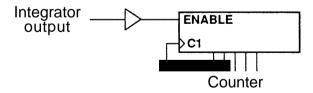

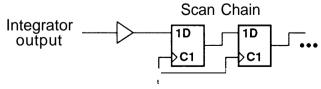

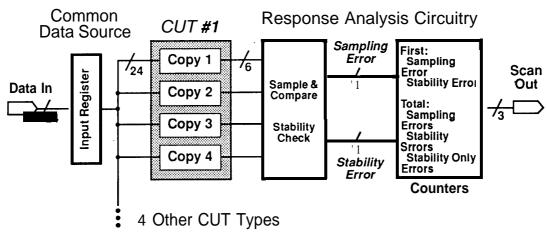

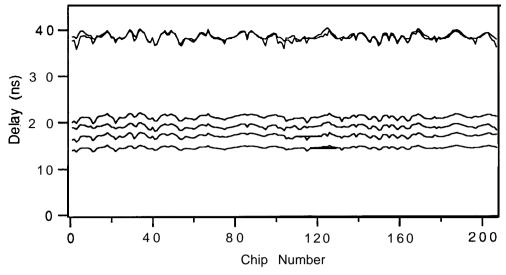

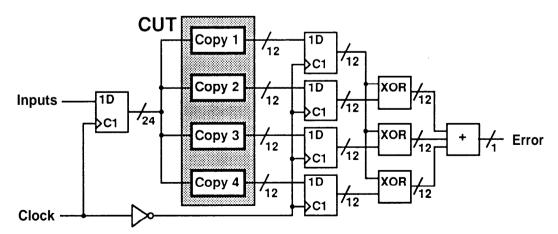

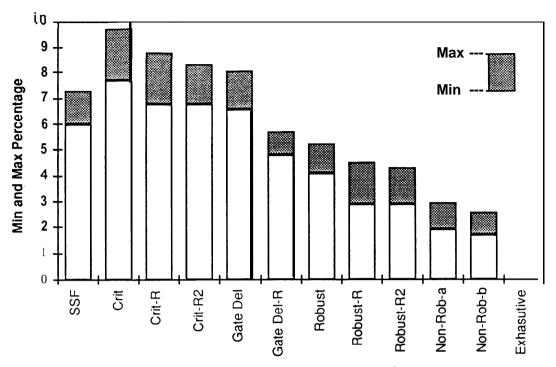

| 5.13.  | Layout for Integrator in Fig. 5.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85 |