# INSTRUCTION LEVEL PARALLEL PROCESSORS—A NEW ARCHITECTURAL MODEL FOR SIMULATION AND ANALYSIS

Kevin W. Rudd

Technical Report: CSL-TR-94-657

December 1994

# INSTRUCTION LEVEL PARALLEL PROCESSORS—A NEW ARCHITECTURAL MODEL FOR SIMULATION AND ANALYSIS

by Kevin W. Rudd

Technical Report: CSL-TR-94-657

December 1994

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305-4055

#### Abstract

Trends in high-performance computer architecture have led to the development of increased clock-rate and dynamic multiple-instruction issue processor designs. There have been problems combining both these techniques due to the pressure that the complex scheduling and issue logic puts on the cycle time. This problem has limited the performance of multiple-instruction issue architectures. The alternative approach of static multiple-operation issue avoids the clock-rate problem by allowing the hardware to concurrently issue only those operations that the compiler scheduled to be issued concurrently. Since there is no hardware support required to achieve multiple-operation issue (there are multiple operations in a single instruction and the hardware issues a single instruction at a time), these designs can be effectively scaled to high clock rates. However, these designs have the problem that the scheduling of operations into instructions is rigid and to increase the performance of the system the entire system must be scaled uniformly so that the static schedule is not compromised. This report describes an architectural model that allows a range of hybrid architectures to be studied.

**Key Words and Phrases:** super-scalar, superscalar, VLIW, instruction level parallelism, computer architecture, static scheduling, dynamic scheduling, processor simulation.

Copyright © 1994 by Kevin W. Rudd

# Contents

| 1            | Introduction                                                                         | 1  |

|--------------|--------------------------------------------------------------------------------------|----|

| 2            | Super-scalar issue techniques                                                        | 1  |

|              | 2.1 Dynamic super-scalar issue techniques—dynamic multi-instruction issue processors | 2  |

|              | 2.2 Static super-scalar issue techniques—static multi-operation issue processors .   | 2  |

|              |                                                                                      | 3  |

|              | 2.3 Issues leading to a hybrid design                                                |    |

|              | 2.4 Hybrid architecture conclusions                                                  | 6  |

| 3            | The split-issue execution paradigm                                                   | 6  |

|              | 3.1 An introduction to split-issue                                                   | 8  |

|              | 3.2 A tabular representation for split-issue                                         | 10 |

|              | 3.3 Representation of a traditional static multi-operation issue processor           | 12 |

|              | 3.4 Further examples of split-issue techniques                                       | 13 |

| 4            | The NYFO VLIW model                                                                  | 17 |

|              | 4.1 Stages in an NYFO VLIW model                                                     | 18 |

|              | 4.2 Elaboration on the invoke stage                                                  | 19 |

|              | 4.3 Elaboration on the compute stage                                                 | 20 |

|              | 4.4 Implementation policies                                                          | 21 |

| 5            | Example implementation descriptions                                                  | 22 |

|              | 5.1 Simple static multi-operation issue implementation                               | 22 |

|              | 5.2 Simple dynamic multi-instruction issue implementation                            | 23 |

| 6            | Conclusion                                                                           | 24 |

| 7            | ${f Acknowledgments}$                                                                | 24 |

| $\mathbf{A}$ | Illustrative code fragments                                                          | 24 |

#### 1 Introduction

High-performance processor design has recently taken two different (and often diametrically opposed) approaches. One approach used to design a high-performance processor is to increase the execution rate by increasing the clock rate of the processor or by reducing the latency of operations. These improvements are primarily through the application of circuit design and fabrication process enhancements and, while important, are outside the scope of this report. Another approach used to design a high-performance processor is to issue and to execute multiple operations concurrently. Traditional processor designs that issue and execute at most one operation per cycle have been referred to as "scalar" designs<sup>1</sup>. Processor designs that can issue and execute more than one operation per cycle will be referred to as "super-scalar" processors.

Historically, there have been two primary techniques used to achieve super-scalar performance. The first technique uses dynamic analysis of the instruction stream during execution to determine those operations that are independent. These independent operations can be issued and executed concurrently. The second technique uses static analysis performed by the compiler to schedule independent operations together into compound multi-operation instructions. All operations in a given instruction can be issued and executed concurrently with no dynamic analysis. Both of these approaches to processor design have advantages and disadvantages and both have demonstrated significant problems that have limited their performance. We have developed an architectural model that will be used as a research platform to evaluate a number of configuration and policy trade-offs in a design space that spans these two techniques and allows a variety of hybrid architectures to be compared.

Section 2 describes these two techniques in more detail and develops the need for exploring hybrid architectures to achieve scalable high-performance processor designs. Section 3 describes the execution paradigm that supports modeling a range of processors that spans these two techniques and provides several examples to clarify its organization and behavior. Section 4 describes the model in detail. This model is parametric not only in configuration (number and type of function units, architectural and implementation latencies) but also in several of the key policies that affect the behavior of the architecture. Section 5 describes several examples to reinforce the features and operation of the model.

## 2 Super-scalar issue techniques

As recent designs have demonstrated, neither dynamic nor static techniques alone have been sufficient to achieve high performance. The obvious consequence of this situation is that hybrid techniques should be considered as a general and effective solution to the problem of achieving high-performance in a super-scalar processor.

<sup>&</sup>lt;sup>1</sup>Each operation in a "scalar" processor operates on single (scalar) data values in contrast to a "vector" processor which, while executing only a single operation at a time, execute the operation on multiple (vector) data values.

# 2.1 Dynamic super-scalar issue techniques—dynamic multi-instruction issue processors

The most popular technique today is the use of dynamic analysis to determine the operations that are available for concurrent issue and execution. Processors that use this technique are dynamic multi-instruction issue processors and are frequently referred to as superscalar processors—an unfortunate but not untrue nomenclature since this technique is but one of many techniques that achieve super-scalar performance. In this type of architecture, each instruction in the instruction stream consists of a single operation. In order to issue and to execute multiple operations concurrently, operations in the instruction stream must be analyzed for dependencies each time that issue is attempted. Compilers minimize the actual dependencies that an instruction stream will have but if the compiler cannot, or does not, prevent a dependency, the hardware must ensure that all dependencies are detected and enforced. This technique has significant advantages, one of which is code compatibility with other processors sharing the same architecture—a significant advantage in the marketplace if not in the research laboratory. Another advantage is that, since the analysis is based on the dynamic code stream, operations across branches and other changes of control flow are considered for concurrent issue and execution.

The major drawback of using dynamic analysis in a dynamic multi-instruction issue processor is that it requires a significant amount of hardware to analyze the instruction stream and to ensure that correctness is maintained. This approach lengthens the amount of time required to perform operation issue and can result in an increased cycle time (resulting in a reduced clock rate) or an increased pipeline length (resulting in increased branch penalties). Neither of these results is desirable and and the increase in performance from the concurrent issue and execution of multiple operations can be reduced or eliminated due to these problems. The complexity of the hardware required to perform the analysis is limited by both the number of operations within the analysis window (proportional to  $n^2$  where n is the window size) and the maximum number of pending register results (proportional to n0 where n1 is the number of pending results). Existing designs have had difficulty with dynamically analyzing 2 to 4 operations and even with low issue widths have been limited to exploiting only those cases that match specific patterns of operations.

# 2.2 Static super-scalar issue techniques—static multi-operation issue processors

An alternative technique is the use of static analysis to determine the operations that are available for concurrent issue and execution. Processors that use this technique are static multi-operation issue processors and are frequently referred to VLIW processors—these processors have very long instruction words. In this type of architecture, each instruction in the instruction stream consists of multiple independent operations. No dynamic analysis is required to issue and execute these operations concurrently—the compiler performs any necessary analysis and schedules independent operations within a single instruction. Since no dynamic analysis is required during execution, the clock rate is not limited by the instruction issue logic and wide and fast processor designs are feasible. It is possible that

there will be independent operations within several instructions—but, in order to issue and execute operations from multiple instructions concurrently, similar techniques to those used in dynamic multi-instruction issue processors would be required and similar complexity issues would arise.

Using static analysis in a static multi-operation issue processor is not without its problems. While there is no complex hardware to limit the performance, there is the requirement that the compiler have full knowledge of the hardware structure and latencies. This requirement is necessary since there are typically no interlocks on data dependencies and operations must not be scheduled until the source operands are ready. A side effect is that the hardware cannot vary from the specification that the compiler works with—all latencies (measured in cycles) must be constant. Thus, while the entire system can be improved if the speed-up is uniform, individual portions of the system cannot be improved upon independently without requiring that the program be recompiled in order to run on the new system. Another side effect is that since latencies are constant, operations with non-constant latencies cannot be supported. Load operations from a memory hierarchy that has multiple levels (and includes data caches) have multiple latencies depending on the location of the data within the memory hierarchy. This makes data caches unusable in a static multi-operation issue architecture and results in memory operations that have very long latencies. However, there are many programs that are able to be efficiently scheduled with long memory operation latencies. These programs are frequently loop-based floating point programs are able to be scheduled to hide the memory latency within loops and calculations. Existing implementations have been able to exploit instructions that are 28 operations wide [4] on this class of application. Unfortunately, there are also many programs that are not able to hide the long memory latency and these programs do extremely poorly on these processors.

#### 2.3 Issues leading to a hybrid design

Clearly, both dynamic multi-instruction issue and the static multi-operation issue techniques can be used to achieve super-scalar performance and neither one has been proven to be superior to the other in all cases. However, these techniques are not mutually exclusive and some combination of static and dynamic techniques may result in an architecture that tolerates multiple latency operations and is efficient at wide instruction widths. In order to understand the aspects of these techniques that must be considered in a hybrid architecture, several issues must first be discussed.

One fundamental distinction that must be made is the separation of architectural and implementation specifications. An architectural specification determines the operation semantics that the compiler must schedule code for to ensure a correct schedule and defines the virtual processor. An implementation specification determines the operation semantics that are actually implemented—but this must be transparent outside the processor so that code that is scheduled to the architectural specification will run. For example, an add operation may have an architectural latency of  $2^{\sim}$  while a given implementation may have a latency of  $3^{\sim}$ —this is not a problem as long as the implementation ensures that the instruction stream will see the result as if it had occurred in  $2^{\sim}$  as scheduled.

The notion of architectural and implementation specifications lead directly to the notion

of virtual time and latency and real time and latency. Operations are scheduled according to the architectural specification in virtual time and appear to have virtual latency while they execute on the hardware according to the implementation specification in real time and have real latency. The implementation of the processor provides the illusion of a virtual processor that implements the architectural specification in much the same way that memory management hardware and operating system software provide the illusion of virtual memory—in both cases the reality is potentially very different from the illusion and yet there is no awareness of reality to the program.

In order to maintain the illusion of the virtual machine, when a result is generated earlier in real time than the virtual latency specifies, the result must be delayed so that it does not become visible to the instruction stream until the appropriate virtual time. Analogously, when a result is generated later in real time than the virtual latency specifies, any operations that use the result (as scheduled in virtual time) are delayed appropriately until the result is available. This distinction has been implicitly true within dynamic multi-instruction issue architectures (where operation reordering avoids data dependencies when possible and interlocks prevent data dependencies from occurring); there is no distinction between architecture and implementation in static multi-operation issue architectures since no operation variation is allowed<sup>2</sup>. The distinction between the architecture and the specification as it applies to dynamic VLIW architectures was noted in [5].

Most operations in a dynamic multi-instruction issue architecture have a virtual latency of 1 —that is, the hardware guarantees that dependent operations that are scheduled consecutively (and which, in the virtual machine, issue in consecutive virtual cycles) will produce the desired result. The few exceptions are typically memory load and control flow operations which often have a virtual latency of 2° and are specified with a "load delay slot" or a "branch delay slot" that may or may not be able to be filled with a useful instruction by the compiler. For the case of a load that takes longer, interlocks typically ensure that the dependencies between operations are honored; for the case of a branch that takes longer, the pipeline control typically inserts null operations into the pipeline until the new instruction stream is available. A recent trend in architectural extensions is to deprecate or eliminate these "delayed" operations and to add in analogous operations that have a virtual latency of 1° so that all operations have uniform virtual latencies. Shifting away from delayed operations allows implementations to more easily support varying issue widths and out-of-order execution. Unfortunately, this does not eliminate the need for the compiler to target its code schedule for a given architecture with knowledge of its implementation specification—in fact, this customized scheduling becomes more and more important as higher performance and wider issue designs are developed.

Even a simple machine that performs no concurrent operation issue is affected by poor code scheduling. A program that is scheduled using only the architectural latencies (of 1° per operation) will run correctly but will exhibit poor performance on many implementations. With this code schedule, any time that there is a dependency (when the implementation latency exceeds the architectural latency) the pipeline will have to stall until the

<sup>&</sup>lt;sup>2</sup>There have been cases where some results, primarily those from memory operations, may not be available when scheduled. These cases were handled by stalling the processor until the late result was available.

dependency is resolved. One of the goals of dynamic multi-instruction issue architectures is to analyze the instruction stream and to rearrange the operations so that better utilization of the pipeline is possible (this was a precursor to the goal of achieving concurrent issue and execution and is a similar but more limited problem). Thus, when a dependency arises, the dynamic scheduling will attempt to find another operation that can execute while the stalled operation waits for the dependent result to become available. But even if a program is scheduled efficiently for one implementation, when run on a different implementation it may no longer be scheduled efficiently and performance may suffer.

When concurrent issue and execution is considered, the problem becomes worse. The goal is no longer to find one available operation to issue but to find several available operations to issue. In this situation, there are more operands being analyzed and and more operations in progress within the pipelines to be checked against resulting in significantly more hardware requirements. This occurs even when the compiler anticipates which operations are independent and schedules them so as to avoid any dependencies on a given implementation—however, since this information is thrown away after the schedule is generated there is no way that the implementation can be aware of this. Additionally, operations that are analyzed but not issued are examined again during the next analysis cycle resulting in more redundant computation by the hardware.

To clarify this problem, consider the following example code sequence:

```

0:

r \leftarrow comp8(a, b)

1:

s \leftarrow comp2(c, d)

t \leftarrow comp4(d, e)

2:

3:

u \leftarrow comp2(s, f)

; s available

4:

v \leftarrow comp4(s, s)

w \leftarrow comp2(u, a)

5:

; u available

6:

x \leftarrow comp2(t, u)

t available

7:

y \leftarrow comp4(b, w)

w available

8:

z \leftarrow comp2(r, x)

; r, v, x available

```

In this code sequence, comp2 operations complete in  $2^{\sim}$ , comp4 operations complete in  $4^{\sim}$ , and comp8 operations complete in  $8^{\sim}$ .

First, consider the case where the architectural latency is 1° for all operations. Now every operation scheduled completes "late" and all operations that are in any stage of execution must have their result operands compared with all operations being evaluated for issue to ensure that there are no dependencies that must be enforced. All operations that are being analyzed for issue until cycle 8 must be checked to ensure that they do not use result **r** (which is unavailable for cycles 1 through 7) even though the compiler scheduled the code with this knowledge and was able to avoid any true dependency. This is true of every operation that is in execution since all of these are "late" relative to the architectural specification.

Next, consider the same example where the architectural specification reflects the anticipated implementation specification. This means that values are known not to be available until their architectural (and implementation) latency and operations that are not "late" do

not need to be checked while analyzing the instruction stream. Now, when every operation completes "on time" there are no checks required. In contrast, consider the same example where now all comp2 operations actually take 3 to complete. In this case, the operation in instruction 1 does not complete in cycle 3 but in cycle 4. Since result s is not late until cycle 4 this cycle is the first cycle that this result needs to be checked while analyzing the instruction stream. Even if there are a number of operations that have an implementation latency that is greater than the architectural latency, it is clear from these cases that using non-unit architectural latencies that are matched closely to the anticipated implementation latencies results in few late operations. Since there are few late operations there are also few pending register results that need to be checked for dependencies during the issue process are reduced resulting in less complex issue hardware.

#### 2.4 Hybrid architecture conclusions

As has been shown, the significant feature that a dynamic multi-instruction issue processor has is its ability to reschedule code to support unexpected latencies—either from a poor schedule or from a mispredicted operation latency (typically from the memory system). This is, unfortunately, an expensive feature to support given the liabilities of single-operation instructions and the 1° virtual operation latencies. There are two significant features that the static multi-operation issue processors have—multiple operation instructions (which are guaranteed independent) and accurate virtual operation latencies. These features have their downsides however. The exclusive use of static scheduling proscribes any scheduling errors—including mispredicted operation latencies—requiring that all implementation latencies match the virtual latencies.

All is not as bleak as one might expect—there are three key characteristics of these two processors that can be identified and must be considered in a hybrid architecture: the instruction stream must include as much dependency information as possible from the compiler; architectural latencies that correspond reasonably well to the anticipated implementation latencies must be used; and the distinction between architectural and implementation specifications and the illusion of a virtual machine. Providing these capabilities reduces the amount of dynamic analysis that must be performed to issue and to execute concurrent operations (the critical problem with dynamic multi-instruction issue processors) and reduces or eliminates many scheduled stalls (the critical problem with static multi-operation issue processors). This results in fast wide operation issue architectures that will achieve much higher performance and much greater scalability than either of the two original architectures.

## 3 The split-issue execution paradigm

The primary goal of creating a new architectural model is to explore high-performance instruction-level parallel processor architectures over a wide range of configurations. In order to meet this requirement, section 2.4 presented three architectural characteristics that are effective in achieving this goal. To include dependency information from the compiler we use statically scheduled instructions that contain independent operations; to minimize the differences between the architectural and implementation machines we use realistic

latencies for all operations; and to maintain the illusion of a virtual processor we use splitissue techniques.

The first two features, instructions containing independent operations and the use of realistic latencies, are already characteristic of static multi-operation issue processors. This similarity is not surprising since both of these are efficient techniques for embedding dependency information into the instruction stream. Both the Horizon [1] and Cydra 5 [2] processors used variations on the use of realistic latencies for their operations to avoid unnecessary analysis or stalls.

In the Horizon processor, instead of using fixed operation latencies, each instruction embedded the distance to the nearest use of any result from the contained operations along any possible path. The use of this distance field allowed additional instructions to be issued while a given instruction was in execution—only when the distance value was exceeded and the instruction was still in execution would a stall occur. Since the Horizon instruction contained three operations, this distance value was a worst-case value of all three operations along all possible paths. One obvious extension to this technique would be to use a unique distance value for each operation. This extension would increase the Horizon instruction size by 5% to 10% and would increase the complexity of the execution logic slightly to support carrying a distance value for each operation.

In the Cydra 5 processor, instead of using fixed memory latencies a memory latency register contained the effective memory latency value that the current code region was scheduled for. Using the memory latency register allowed the schedule to take into account the memory access pattern of a region of code and to reduce the scheduled memory latency in those cases where the memory system could approach its minimum latency. When memory references took a different amount of time to complete than the value in the memory latency register, the results were either buffered (when available early) or the pipelines were stalled (when available late) so that results appeared to be available precisely as schedule. This approach could be easily be extended to support an operation latency register for each operation or class of operations. This would not affect the instruction size (although there would need to be new instructions added to read and to modify these values) but would increase the complexity of the execution logic to support variable scheduled latencies for all operations.

Neither of these extensions appears to have significant performance gains although both may reduce the stall penalty in some cases; both of these extensions increase the complexity of the processor to support operations that have non-fixed latencies during execution. Using statically scheduled instructions with fixed virtual latencies avoids both of these inefficiencies and embeds a significant amount of dependency information in each instruction. There may yet be better approaches and when an efficient approach for embedding the full dependency graph in the instruction stream is developed then the situation may improve further—but this development is neither likely nor expected to achieve dramatic improvements over the current approach.

The third feature, the use of **split-issue** techniques, is less traditional and the remainder of this section is devoted to the topic. In the **split-issue** execution paradigm the execution of an operation is broken up into three independent sets of events that correspond to the three phases of operation execution—the acquisition of source values from their origination

(register file), the computation of result values (within execution resources), and the delivery of result values to their destination (register file). Each event in this scheme is scheduled at the virtual time that the architectural specification requires so that the implementation is able to maintain the illusion of the virtual processor. Temporary storage is used to hold the source and result values during this process which decouples the three phases from each other and allows them to be acted upon independently. There are a number of dependency issues that must be considered in order to ensure correctness but these are policy issues that are independent of (but allowed by) the model. This section will describe the splitissue paradigm in detail and will show how this model is directly applicable to the simulation of a wide range of high performance processors.

#### 3.1 An introduction to split-issue

The execution of an operation typically consists of three distinct phases—the acquisition of source values, the computation of result values, and the delivery of the completed results. In a traditional pipelined processor, these are often described as "register fetch", "execute", and "write-back" and are considered to be inseparable steps in the execution of an operation in the pipeline. In the split-issue model, these phases are decoupled from each other so that they can be treated independently in the implementation. In order to maintain the correctness of the virtual machine, each event is scheduled to take effect at the appropriate time based on the architectural specification for each operation. Whereas in the traditional pipeline, source, result, and intermediate values are held in latches in pipeline stages until conditions are set to proceed, in the split-issue model these are held in temporary storage locations.

The original concept for split-issue was presented in [3] as a mechanism for supporting a dynamic execution model for a static multi-operation issue processor. In the original model, operations were split into two independent micro-operations that operated in a producer-consumer relationship using an internal temporary register file to buffer results between the two micro-operations. Each micro-operation is scheduled to occur in the virtual cycle specified by the architecture. Thus the operation  $A \leftarrow f(B,C)$  with an architectural latency of  $3^{\sim}$  would be broken out into the two micro-operations  $T_1 \leftarrow f(B,C)$  @ 0 and  $A \leftarrow T_1$  @ 2 with the advantage that slip between these two micro-operations is allowed. In this nomenclature,  $x \leftarrow f(y)$  @ z indicates that the register (temporary or otherwise) x is assigned the value of the computation f(y) at the virtual time z. If there is no time specified then the result will be generated at some arbitrary time when it is ready. Note that the result of this example operation is available at the end of cycle 2—and can be used  $3^{\sim}$  from the start time as required by the architectural specification.

The original model supports the ability to dynamically schedule operations but limits these operations to those that can be supported in this simple two-step manner. However, the coupling of all source accesses with the operation may lead to unnecessary complexity when some source values are available and others are not. Reconsidering the events that occur during the execution of an operation leads to a revision of the two-step producer-consumer model to the three-step acquisition-computation-delivery model that provides additional capabilities.

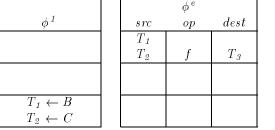

In the split-issue model, operations are split into into three independent phases— $\phi^1$  performs all acquisition events,  $\phi^e$  performs all computation, and  $\phi^2$  performs all delivery events. The  $\phi^1$  and  $\phi^2$  events are similar in that they are access events performing read and write accesses to the register file. Using the same example as before, in this model  $A \leftarrow f(B,C)$  results in the event triple

$$\phi^{1}: \quad T_{1} \leftarrow B @ 0 \qquad \qquad T_{2} \leftarrow C @ 0$$

$$\phi^{e}: \quad T_{3} \leftarrow f(T_{1}, T_{2})$$

$$\phi^{2}: \quad A \leftarrow T_{3} @ 2$$

Note that the  $\phi^e$  events do not need any timing information specified since they are able to commence once all operands are flagged as available.

With the exception of the separation of the acquisition events this approach accomplishes the same result as the original approach with the apparent addition of complexity. However, there are two benefits of this approach. First, there is only a single conceptual micro-operation that operates on the temporary storage values instead of two independent processing units—the acquisition and delivery of source and result values has been decoupled and is in many ways more like the traditional pipelined approach. Second, in addition to supporting basic operations like those supported in the original model, operations that allow events to occur at arbitrary cycles are also supported. One simple example is that of an operation with the late delivery of one operand—such as in a multiply-accumulate operation that forms the core of the SAXPY loop. This operation,  $S \leftarrow A * X + Y$ , can be specified such that only the two multiplicands (A and X) are required to start the operation and the summand (Y) is not required until later<sup>3</sup>. Using a 1<sup>-</sup> delay for the summand and a 3<sup>-</sup> operation latency, we have the triple

$$\phi^{1}: T_{1} \leftarrow A @ 0 & T_{2} \leftarrow X @ 0 & T_{3} \leftarrow Y @ 1 \\

\phi^{e}: T_{4} \leftarrow f(T_{1}, T_{2}) & T_{5} \leftarrow g(T_{4}, T_{3}) & \phi^{2}: A \leftarrow T_{5} @ 2$$

Note that in this example, the function f(a,x) is used as the first stage of processing of the multiply-accumulate that takes the two multiplicands as arguments and immediately sets the flag  $T_4$  (which could be an intermediate value from the computation) to represent that the computation has begun. The function g(t,z) is then used to provide the summand to the process and the final result is placed in the temporary  $T_5$ .

Arbitrarily complex operations may be constructed in this manner and even the most complex CISC processor operation can be framed in this form. For example, even indefinite iteration can be specified as in  $T_x, \dots \leftarrow h(T_x, \dots)$ . One tangential use of split-issue techniques might be the emulation of CISC processors—this use will not be considered further in this report.

An observation of the representation used in the above two examples is that it bears a striking resemblance to the information contained in a machine specification for the operations. In a machine readable form, this is essential information that a compiler would

<sup>&</sup>lt;sup>3</sup>Note that the multiply-accumulate operation is a reasonable example of the use of this approach and is *not* necessarily a recommendation for this specification!

need to schedule the operation and is also essential information that a processor designer would require to implement the same operation. This natural connection between specification and model is fortuitous—and the next section will demonstrate that there is a similar connection between the model and implementation as well.

One final point to make about the model concerns the timing of the events. It is clearly important to be able to model operations that take a single cycle to execute and to allow these to be supported back-to-back. Rather than to specify complex rules regarding the behavior of forwarding logic to deliver results and to provide values to execution events issuing the same cycle, this model adopts a simple read-execute-write sequence within a cycle. This is not a significant limitation since the problem can be resolved for many processor configurations by having the compiler schedule operations taking these delays into account and using operations that are specified to have the appropriate latencies for these cases. It is easy to conceive of a complex processor for which this approach would be inadequate but it is our belief that these processors are also too complex to reasonably consider building.

#### 3.2 A tabular representation for split-issue

While the representation presented in the previous section is useful for specifying the behavior of operations, it is not directly useful for an implementation—either hardware or simulator—due to the tagged nature of each of the acquisition and delivery events. However, there is an analogous table-based representation that embodies the same information in a similar manner to what can be seen to be efficiently implemented. In the tabular representation there are three columns that represent the three phases in the execution of the operation— $\phi^I$ ,  $\phi^e$ , and  $\phi^2$ . Thus the earlier example of the simple operation  $A \leftarrow f(B,C)$  is represented in this model as

In this representation, the first column corresponds to the  $\phi^1$  events and the third column corresponds to the  $\phi^2$  events. These operate as queues of events scheduled in virtual time with the bottom event being the current event. Thus, for this example, the acquisition events  $T_1 \leftarrow B$  and  $T_2 \leftarrow C$  are scheduled as the next events to be processed and the delivery event  $A \leftarrow T_3$  is scheduled to occur two cycles later as specified. As events are processed, all events in the queues progress one cycle just as in a queue. The behavior is only half like a queue since events are inserted at their appropriate virtual time and not at the very top, but the queue analogy is a useful one in understanding the sequencing of event processing.

The second column is corresponds to the  $\phi^e$  events and is used more as a scoreboard of pending operations than as a queue. This example reflects that the source values for the operation shown are in temporary storage  $T_1$  and  $T_2$  and that the result value will be placed in temporary storage  $T_3$ . Note that, although there is a required correlation between the positions in the  $\phi^1$  and  $\phi^2$  queues, there is no correlation between the positions in the  $\phi^1$  and  $\phi^2$  queues and the entries in the  $\phi^e$  structure. While the  $\phi^e$  structure may maintain the ordering of operations<sup>4</sup> there is no requirement that it do so.

In the examples that follow, all operations will be limited to a single source and destination operand and will avoid the use of temporary storage labels. This simplifies the examples and demonstrates the use of the model without any loss of generality—but with significantly less complexity than actually tracking multiple source and destination values using more realistic operations. Another simplification is that the tabular representation will be "preloaded" at the start of the example and will not show the sequential filling that would normally occur during a step-by-step execution process. However, all events are listed in the places that they would be relative to the first operation that is inserted so the events that are processed will be dealt with appropriately.

The following demonstrates the use of this representation for hypothetical code starting at cycle 1000:

Cycle 1000

| $\phi^{1}$                    |

|-------------------------------|

|                               |

|                               |

| $g:\mathrm{r}(\mathcal{R}_1)$ |

|           | $\phi^{e}$ |      |

|-----------|------------|------|

| src       | op         | dest |

| $\sqrt{}$ | (f)        |      |

| _         | g          |      |

|           | h          | _    |

| $\phi^{2}$                    |

|-------------------------------|

| $h:\mathrm{w}(\mathcal{R}_1)$ |

|                               |

|                               |

| $f:\mathrm{w}(\mathcal{R}_2)$ |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 3 |

| $\mathcal{R}_2 =$ | ? |

|                   |   |

This example represents three arbitrary operations labeled "f", "g", and "h". The parenthesis on operation f represent that the operation has started computation. In the state represented, the acquisition for operation f is completed (represented by the " $\sqrt{}$ " mark) and the operation has started computation; however, the "—" in the destination for f indicates that there is a result value but it is not available yet. The delivery event for operation f is shown below the  $\phi^2$  event queue as " $f: w(\mathcal{R}_2)$ "—this placement indicates that this event was scheduled to be executed before the operation actually completed computation and is "late"—this also is reflected in the "?" in register  $\mathcal{R}_2$  indicating an unknown value.

Operation g is waiting for its source value (this is the next acquisition event to execute) and has no result and operation h has no source value but generates a result. Neither of these operations has started execution yet although it may be possible to start operation h depending on how dependencies are handled (operation h writes the same register that operation h is waiting to read). One key feature of this model is that a number of aspects of an implementation—such as how dependencies and late results are handled—are not a part of the model but can be specified independently.

One use of operation ordering in the  $\phi^e$  structure is to implement precise interrupts.

#### 3.3 Representation of a traditional static multi-operation issue processor

As a real example to start off with, consider a bare-bones static multi-operation issue with no dynamic behavior of any kind—typical of a traditional VLIW processor (although for the purposes of this example, all operation latencies are 1° for simplicity). For this example, we will use the following code sequence:

$$\mathcal{R}_2 \ \leftarrow \ f(\mathcal{R}_1)$$

$$\mathcal{R}_3 \leftarrow g(\mathcal{R}_2)$$

$$\begin{array}{cccc} \mathcal{R}_3 & \leftarrow & g(\mathcal{R}_2) \\ \mathcal{R}_2 & \leftarrow & h(\mathcal{R}_3) \end{array}$$

There are two dependencies in this code (each operation is immediately dependent on its predecessor). However, since the compiler guarantees that there are no scheduling problems the processor can execute the code stream without regard to any potential dependencies. These operations generate results that correspond to the operation. The first operation thus generates the result f and so forth. Initial values correspond to the register number for simplicity.

Thus, we initially have

Cycle 0

| •                             |     |  |

|-------------------------------|-----|--|

|                               |     |  |

| $\phi^{1}$                    | src |  |

| $h:\mathrm{r}(\mathcal{R}_3)$ |     |  |

| $g:\mathrm{r}(\mathcal{R}_2)$ | -   |  |

| $f:\mathrm{r}(\mathcal{R}_1)$ |     |  |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | f          |      |

| -   | g          | _    |

|     | h          |      |

|     |            |      |

| $\phi^{2}$                     |

|--------------------------------|

| $h: \mathrm{w}(\mathcal{R}_2)$ |

| $g: \mathrm{w}(\mathcal{R}_3)$ |

| $f: \mathbf{w}(\mathcal{R}_2)$ |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | 2 |

| $\mathcal{R}_3 =$ | 3 |

After executing the first cycle we read  $\mathcal{R}_1$ , issue operation 1, and write  $\mathcal{R}_2$  and this results in

Cycle 1

| $\phi^{1}$                    |

|-------------------------------|

|                               |

| $h: r(\mathcal{R}_3)$         |

| $g:\mathrm{r}(\mathcal{R}_2)$ |

|              | $\phi^{e}$ |      |

|--------------|------------|------|

| src          | op         | dest |

| $\checkmark$ | (f)        |      |

|              | g          | _    |

|              | h          | _    |

|              |            |      |

| $\phi^{2}$                     |  |

|--------------------------------|--|

| $h: \mathrm{w}(\mathcal{R}_2)$ |  |

| $g: \mathbf{w}(\mathcal{R}_3)$ |  |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | f |

| $\mathcal{R}_3$ = | 3 |

Similarly we execute the second cycle and get

Cycle 2

| $\phi^{1}$                    |

|-------------------------------|

|                               |

|                               |

| $h:\mathrm{r}(\mathcal{R}_3)$ |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (f)        |      |

|     | (g)        |      |

| _   | h          |      |

| $\phi^{2}$                     |

|--------------------------------|

|                                |

|                                |

| $h: \mathrm{w}(\mathcal{R}_2)$ |

| B ' ( E7                                 |   |

|------------------------------------------|---|

| $\frac{Register\ File}{\mathcal{R}_1 =}$ | 1 |

| $\mathcal{R}_2$ =                        | f |

| $\mathcal{R}_3 =$                        | g |

And finally we execute the third cycle and get

Cycle 3

| $\phi^{1}$ |

|------------|

|            |

|            |

|            |

|           | $\phi^{e}$ |      |

|-----------|------------|------|

| src       | op         | dest |

|           | (f)        |      |

| $\sqrt{}$ | (g)        |      |

|           | (h)        |      |

|   | $\phi^{2}$ |

|---|------------|

|   |            |

| Ī |            |

| ĺ |            |

| Register Fil      | le |

|-------------------|----|

| $\mathcal{R}_1$ = | 1  |

| $\mathcal{R}_2$ = | h  |

| $\mathcal{R}_3 =$ | f  |

The code operates in 3° as scheduled—not surprising since traditional static multioperation issue architectures do not allow any unpredictability in the behavior of their operations.

#### Further examples of split-issue techniques 3.4

We now consider a configuration that relies on split-issue techniques to maintain correctness. As a first example of the abilities of split-issue to resolve problems with schedule difficulties, consider the same code sequence as before with the exception that each operation now has an architectural latency of  $2^{\sim}$  while the code is scheduled for the virtual latency of  $1^{\sim}$ .

We have the same initial condition of the example in the previous section of

Cycle 0

| v                              |

|--------------------------------|

|                                |

| $\phi^{1}$                     |

| $h:\mathrm{r}(\mathcal{R}_3)$  |

| $g:\mathrm{r}(\mathcal{R}_2)$  |

| $f: \mathbf{r}(\mathcal{R}_1)$ |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | f          | —    |

|     | g          |      |

| _   | h          | _    |

| $\phi^{2}$                     |

|--------------------------------|

| $h:\mathrm{w}(\mathcal{R}_2)$  |

| $g: \mathrm{w}(\mathcal{R}_3)$ |

| $f: \mathrm{w}(\mathcal{R}_2)$ |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | 2 |

| $\mathcal{R}_3$ = | 3 |

After the first cycle we've issued the first computation but it hasn't completed yet. We thus have the following situation where the first write must be held until it is ready. We thus have

Cycle 1

| $\phi^{1}$                     |

|--------------------------------|

|                                |

| $h: \mathrm{r}(\mathcal{R}_3)$ |

| $g:\mathrm{r}(\mathcal{R}_2)$  |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (f)        | _    |

|     | g          |      |

|     | h          |      |

| $\phi^{2}$                     |

|--------------------------------|

| $h:\mathrm{w}(\mathcal{R}_2)$  |

| $g:\mathrm{w}(\mathcal{R}_3)$  |

| $f: \mathbf{w}(\mathcal{R}_2)$ |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | ? |

| $\mathcal{R}_3$ = | 3 |

|                   |   |

After the next cycle we retire the first computation but can't start the second since the read hasn't occurred yet. We get

Cycle 2

| - J                            |

|--------------------------------|

| $\phi^{1}$                     |

|                                |

|                                |

| $h: \mathrm{r}(\mathcal{R}_3)$ |

| $g: \mathrm{r}(\mathcal{R}_2)$ |

|           | $\phi^{e}$ |      |

|-----------|------------|------|

| src       | op         | dest |

| $\sqrt{}$ | (f)        |      |

|           | g          | _    |

|           | h          |      |

|           |            |      |

| $\phi^{2}$                     |

|--------------------------------|

|                                |

| $h: \mathrm{w}(\mathcal{R}_2)$ |

| $g: \mathbf{w}(\mathcal{R}_3)$ |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | f |

| $\mathcal{R}_3=$  | ? |

Now we can start the second but have to deal with the deferred write and the new deferred read and write, thus

Cycle 3

| v                        |  |

|--------------------------|--|

|                          |  |

| $\phi^{1}$               |  |

|                          |  |

|                          |  |

|                          |  |

| $h \cdot n(\mathcal{D})$ |  |

$$h: \mathrm{r}(\mathcal{R}_3)$$

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (f)        |      |

|     | (g)        | -    |

|     | h          |      |

$h: \mathrm{w}(\mathcal{R}_2)$  $g: \mathbf{w}(\mathcal{R}_3)$

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1 =$ | 1 |

| $\mathcal{R}_2$ = | ? |

| $\mathcal{R}_3=$  | ? |

With the end if the first cycle of the second operation we have the result posted but the third operation has not yet read its register so does not immediately reflect the result. Thus,

Cycle 4

| Cycle 1                        | _ |   |

|--------------------------------|---|---|

| $\phi^{1}$                     |   | s |

|                                |   | 1 |

|                                |   | 1 |

|                                |   | _ |

| $h: \mathrm{r}(\mathcal{R}_3)$ |   |   |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (f)        |      |

|     | (g)        |      |

|     | h          |      |

|     |            |      |

|   | $\phi^{2}$                     |  |

|---|--------------------------------|--|

|   |                                |  |

|   |                                |  |

| _ | $h: \mathrm{w}(\mathcal{R}_2)$ |  |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | ? |

| $\mathcal{R}_3 =$ | g |

The third operation completes its read and issues

Cycle 5

|           | $\phi^{e}$ |              |

|-----------|------------|--------------|

| src       | op         | dest         |

| $\sqrt{}$ | (f)        |              |

| $\sqrt{}$ | (g)        | $\checkmark$ |

|           | (h)        | _            |

| -         | -          |              |

|   | $\phi^{2}$                    |

|---|-------------------------------|

|   |                               |

|   |                               |

| _ | $h:\mathrm{w}(\mathcal{R}_2)$ |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | ? |

| $\mathcal{R}_3=$  | g |

And after its second cycle the third operation completes and updates its result thusly

Cycle 6

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (f)        |      |

|     | (g)        |      |

|     | (h)        |      |

| $\phi^{2}$ |

|------------|

|            |

|            |

|            |

| Register File     |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | h |

| $\mathcal{R}_3$ = | g |

This has taken a total of 6 cycles—exactly what would have been scheduled by the compiler had it know that the latency for the operations were doubled. This is also the same amount of time that it would have taken a double-cycled static multi-operation issue processor although operations would not have been executed with the same timing.

The next example will demonstrate a more realistic situation where **split-issue** is useful—a mis-scheduled memory load operation that takes  $5^{\circ}$  to complete instead of the scheduled  $2^{\circ}$ . This is representative of a first level cache miss which is a hit in the second level cache. Other operations will be included and will serve to mitigate the cost of the load. All other operations are scheduled to complete in  $1^{\circ}$ . The code sequence to be considered is as follows:

$$\mathcal{R}_{3} \leftarrow ld(\mathcal{R}_{1}) \\

\leftarrow f(\mathcal{R}_{2}) \\

\mathcal{R}_{5} \leftarrow use(\mathcal{R}_{3}) \\

\mathcal{R}_{6} \leftarrow g(\mathcal{R}_{1}) \\

\mathcal{R}_{7} \leftarrow h(\mathcal{R}_{5}) \\

\mathcal{R}_{8} \leftarrow k(\mathcal{R}_{6})$$

This sequence takes 6 to complete as scheduled.

For this example we have the initial setup of

Cycle 0

| $\phi^{1}$                       |

|----------------------------------|

| $k: \mathrm{r}(\mathcal{R}_6)$   |

| $h:\mathrm{r}(\mathcal{R}_5)$    |

| $g:\mathrm{r}(\mathcal{R}_1)$    |

| $use: \mathrm{r}(\mathcal{R}_3)$ |

| $f: \mathrm{r}(\mathcal{R}_2)$   |

| $ld: \mathbf{r}(\mathcal{R}_1)$  |

|     | 10         |      |

|-----|------------|------|

|     | $\phi^{e}$ |      |

| src | op         | dest |

| _   | ld         |      |

| _   | f          |      |

| _   | use        |      |

| _   | g          |      |

|     | h          |      |

|     | k          |      |

|     |            |      |

| $\phi^{2}$                       |

|----------------------------------|

| $k: \mathrm{w}(\mathcal{R}_8)$   |

| $h:\mathrm{w}(\mathcal{R}_7)$    |

| $g:\mathrm{w}(\mathcal{R}_6)$    |

| $use: \mathrm{w}(\mathcal{R}_5)$ |

| $ld: \mathrm{w}(\mathcal{R}_3)$  |

|                                  |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | 2 |

| $\mathcal{R}_3$ = | 3 |

| $\mathcal{R}_4$ = | 4 |

| $\mathcal{R}_5$ = | 5 |

| $\mathcal{R}_6$ = | 6 |

| $\mathcal{R}_7$ = | 7 |

| $\mathcal{R}_8 =$ | 8 |

After the first operation, the load operation, we have the following state:

Cycle 1

| •                                |

|----------------------------------|

| $\phi^{1}$                       |

|                                  |

| $k: \mathbf{r}(\mathcal{R}_6)$   |

| $h:\mathrm{r}(\mathcal{R}_5)$    |

| $g:\mathrm{r}(\mathcal{R}_1)$    |

| $use: \mathrm{r}(\mathcal{R}_3)$ |

| $f: r(\mathcal{R}_2)$            |

|                                  |

|           | $\phi^{e}$ |      |

|-----------|------------|------|

| src       | op         | dest |

| $\sqrt{}$ | (ld)       | _    |

|           | f          |      |

| _         | use        | _    |

| _         | g          | _    |

|           | h          |      |

| _         | k          | _    |

| $\phi^{2}$                       |

|----------------------------------|

|                                  |

| $k: \mathrm{w}(\mathcal{R}_8)$   |

| $h:\mathrm{w}(\mathcal{R}_7)$    |

| $g:\mathrm{w}(\mathcal{R}_6)$    |

| $use: \mathrm{w}(\mathcal{R}_5)$ |

| $ld: w(\mathcal{R}_3)$           |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | 2 |

| $\mathcal{R}_3$ = | 3 |

| $\mathcal{R}_4$ = | 4 |

| $\mathcal{R}_5$ = | 5 |

| $\mathcal{R}_6$ = | 6 |

| $\mathcal{R}_7$ = | 7 |

| $\mathcal{R}_8$ = | 8 |

So far, so good—the load was supposed to take  $2^{\sim}$  to begin with so we can easily deal with the next operation. Thus

Cycle 2

| C J 010 =                        |

|----------------------------------|

| $\phi^{1}$                       |

|                                  |

|                                  |

| $k:\mathrm{r}(\mathcal{R}_6)$    |

| $h:\mathrm{r}(\mathcal{R}_5)$    |

| $g:\mathrm{r}(\mathcal{R}_1)$    |

| $use: \mathrm{r}(\mathcal{R}_3)$ |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (ld)       |      |

|     | (f)        |      |

|     | use        |      |

|     | g          |      |

|     | h          |      |

| _   | k          |      |

| $\phi^{2}$                       |

|----------------------------------|

|                                  |

|                                  |

|                                  |

| $k:\mathrm{w}(\mathcal{R}_8)$    |

| $h:\mathrm{w}(\mathcal{R}_7)$    |

| $g:\mathrm{w}(\mathcal{R}_6)$    |

| $use: \mathrm{w}(\mathcal{R}_5)$ |

| $ld: \mathrm{w}(\mathcal{R}_3)$  |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2$ = | 2 |

| $\mathcal{R}_3$ = | ? |

| $\mathcal{R}_4$ = | 4 |

| $\mathcal{R}_5$ = | 5 |

| $\mathcal{R}_6$ = | 6 |

| $\mathcal{R}_7$ = | 7 |

| $\mathcal{R}_8$ = | 8 |

Now we see the problem—the load operation has not completed but the next operation requires the result. Thus this operation is pended as follows and processing continues, giving

#### Cycle 3

|        | $\phi^{1}$         |

|--------|--------------------|

|        |                    |

|        |                    |

|        |                    |

|        | $r(\mathcal{R}_6)$ |

| h:     | $r(\mathcal{R}_5)$ |

| g:     | $r(\mathcal{R}_1)$ |

| use :: | $r(\mathcal{R}_3)$ |

|           | $\phi^{e}$      |      |

|-----------|-----------------|------|

| src       | $\phi^{e}$ $op$ | dest |

| $\sqrt{}$ | (ld)            | _    |

|           | (f)             |      |

|           | use             | _    |

| _         | g               |      |

|           | h               |      |

|           | k               | _    |

|           |                 |      |

| $\phi^{2}$                       |

|----------------------------------|

|                                  |

|                                  |

|                                  |

| $k:\mathrm{w}(\mathcal{R}_8)$    |

| $h:\mathrm{w}(\mathcal{R}_7)$    |

| $g:\mathrm{w}(\mathcal{R}_6)$    |

| $use: \mathrm{w}(\mathcal{R}_5)$ |

| $ld:\mathrm{w}(\mathcal{R}_3)$   |

|                                  |

| Register File       |   |

|---------------------|---|

| $\mathcal{R}_1$ =   | 1 |

| $\mathcal{R}_2^{=}$ | 2 |

| $\mathcal{R}_3$ =   | ? |

| $\mathcal{R}_4$ =   | 4 |

| $\mathcal{R}_5$ =   | ? |

| $\mathcal{R}_6$ =   | 6 |

| $\mathcal{R}_7$ =   | 7 |

| $\mathcal{R}_8$ =   | 8 |

While the last operation was pended, the next can proceed since it is not dependent on the load but on the operation following the load. Thus we have this operation complete "out of order" with respect to the earlier operations. We then see

Cycle 4

| _ Cyclc 1                                                        |

|------------------------------------------------------------------|

| $\phi^{1}$                                                       |

|                                                                  |

|                                                                  |

|                                                                  |

|                                                                  |

| $k:\mathrm{r}(\mathcal{R}_6)$                                    |

| $rac{k:\mathrm{r}(\mathcal{R}_6)}{h:\mathrm{r}(\mathcal{R}_5)}$ |

| $use: \mathrm{r}(\mathcal{R}_3)$                                 |

|     | $\phi^{e} \ op$ |      |

|-----|-----------------|------|

| src |                 | dest |

|     | (ld)            | _    |

|     | (f)             |      |

| _   | (use)           | _    |

|     | (g)             |      |

| _   | h               |      |

| _   | k               |      |

|     | •               | -    |

| . 0                              |

|----------------------------------|

| $\phi^{2}$                       |

|                                  |

|                                  |

|                                  |

|                                  |

| $k:\mathrm{w}(\mathcal{R}_8)$    |

| $h:\mathrm{w}(\mathcal{R}_7)$    |

| $use: \mathrm{w}(\mathcal{R}_5)$ |

| $ld:\mathrm{w}(\mathcal{R}_3)$   |

| $Register\ File$  |   |

|-------------------|---|

| $\mathcal{R}_1$ = | 1 |

| $\mathcal{R}_2 =$ | 2 |

| $\mathcal{R}_3$ = | ? |

| $\mathcal{R}_4$ = | 4 |

| $\mathcal{R}_5$ = | ? |

| $\mathcal{R}_6$ = | g |

| $\mathcal{R}_7$ = | 7 |

| $\mathcal{R}_8$ = | 8 |

The next operation depends on the operation stalled by the load operation and we must pend it too. However, the load completes in this cycle so it and its dependent operation are updated giving

Cycle 5

| - J                                                              |

|------------------------------------------------------------------|

| $\phi^{1}$                                                       |

|                                                                  |

|                                                                  |

|                                                                  |

|                                                                  |

|                                                                  |

| $rac{k:\mathrm{r}(\mathcal{R}_6)}{h:\mathrm{r}(\mathcal{R}_5)}$ |

| $h:\mathrm{r}(\overline{\mathcal{R}}_5)$                         |

|     | $\phi^{e}$ |      |

|-----|------------|------|

| src | op         | dest |

|     | (ld)       |      |

|     | (f)        |      |

|     | (use)      |      |

|     | (g)        |      |

|     | h          | _    |

|     | k          | _    |

|     |            | -    |

| $\phi^{2}$                       |  |

|----------------------------------|--|

| φ                                |  |

|                                  |  |

|                                  |  |

|                                  |  |

|                                  |  |

|                                  |  |

| $k: \mathrm{w}(\mathcal{R}_8)$   |  |

| $h: \mathrm{w}(\mathcal{R}_7)$   |  |

| $use: \mathrm{w}(\mathcal{R}_5)$ |  |

| $Register\ File$  |    |

|-------------------|----|

| $\mathcal{R}_1$ = | 1  |

| $\mathcal{R}_2$ = | 2  |

| $\mathcal{R}_3$ = | ld |

| $\mathcal{R}_4$ = | 4  |

| $\mathcal{R}_5$ = | ?  |

| $\mathcal{R}_6$ = | g  |

| $\mathcal{R}_7 =$ | ?  |

| $\mathcal{R}_8 =$ | 8  |

This cycle we are (potentially) able to issue both  $\phi^1$  operations use and k since both are ready—this is shown here. Thus we now have one operation left to process:

| Cycle 6                                      |              | $\phi^{e}$                                                                 |                         |                                         |                                                                                                                                      |           |

|----------------------------------------------|--------------|----------------------------------------------------------------------------|-------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------|

| $\phi^{1}$                                   | src          | $\stackrel{^{	au}}{op}$                                                    | dest                    | $\phi^{2}$                              | Register F                                                                                                                           | ile       |

|                                              | $\sqrt{}$    | (ld)                                                                       |                         |                                         | $\mathcal{R}_1$ =                                                                                                                    |           |

|                                              | $\sqrt{}$    | (f)                                                                        |                         |                                         | $\mathcal{R}_2$ =                                                                                                                    |           |

|                                              | $\sqrt{}$    | (use)                                                                      | $\sqrt{}$               |                                         | $\mathcal{R}_3 =$                                                                                                                    |           |

|                                              | $\sqrt{}$    | (g)                                                                        | $\sqrt{}$               |                                         | $\mathcal{R}_4$ =                                                                                                                    |           |

|                                              |              | h                                                                          |                         |                                         | $\mathcal{R}_5 =$                                                                                                                    | u         |

|                                              |              | (k)                                                                        | $\sqrt{}$               |                                         | $\mathcal{R}_6=$                                                                                                                     |           |

| 1 (D)                                        |              |                                                                            |                         |                                         |                                                                                                                                      |           |

| $h: \mathrm{r}(\mathcal{R}_5)$ And after the | e final exec | cution v                                                                   | we have                 | $h:\mathrm{w}(\mathcal{R}_7)$           | ${\cal R}_7= \ {\cal R}_8=$                                                                                                          |           |

|                                              | e final exec |                                                                            | we have                 | $h:\mathrm{w}(\mathcal{R}_7)$           |                                                                                                                                      |           |

| And after the                                | e final exec | $\phi^{e}$                                                                 |                         |                                         | $\mathcal{R}_8$ =                                                                                                                    | ile       |

| And after the                                |              |                                                                            | we have $\frac{dest}{}$ | $h: \mathrm{w}(\mathcal{R}_7)$ $\phi^2$ | $\mathcal{R}_{8}$ =                                                                                                                  | ile       |

| And after the                                |              | $\phi^{e} \ op$                                                            |                         |                                         | $\mathcal{R}_8$ =                                                                                                                    | ile       |

| And after the                                |              | $\phi^{e} \ op \ (ld)$                                                     |                         |                                         | $\mathcal{R}_8$ = $ \begin{array}{c} \mathcal{R}_8 = \\ \mathcal{R}_1 = \\ \mathcal{R}_2 = \\ \mathcal{R}_3 = \end{array} $          |           |

| And after the                                |              | $\begin{array}{c} \phi^e \\ op \\ (ld) \\ (f) \\ (use) \\ (g) \end{array}$ |                         |                                         | $\mathcal{R}_8=$ $\begin{array}{c} \mathcal{R}_8=\\ \mathcal{R}_1=\\ \mathcal{R}_2=\\ \mathcal{R}_3=\\ \mathcal{R}_4=\\ \end{array}$ |           |

| And after the                                |              | $ \phi^{e} $ $ op $ $ (ld) $ $ (f) $ $ (use) $                             |                         |                                         | $\mathcal{R}_8$ = $ \begin{array}{c} \mathcal{R}_8 = \\ \mathcal{R}_1 = \\ \mathcal{R}_2 = \\ \mathcal{R}_3 = \end{array} $          | ile<br>u: |

From this example it is clear that there was a 1<sup>-</sup> penalty from the increased latency of the *ld* operation due to a cache miss. Had the miss been scheduled for by the compiler there would not have been any penalty at all since other operations could have been scheduled in to the stall slots—however, this is not the typical situation in non-loop code and the use of dynamic scheduling will benefit these cases.

$\mathcal{R}_8 =$

k

#### 4 The NYFO VLIW model

The NYFO VLIW architectural model is based on the split-issue execution paradigm described in section 3 and allows the specification of a wide range of processor configurations through the use of different policies to control the transitions within the split-issue framework. At a high level—that of the virtual processor—the NYFO VLIW architectural model has the structure of a traditional static multi-operation issue machine. Instructions are fetched, decoded, issued, and executed precisely as scheduled. At a low level—that of the implementation processor—the NYFO VLIW architectural model has very different characteristics than the traditional static multi-operation issue. Latencies may differ from the architectural specification and resources may have contention for their use. This section describes the characteristics of the architectural model in detail and identifies the aspects of the model that provide the flexibility to model a wide range of architectures.

#### 4.1 Stages in an NYFO VLIW model

The NYFO VLIW architectural model is organized as a sequence of four basic stages which are fetch, decode, invoke, and compute. These stages correspond to the major actions that occur within the NYFO VLIW architectural model and do not necessarily correspond to separate pipeline stages. Specific details on the ordering of events within any particular implementation are modeled by policies which provide for both event handling and time (cost) accounting.

The fetch stage is responsible for maintaining the code stream supply to the decode stage for processing. Unless otherwise directed, it continues to fetch contiguous memory along the current fetch path. Using branch prediction, other stages (primarily decode and compute) can adjust the fetch path to try and reduce the effective latency of branches. The fetch stage is not concerned with the boundaries and format of instructions—only the maintenance of a ready memory stream for the decode stage.

The decode stage assembles instructions from the memory stream provided by the fetch stage and delivers the assembled instructions to the invoke stage. Instruction assembly can be a simple or complex problem depending on the encoding used and whether or not the instruction stream is compressed to reduce the memory footprint. In the simple case, instructions are fixed size packets that are easily assembled. The problem with this simple scheme is that not all operation slots in an instruction are always filled and the presence of many unused operations in an instruction results in an inefficiently used instruction memory hierarchy. An alternative to the simple encoding is to use some form of compression—a tradeoff between memory utilization and decode complexity. This research may look into the characteristics of different encoding and compression schemes at a later point but these will not be considered further in this report. The delivered instructions are not just copies of uncompressed instructions from memory but are templates of the actions that are required by the architectural specification. This information is then processed by the invoke stage.

The invoke stage receives the assembled instruction template from the decode stage, adds in any dynamic information that is required for each contained operation, and delivers the specified actions to the compute stage for computation. This stage bears a strong resemblance to the instruction issue stage in a traditional processor and is effectively the instruction issue stage of the virtual processor. However, the notion of invoking instructions to generate and deliver the dynamic event instances reduces confusion with other points of issue within the implementation. Section 4.2 describes the actions of this stage in detail.

The compute stage continuously processes the events that have been delivered to it by the invoke stage. Specifics of when events are processed and how late events are handled are provided by the policies for a particular configuration. The invoke stage ensures that the events are scheduled for execution according to the implementation specification and the compute stage processes these events accordingly performing whatever actions are necessary to maintain the illusion of the virtual processor. Section 4.3 describes the actions of this stage in detail and introduces the aspects that are governed by specific policies.

#### 4.2 Elaboration on the invoke stage

The invocation of an instruction results in two primary actions that are performed within the invoke stage. These actions are the collection and merging of relevant processor configuration information with the individual operations and the delivery of the operation events to the compute stage.

The view that the compiler has of an operation is that events occur at specific times based on the architectural specification. The compiler schedules operations into specific instructions based on the availability of results and on its view of the configuration of the processor at the scheduled cycle. Each operation is placed into a specific slot in the instruction which may be restricted in which operations may be placed there. These slots correspond to execution resources within the virtual processor. In the ideal processor, there are sufficient resources to satisfy all possible operation configurations without contention. In the NYFO VLIW architectural model there is a split-issue structure ( $\phi^1$ ,  $\phi^e$ , and  $\phi^2$ ) that corresponds to each slot—there may or may not be an execution resource that corresponds to each slot depending on the details of the implementation.