# PRODUCER-ORIENTED VERSUS CONSUMER-ORIENTED PREFETCHING:

# A COMPARISON AND ANALYSIS OF PARALLEL APPLICATION PROGRAMS

Moriyoshi Ohara

**TECHNICAL REPORT: CSL-TR-96-695**

**June 1996**

This research has been supported by ARPA under contracts N00039-91-C-0138 and DABT63-94-C-0054, and IBM Japan, Ltd.

# PRODUCER-ORIENTED VERSUS CONSUMER-ORIENTED PREFETCHING: A COMPARISON AND ANALYSIS OF PARALLEL APPLICATION PROGRAMS

#### Moriyoshi Ohara

**Technical Report: CSL-TR-96-695**

June, 1996

Computer Systems Laboratory

Department of Electrical Engineering and Computer Systems

Stanford University

Gates Building, A-408

Stanford, CA 94305-9040

pubs@shasta.stanford.edu

#### **Abstract**

Due to large remote-memory latencies, reducing the impact of cache misses is critical for large scale shared-memory multiprocessors. This thesis quantitatively compares two classes of software-controlled prefetch schemes for reducing the impact: consumer-oriented and producer-oriented schemes. Examining the behavior of these schemes leads us to characterize the communication behavior of parallel application programs.

Consumer-oriented prefetch has been shown to be effective for hiding large memory latencies. Producer-oriented prefetch (called deliver), on the other hand, has not been extensively studied. Our implementation of deliver uses a hardware mechanism that tracks the set of potential consumers based on past sharing patterns. Qualitatively, deliver has an advantage since the producer sends the datum as soon as, but not before, it is ready for use. In contrast, prefetch may fetch the datum too early so that it is invalidated before use, or may fetch it too late so that the datum is not yet available when it is needed by the consumer. Our simulation results indeed show that the qualitative advantage of deliver can yield a slight performance advantage when the cache size and the memory latency are very large. Overall, however, deliver turns out to be less effective than prefetch for two reasons. First, prefetch benefits from a "filtering effect," and thus generates less traffic than deliver. Second, deliver suffers more from cache interference than prefetch. The sharing and temporal characteristics of a set of parallel applications are shown to account for the different behavior of the two prefetch schemes. This analysis shows the inherent difficulties in predicting future communication behavior of parallel applications from recent history of the application behavior. This suggests that cache accesses involved with coherency in general are much less predictable based on past behavior than other types of cache behavior.

**Key Words and Phrases:** prefetching, latency hiding, data sharing, cache coherency, shared-memory multiprocessors.

© Copyright by Moriyoshi Ohara 1996 All Rights Reserved

## Acknowledgments

Without assistance of many people, this dissertation could not have been realized. Especially, I thank my principal advisor, John Hennessy, for his wisdom and guidance throughout my graduate study at Stanford. I also thank Anoop Gupta, Monica Lam, and Arogyaswami Paulraj for their insights on my dissertation work.

I thank all of my colleagues for making my student life at the farm stimulating. I also thank faculty and students of the DASH/FLASH project. J.P. Singh and Todd Mowry gave me valuable insights for my research. Steve Goldschmidt made tango simulator available to me. Truman Joe gave me a part of his simulation program. I thank Dave Ofelt and Jeff Kuskin as a great officemate. I also thank Steve Woo and Evan Torrie who are insightful and fun to work with.

My thanks also go to support stuffs at Stanford: Charlie Orgish and Thoi Nguyen for keeping the computers running, and Margaret Rowland and Darlene Hadding for making my school life easier. My graduate study was supported by ARPA under contracts N00039-91-C-0138 and DABT63-94-C-0054, and IBM Japan, Ltd. Finally I thank my family, especially my wife, Kyoko, who has shared a graduate student life with me from the beginning.

# **Contents**

| Acknowledgments |                                                               |           |

|-----------------|---------------------------------------------------------------|-----------|

| Chapter         | 1 Introduction                                                | 1         |

| 1.              | 1 Related Work                                                | . 3       |

|                 | 1.1.1 Optimizing Cache Protocols                              | . 3       |

|                 | 1.1.2 Combining Shared-Memory and Message-Passing Paradigms   | 11        |

|                 | 1.1.3 Summary                                                 | 12        |

| 1.              | 2 Research Goals                                              | 13        |

| 1.              | 3 Contributions                                               | 14        |

| 1.              | 4 Organization of Dissertation                                | 14        |

| Chapter         | 2 Producer-oriented and Consumer-oriented Approaches          | 17        |

| 2.              | 1 Producer-oriented Deliver                                   | 17        |

|                 | 2.1.1 Strategy for Inserting Deliver Operations               | 19        |

|                 | 2.1.2 Hardware Mechanisms for the Deliver Operation           | 21        |

|                 | 2.1.3 Variations on the Deliver Operation                     | 24        |

| 2.              | 2 Consumer-oriented Prefetch                                  | 27        |

| Chapter         | 3 Experimental Environment                                    | 29        |

| 3.              | 1 Simulation Methodology                                      | 29        |

|                 | 3.1.1 Execution-Driven Simulation                             | 29        |

|                 | 3.1.2 Designing Experiments                                   | 31        |

| 3.              | 2 Benchmark Programs                                          | 33        |

| Chapter         | 4 Sharing Characteristics of Parallel Applications            | <b>37</b> |

| 4.              | 1 Producer-oriented Deliver                                   | 38        |

|                 | 4.1.1 Background                                              | 38        |

|                 | 4.1.2 Sharing Characteristics from the Consumer's Perspective | 42        |

| 4.1.3 Sharing Characteristics from the Producer's Perspective       | 50  |

|---------------------------------------------------------------------|-----|

| 4.1.4 Application Algorithms and Deliver Operation Behavior         | 57  |

| 4.1.5 Summary                                                       | 72  |

| 4.2 Consumer-oriented Prefetch                                      | 73  |

| 4.2.1 Coverage and Efficiency of Prefetch Operations                | 75  |

| 4.2.2 Efficiency Comparison between Prefetch and Deliver Operations | 77  |

| 4.2.3 Application Algorithms and Prefetch Operation Behavior        | 81  |

| 4.2.4 Summary                                                       | 87  |

| 4.3 Chapter Summary                                                 | 87  |

| Chapter 5 Real Architectural Effects                                | 89  |

| 5.1 Cache Size                                                      | 89  |

| 5.1.1 Cache Conflicts                                               | 90  |

| 5.1.2 Temporal Characteristics                                      | 92  |

| 5.1.3 Replacement Policies                                          | 99  |

| 5.1.4 Classification of Cache Misses                                | 101 |

| 5.1.5 Cache Miss Rate versus Cache Size                             | 103 |

| 5.1.6 Working-Set Characteristics                                   | 107 |

| 5.1.7 Cache Associativity                                           | 112 |

| 5.2 Line Size                                                       | 114 |

| 5.2.1 Effect of Large Lines for Large Caches                        | 116 |

| 5.2.2 Interactions Between Line-Size and Cache-Size Effects         | 120 |

| 5.3 Memory/Network Bandwidth                                        | 124 |

| 5.3.1 Architectural Model                                           | 125 |

| 5.3.2 Traffic versus Cache Size                                     | 131 |

| 5.3.3 Traffic versus Line Size                                      | 141 |

| 5.3.4 Traffic versus the Number of Processors                       | 143 |

| 5.3.5 Summary                                                       | 146 |

| 5.4 Memory/Network Latency                                          | 147 |

| 5.4.1 Latency/Bandwidth Assumption                                  | 148 |

| Bibliograpl | hy                                              | 159   |

|-------------|-------------------------------------------------|-------|

| 6.11        | Future Work                                     | . 158 |

| Chapter 6   | Conclusions                                     | 155   |

| 5.5 (       | Chapter Summary                                 | . 153 |

|             | 5.4.3 Execution Time for the Long Latency Model | . 151 |

|             | 5.4.2 Execution Time for the Base Latency Model | . 149 |

## **List of Tables**

| 2-1 | Three Trade-offs between the Number of Deliver Messages and the Number of Eliminated Misses                                |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 3-1 | Benchmark Applications                                                                                                     |

| 4-1 | Deliver-run Types                                                                                                          |

| 4-2 | Deliver Messages Statistics                                                                                                |

| 4-3 | The Number of Delivered Messages per Used Message                                                                          |

| 5-1 | Traffic Table for read, write, upgrade, replace, and deliver operations 128                                                |

| 5-2 | Bandwidth of Four System Components in Processor Nodes                                                                     |

| 5-3 | Typical Read Latency without Contention. (The number of 200MHz processor clocks, Two network hops per remote-node access.) |

# **List of Figures**

| 1-1  | Optimizations for an Update Protocol                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------|

| 2-1  | An Example of Deliver and Prefetch Operations                                                                       |

| 2-2  | Deliver Annotation Techniques                                                                                       |

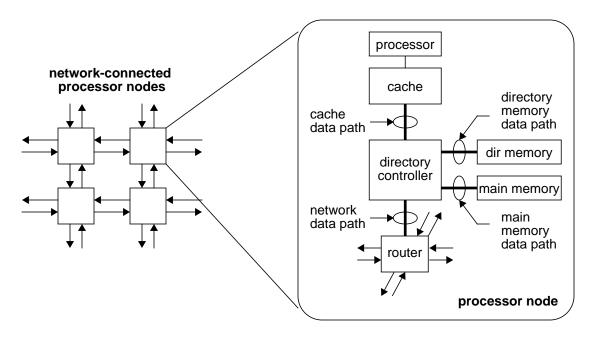

| 2-3  | NUMA Model                                                                                                          |

| 2-4  | Cache Directory Entry for Each Cache Line ( <i>n</i> processors)                                                    |

| 2-5  | An Example of Cache Directory Operations                                                                            |

| 2-6  | An Example of Sharing Patterns. Proc A is a producer and the rest of the processors are a consumer                  |

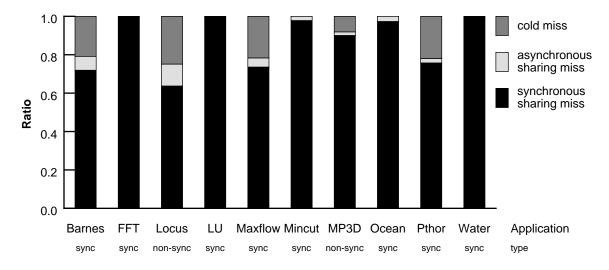

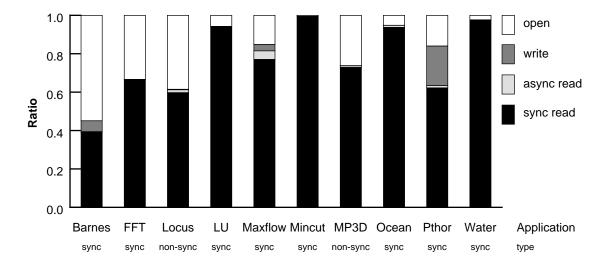

| 4-1  | Ratio of Read Miss Types. No deliver operations are used                                                            |

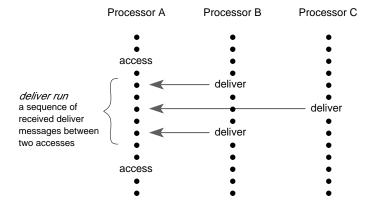

| 4-2  | Deliver-run                                                                                                         |

| 4-3  | Ratio of Deliver-run Types. Deliver-runs are classified by the consumer's operation that terminates the deliver-run |

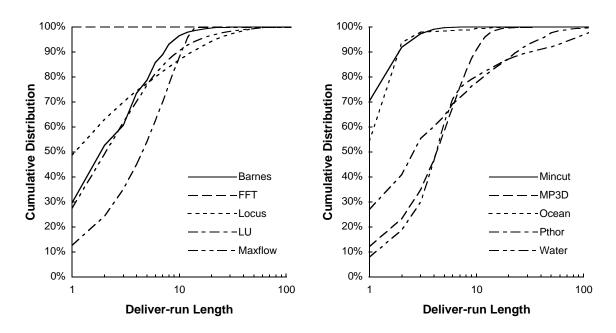

| 4-4  | Cumulative Distribution of Sync-read Deliver-runs                                                                   |

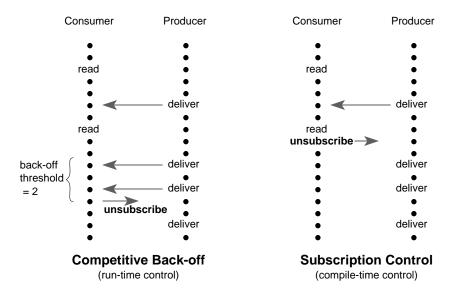

| 4-5  | Consumer Control of Deliver Operations                                                                              |

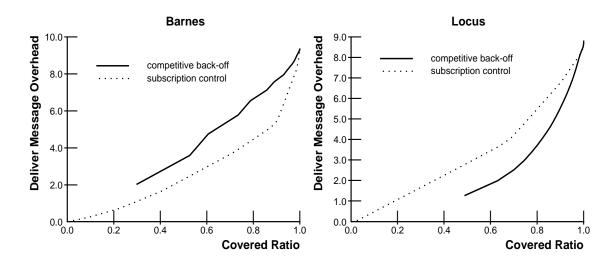

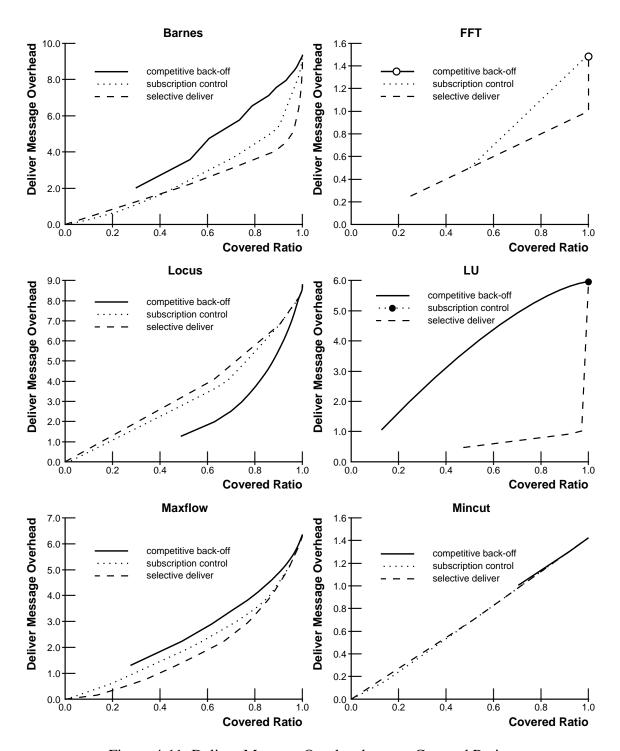

| 4-6  | Deliver Message Overhead versus Covered Ratio (Consumer-initiated Trade-offs)                                       |

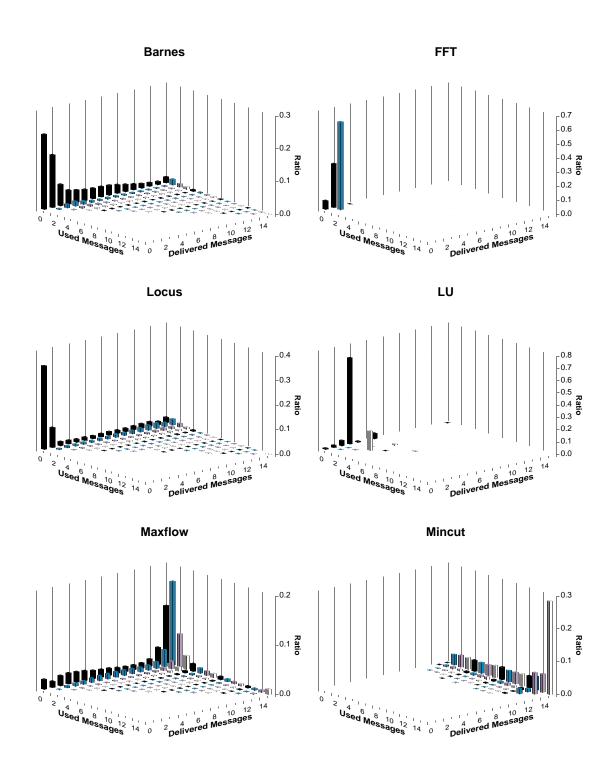

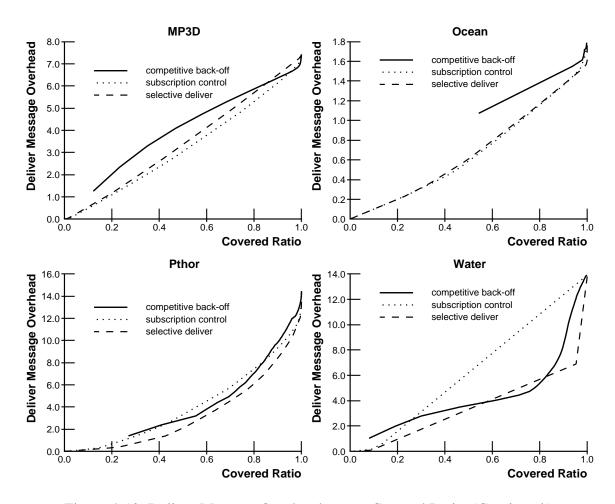

| 4-7  | Delivered Messages versus Used Messages                                                                             |

| 4-8  | Delivered Messages versus Used Messages. (Continued.)                                                               |

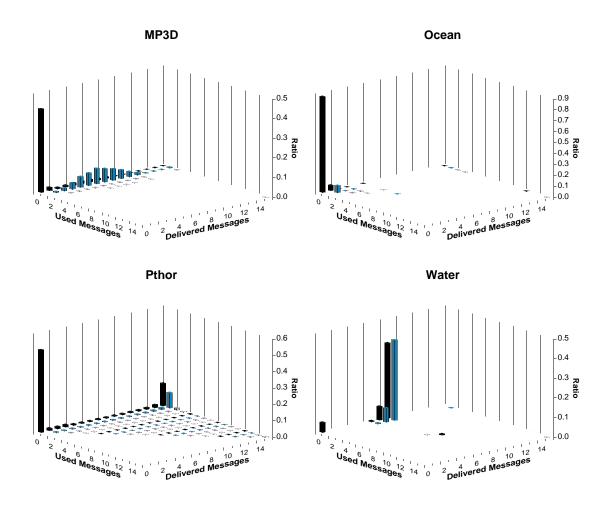

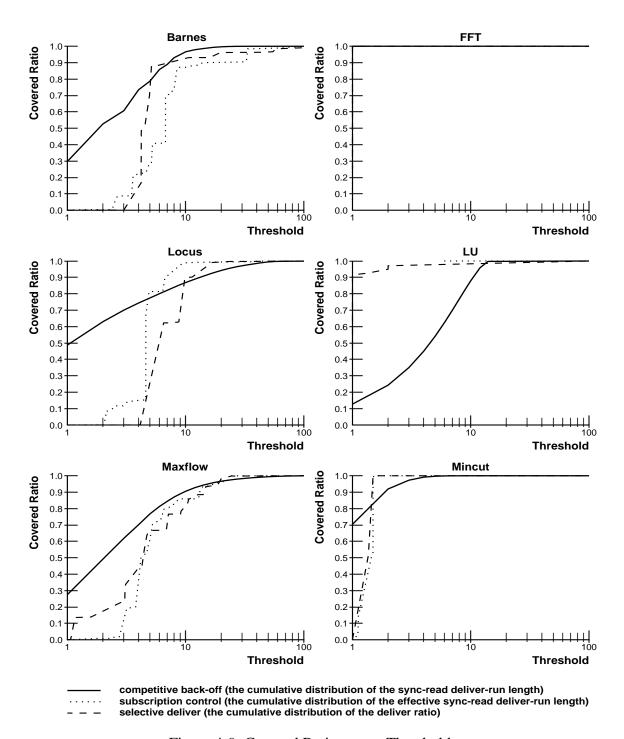

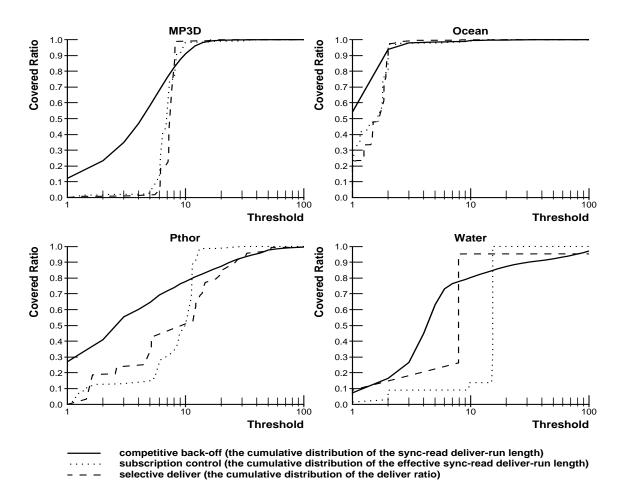

| 4-9  | Covered Ratio versus Threshold                                                                                      |

| 4-10 | Covered Ratio versus Threshold. (Continued.)                                                                        |

| 4-11 | Deliver Message Overhead versus Covered Ratio                                                                       |

| 4-12 | Deliver Message Overhead versus Covered Ratio. (Continued.) 61                                                      |

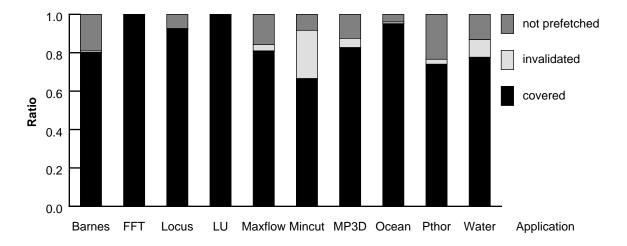

| 4-13 | Coverage of Prefetch Operations                                                                                     |

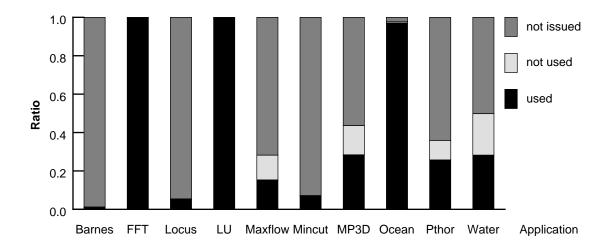

| 4-14 | Efficiency of Prefetch Operations                                                                                   |

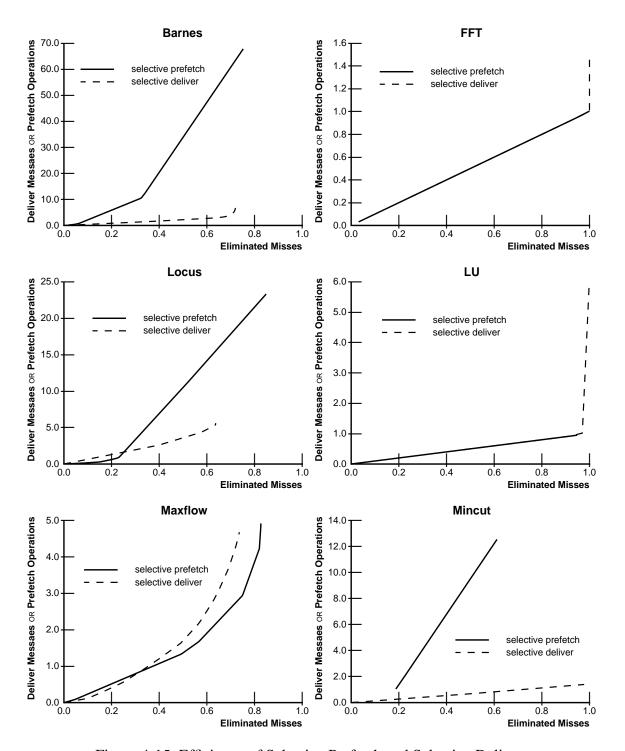

| 4-15 | Efficiency of Selective Prefetch and Selective Deliver                                                              |

| 4-16 | Efficiency of Selective Prefetch and Selective Deliver. (Continued.) 80                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

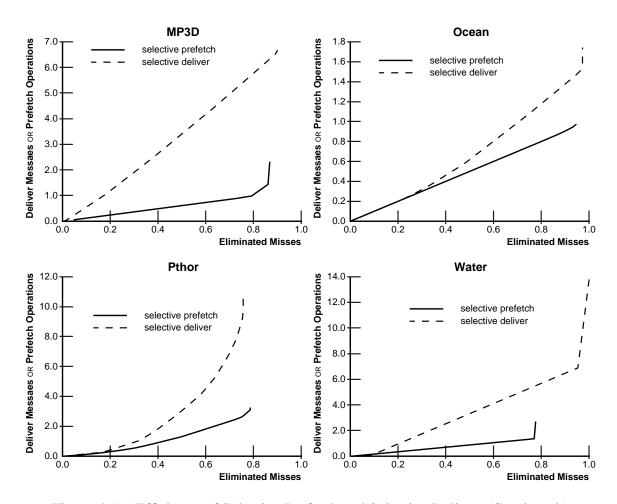

| 5-1  | Two Types of Cache Conflicts due to Prefetch and Deliver                                                                                                                                                                                                                                                                                                                                                                               |

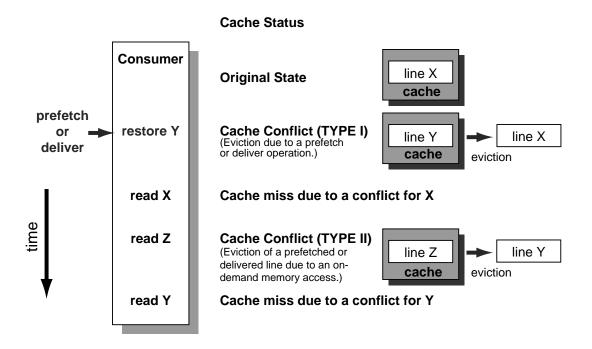

| 5-2  | Prefetch and Deliver Distances                                                                                                                                                                                                                                                                                                                                                                                                         |

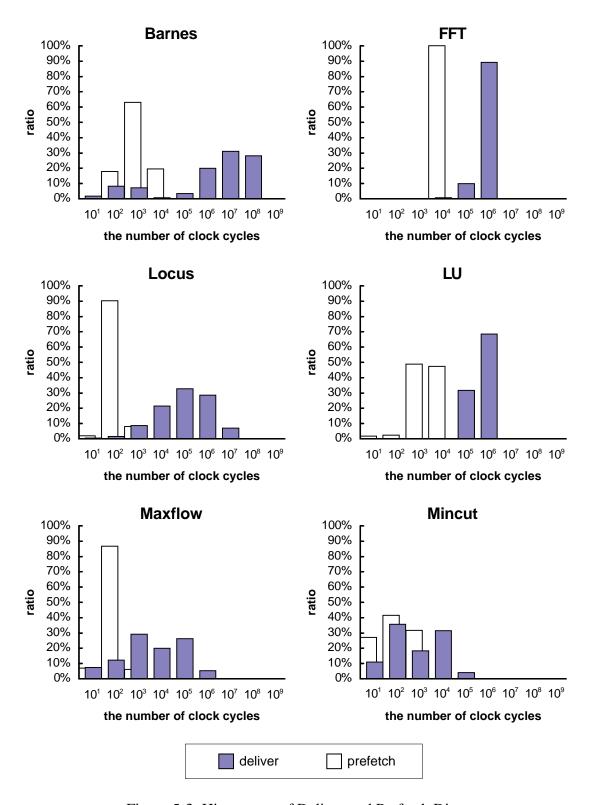

| 5-3  | Histograms of Deliver and Prefetch Distances                                                                                                                                                                                                                                                                                                                                                                                           |

| 5-4  | Histograms of Deliver and Prefetch Distances. (Continued.)                                                                                                                                                                                                                                                                                                                                                                             |

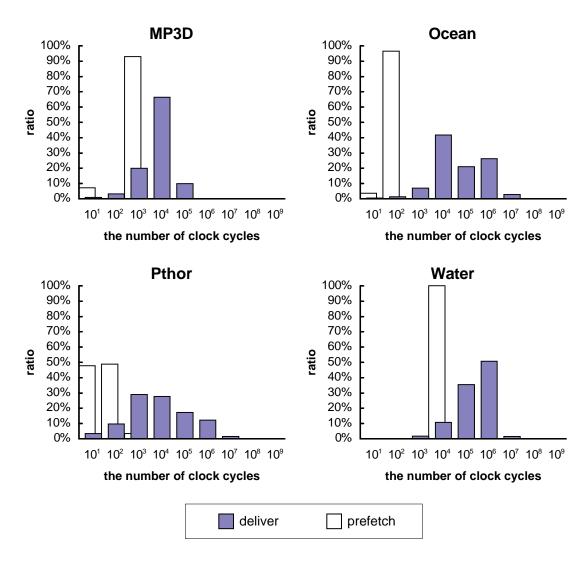

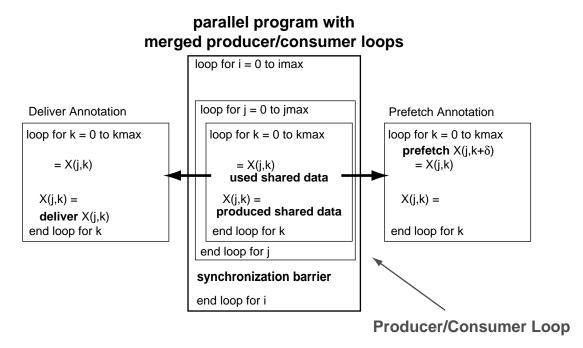

| 5-5  | Two Common Structures of Parallel Programs                                                                                                                                                                                                                                                                                                                                                                                             |

| 5-6  | A Classification of Cache Misses                                                                                                                                                                                                                                                                                                                                                                                                       |

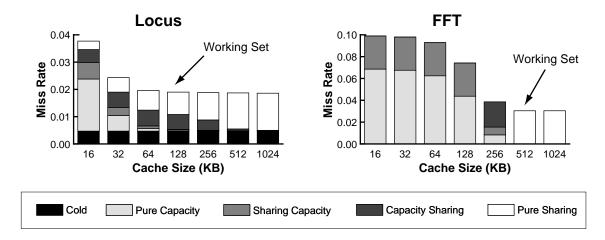

| 5-7  | Breakdown of Miss Rate versus Cache Size. No deliver or prefetch operations are used                                                                                                                                                                                                                                                                                                                                                   |

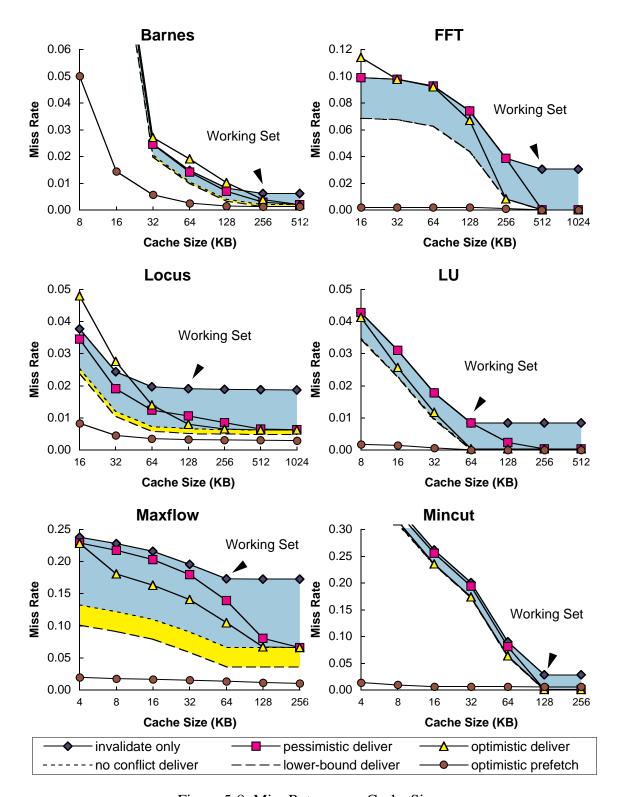

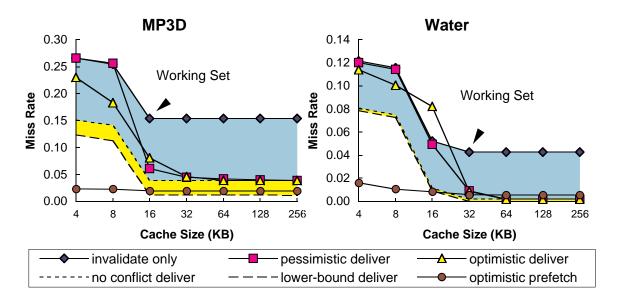

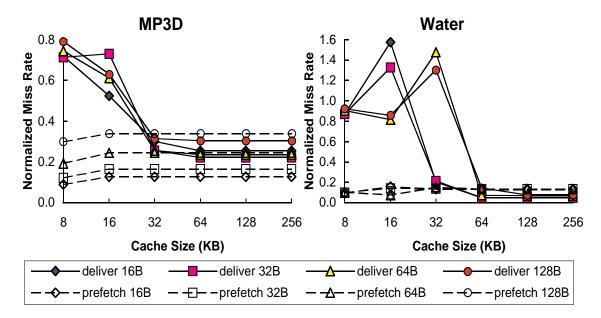

| 5-8  | Miss Rate versus Cache Size                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5-9  | Miss Rate versus Cache Size. (Continued.)                                                                                                                                                                                                                                                                                                                                                                                              |

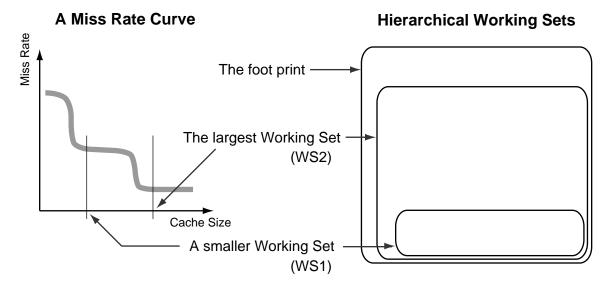

| 5-10 | Miss Rate Curve and Hierarchical Working Sets                                                                                                                                                                                                                                                                                                                                                                                          |

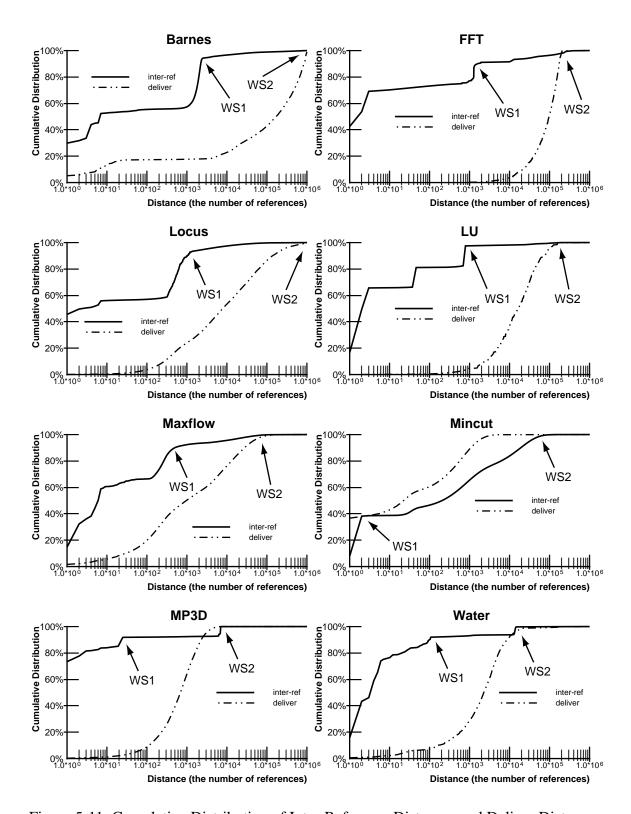

| 5-11 | Cumulative Distribution of Inter-Reference Distances and Deliver Distances. 111                                                                                                                                                                                                                                                                                                                                                        |

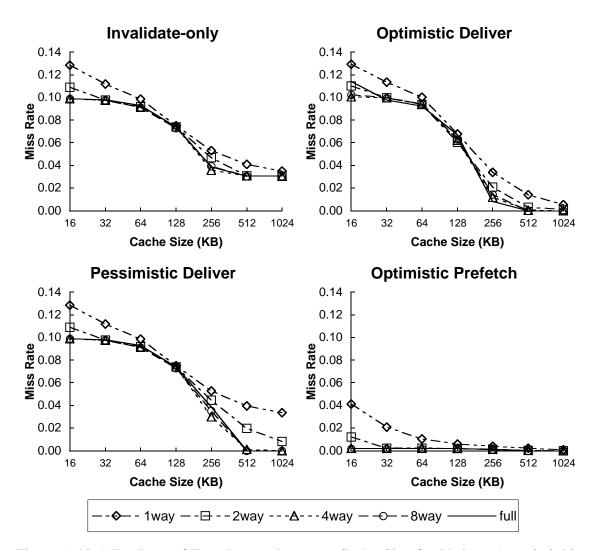

| 5-12 | Miss Rate of Four Protocols versus Cache Size for Various Associativities. The application is FFT                                                                                                                                                                                                                                                                                                                                      |

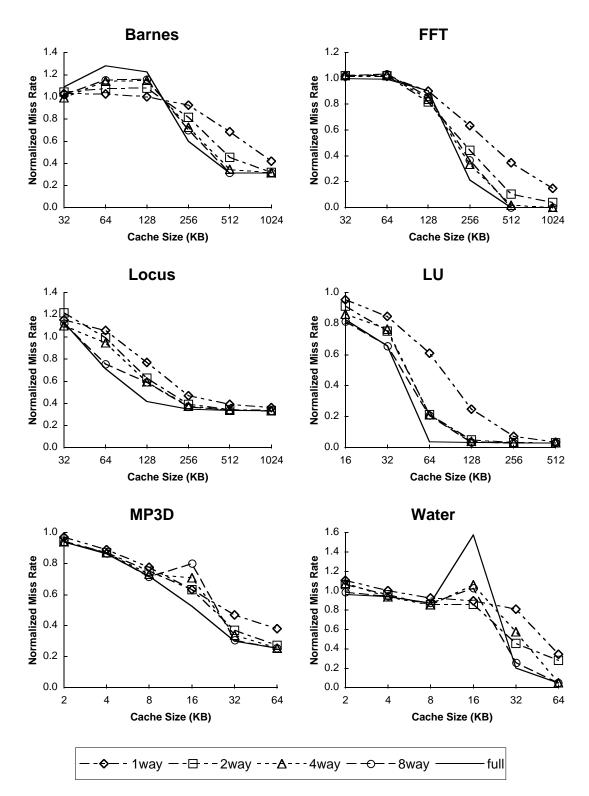

| 5-13 | Miss Rate of Optimistic Deliver versus Cache Size for Various Associativities. The miss rate is normalized by that of the invalidate-only protocol                                                                                                                                                                                                                                                                                     |

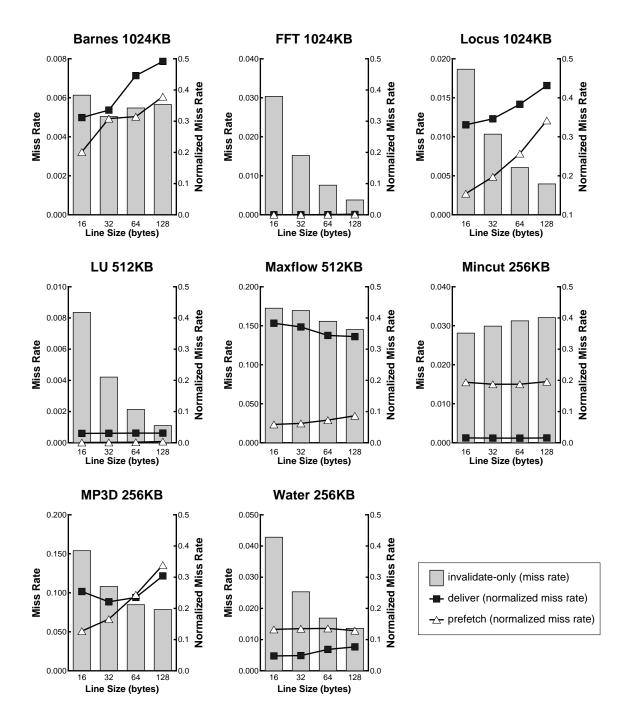

| 5-14 | Miss Rate versus Line Size for a Large Cache. The bar graph shows the miss rate of the invalidate-only protocol. The line graph shows the normalized miss-rate (the miss rate divided by that of the invalidate-only protocol) for the deliver and prefetch protocols. The optimistic replacement policy is used for both protocols. The cache size is shown at the top of each graph and is large enough to eliminate capacity misses |

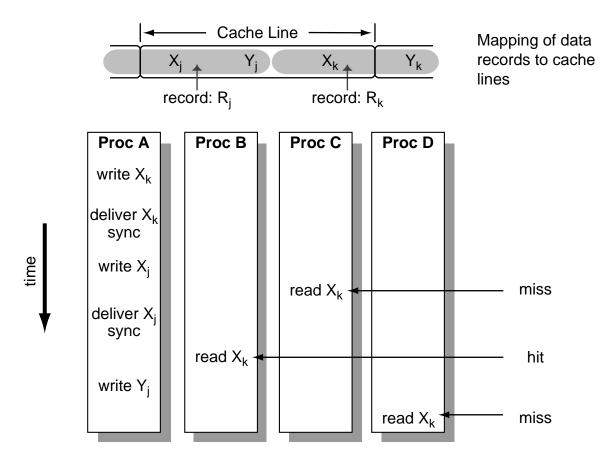

| 5-15 | False Sharing with Deliver Operations. Proc B does not cause a miss because the deliver operation for $X_j$ also sends $X_k$ to Proc B. Proc C causes a miss because Proc A invalidates the delivered $X_k$ . Proc A does not deliver $Y_j$ because of a single-processor reuse of $Y_j$ , so that Proc D causes a miss when Proc D reads $X_k$ . 118                                                                                  |

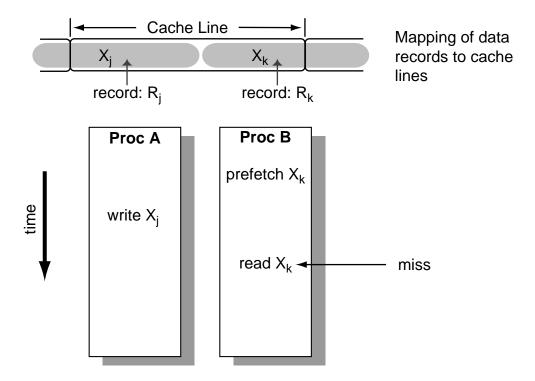

| 5-16 | False Sharing with Prefetch Operations. Proc B causes a cache miss because Proc A invalidates the prefetched $X_k$                                                                                                                                                                                                                                                                                                                     |

| 5-17 | Miss Rate of Optimistic Deliver and Optimistic Prefetch for Cache and Line Size Variations. The miss rate is normalized by that of the invalidate-only protocol with the same cache size and the same line size                                                                                                                                                                                                                        |

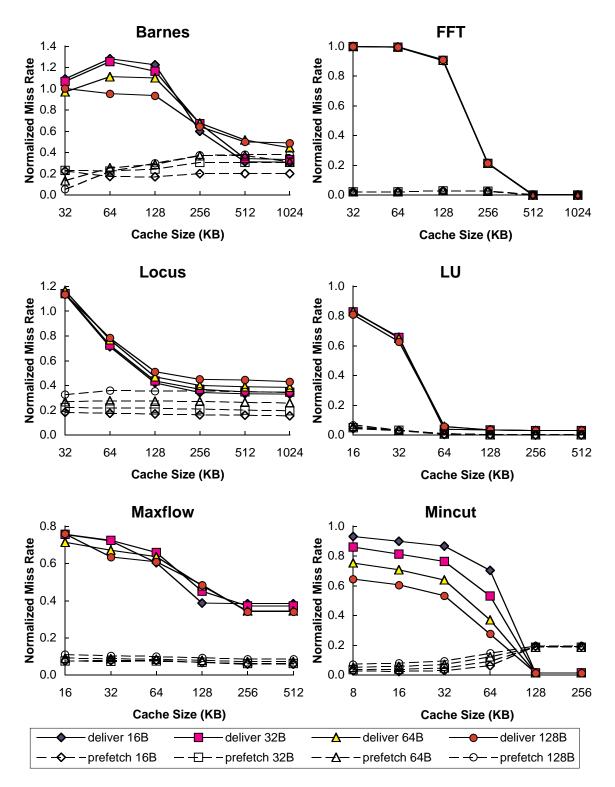

| 5-18 | Variations. (Continued.) The miss rate is normalized by that of the invalidate-only protocol with the same cache size and the same line size                                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-19 | Processor Node Model                                                                                                                                                                                                                                                                                                                                                   |

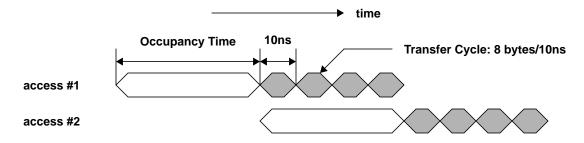

| 5-20 | Data Transfer Model for Cache and Main Memory                                                                                                                                                                                                                                                                                                                          |

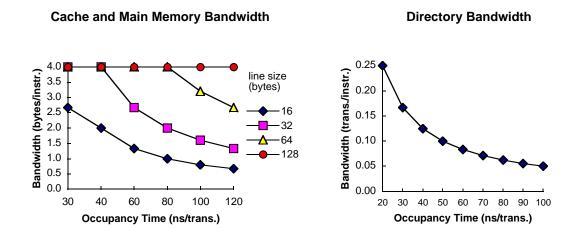

| 5-21 | Bandwidth versus Occupancy Time. Processor = 200 M instructions/sec 130                                                                                                                                                                                                                                                                                                |

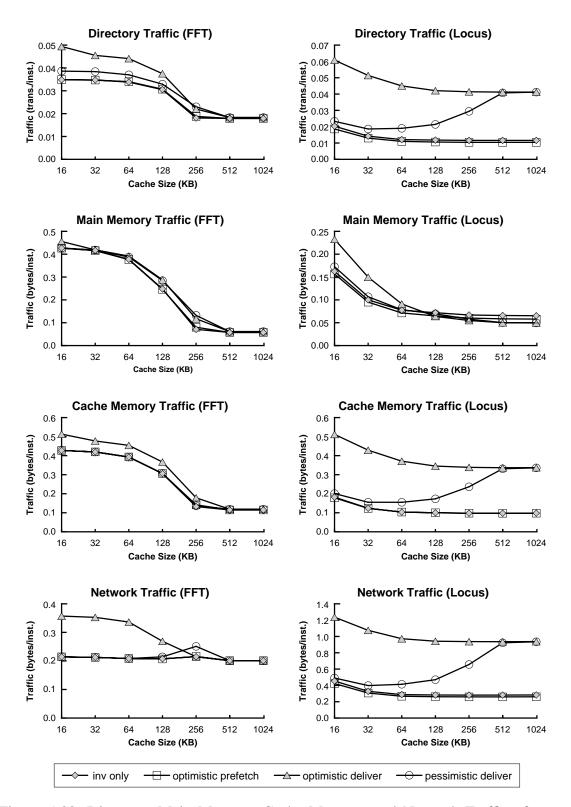

| 5-22 | Directory, Main Memory, Cache Memory, and Network Traffic of versus Cache Size for FFT and Locus                                                                                                                                                                                                                                                                       |

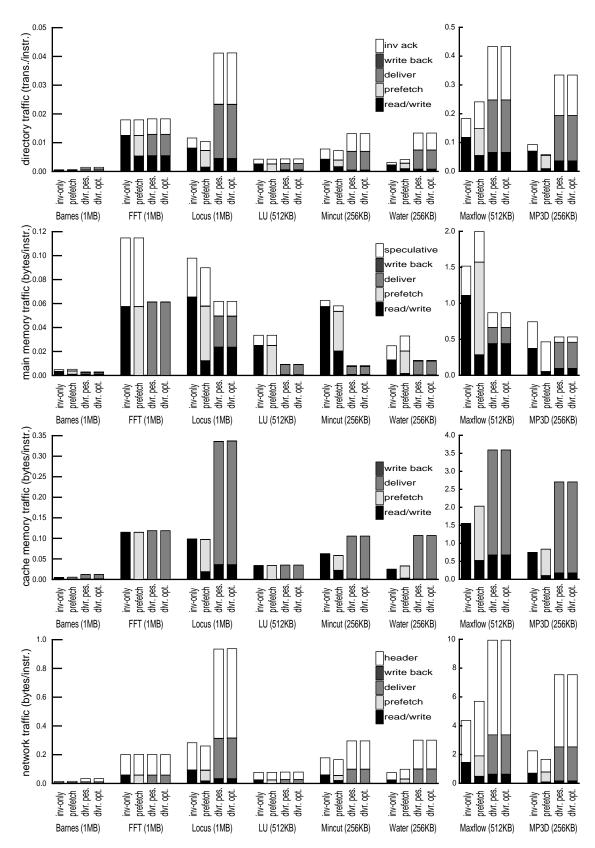

| 5-23 | Breakdown of Directory, Main Memory, Cache Memory, and Network Traffic for a Large Cache                                                                                                                                                                                                                                                                               |

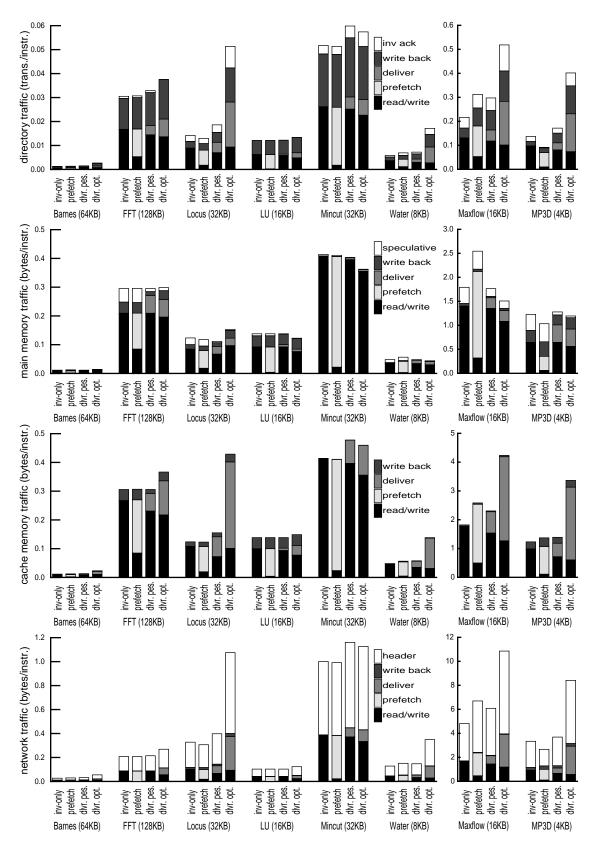

| 5-24 | Breakdown of Directory, Main Memory, Cache Memory, and Network Traffic for a Small Cache                                                                                                                                                                                                                                                                               |

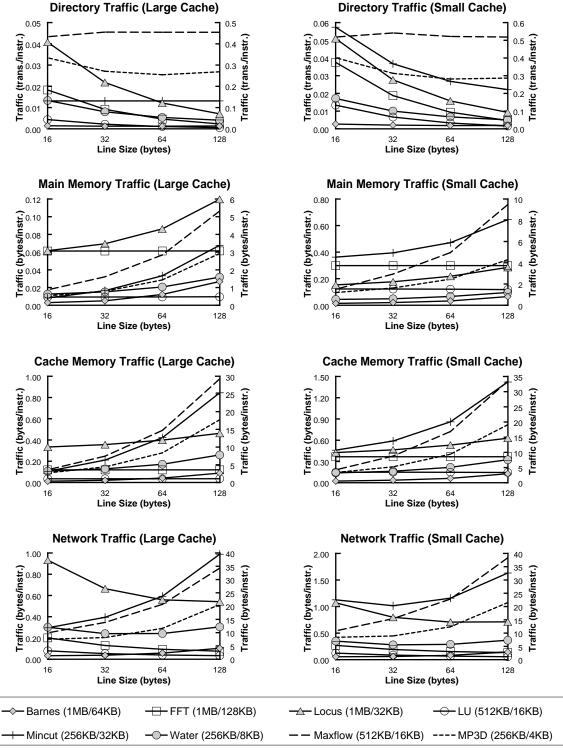

| 5-25 | Directory, Main Memory, Cache Memory, and Network Traffic versus Line Size for Optimistic Deliver. The right Y axis is for Maxflow and MP3D (dotted lines), and the left Y axis is for the rest of the applications (solid lines). The graph legend shows two cache sizes for each application: a large size for the left graphs and a small size for the right graphs |

| 5-26 | Breakdown of Directory, Main Memory, Cache Memory, and Network Traffic versus the Number of Processors for a Large Cache                                                                                                                                                                                                                                               |

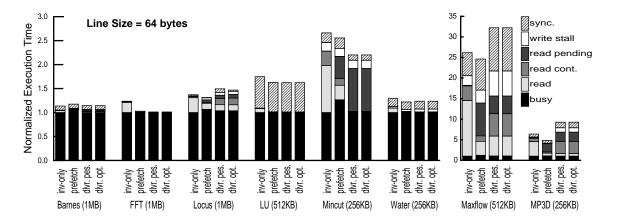

| 5-27 | Execution Time of Four Protocols for Base Latency. The execution time is normalized by the busy time of the invalidate-only protocol                                                                                                                                                                                                                                   |

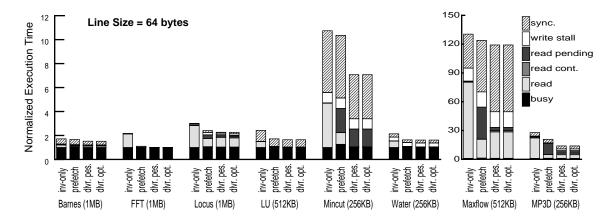

| 5-28 | Execution Time of Four Protocols for Large Latency. The execution time is normalized by the busy time of the invalidate-only protocol                                                                                                                                                                                                                                  |

## **Chapter 1**

### Introduction

Reducing the impact of memory latency is a key issue for shared-memory multiprocessor systems. In shared-memory multiprocessors, inter-processor communication implicitly occurs by memory accesses. Since memory modules are typically distributed among processor nodes in large-scale systems, processors need to access remote memory to communicate with other processors. Thus, communication can stall processors for long-latency memory accesses and offset the performance gain due to parallel processing. As the number of processors increases, moreover, the communication latency generally increases.

Several techniques to reduce the impact of memory latency have been proposed and evaluated. We can categorize those techniques in two types: latency reducing and latency hiding. Latency reducing techniques include coherent caches and page allocation techniques, which reduce the memory latency by storing data at a location closer to the processor that accesses the data. Latency hiding techniques, on the other hand, include multi-threading, prefetching, and relaxing the consistency model, which let the processor perform useful tasks during long-latency memory accesses. Prefetching by the consumer with coherency caches has been shown to be one of the most useful techniques [12, 27, 29]. This thesis examines consumer-based and producer-based prefetching strategies. The producer-based approach, which we call *deliver* in this thesis, could maximally hide memory latencies because the producer sends the shared datum to prospective consumers at the earliest possible time after the datum is produced. The consumer-based approach, which we simply call *prefetch* in this thesis, on the other hand, might not hide memory latencies as effectively because the consumer may fetch the datum before it is produced, or may not fetch it early enough to hide the latency completely. Qualitative arguments can be made for both

capabilities, and the DASH multiprocessor [39] and the KSR1 system [23] actually support both features.<sup>1</sup>

We quantitatively evaluate these two alternatives using a software-controlled mechanism for both; the programmer or a language system explicitly inserts data transfer operations (prefetch or deliver) in the program. The consumer-based prefetch needs to perform prefetch operations early enough so that the prefetched datum comes to the processor by the time the processor needs the datum. Mowry and Gupta [44] have shown that the consumer-based prefetch is not very effective for applications using pointers extensively because addresses to prefetch are often not available early enough. The producer-based deliver, on the other hand, needs to perform a deliver operation when processors write a shared datum for the last time before other processors read the datum. Thus, the last write to a shared datum before a synchronization operation is a good candidate to insert the deliver operation. It is relatively easy to find such places. Even if the program uses pointers, the address for deliver operations is available where these operations should be inserted. Our implementation of a deliver uses a hardware mechanism in a cache directory that keeps track of potential consumers based on past sharing patterns. The deliver operation sends a specified cache line to those potential consumers.

We have chosen to simulate a directory-based cache-coherent NUMA machine as the base in which we evaluate these two schemes. Our simulation results indeed show that the qualitative advantage of the deliver can yield a slight performance advantage when the cache size and the memory latency are very large. For realistic architectural parameters, however, the prefetch scheme generally outperforms the deliver scheme for two reasons. First, the deliver scheme often sends cache lines to consumers so early that the consumers replace the delivered cache lines before they are used. Second, the prefetch scheme can use the local cache as a filter to eliminate most of the unnecessary cache transfers, while the deliver scheme does not have such an effective filtering mechanism. Examining the behavior of these schemes leads us to new insights into communication behavior in parallel applications.

<sup>1.</sup> The producer-based approach is called *poststore* in KSR1.

This chapter is organized as follows. In Section 1.1, we discuss other research work that are related this thesis. In Section 1.2, we define the research goal. In Section 1.3, we summarize the main contributions. In Section 1.4, we discuss the organization of the thesis.

#### 1.1 Related Work

We can view the deliver and prefetch schemes as a technique for optimizing cache-coherency protocols or as a technique for combining message-passing and shared-memory paradigms. This section discusses related work from these two perspectives.

#### 1.1.1 Optimizing Cache Protocols

There are two traditional protocols for cache coherency: the invalidate protocol (e.g., Illinois Protocol [48] and Berkeley Ownership Protocol [37]) and the update protocol (e.g., Firefly Protocol [56] and Dragon Protocol [4]). In the invalidate protocol, once a processor obtains the ownership of a cache line, the processor can write to the entire cache line without generating network traffic. Communication between processors occurs through cache misses; when another processor reads any word in the line, a cache miss occurs, and the reading processor stalls until the line is received. In the update protocol, on the other hand, the writing processor updates all the copies on every write to any words in the cache line. Thus, when another processor reads any word in the line, no cache miss occurs. Moreover, no false sharing misses [19] occur in the update protocol. A major drawback of the update protocol is that it often generates much more write traffic than the invalidate protocol. This write traffic can increase the number of processor stalls for write operations because of write-buffer overflows, as well as increasing the latency for read-miss operations because of network congestion. Large-scale machines typically use an invalidate protocol because of the traffic overhead due to the update protocol.

Other researchers have proposed to optimize the update protocol for reducing the write traffic and to combine the two protocols for obtaining the benefit of the two. The deliver scheme can be viewed as an optimized update protocol or as a combination of the two protocols. In this subsection, we first discuss optimization techniques for update protocols. Second, we discuss hybrid protocols that use a back-off technique. Third, we discuss other

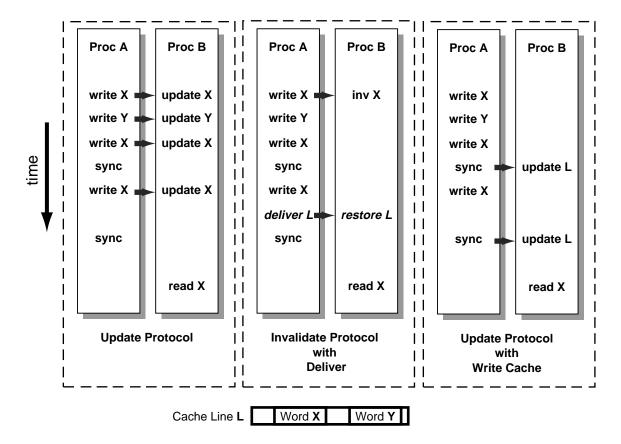

Figure 1-1: Optimizations for an Update Protocol.

techniques for optimizing cache protocols. Fourth, we discuss software-controlled primitives that allow us to exploit software knowledge for cache-coherency protocols.

#### 1.1.1.1 Coalesced Update Protocols

The deliver operation is similar to the update operation in a sense that both operations push a produced value into a consumer's cache based on past sharing patterns. The deliver operation, however, sends a whole cache line to processors that were sharing the line, while the update operation sends a word to processors that are sharing the line. Thus, the deliver operation can be more effective than the update operation because the deliver operation aggregates several updates for the same cache line in a single message. Figure 1-1 illustrates interactions between caches for three cache protocols using the same sharing pattern. Let's focus on the left-most (an update protocol) and the center (an invalidate protocol with deliver operations). A producer (Proc A) and a consumer (Proc B) share the same cache line L, which contains Word X and Word Y. In the update protocol, every

write updates the shared copy in the consumer's cache even if the consumer does not use the updated value. In the deliver scheme, on other hand, every write does not update the shared copy; a deliver operation is inserted after the last write before the consumer uses the produced value. The deliver operation aggregates produced values for the same cache line and sends them to the consumer in a single message. Thus, the deliver scheme has two advantages over the update protocols. First, the deliver scheme sends several updates in a single message rather than individually. Thus, the deliver scheme can use the bandwidth of the interconnection network more effectively than the update protocol, since each send operation has an associated fixed overhead (e.g., message header). Second, when the producer writes the same word multiple times before the consumer accesses it, the deliver scheme sends a single updated value rather than multiple copies. Thus, the deliver scheme generally causes less data traffic than the update protocol.

Several schemes have been proposed to aggregate update operations for update protocols. Glasco et al. [24] have proposed a coalescing write buffer that is placed between the processor and its first-level cache and combines write requests for the same cache line into a single write request. The combining is limited to a sequence of write requests for the same cache line that are not interleaved by writes for another cache line. Thus, this scheme exploits only limited locality.

Dahlgren and Stenström [16] have studied write caches for several cache protocols. The write cache is placed after the second-level cache in each processor node and stores write requests that are not satisfied in the second-level cache (e.g., write and write-upgrade misses). The write cache evicts its cache line when the write cache needs to make a room to store another cache line or when the processor issues a release request. The right most chart in Figure 1-1 illustrates the effect of the write cache for an update protocol. Since write requests do not usually propagate to other processors until a release operation, the program has to be synchronized for the correctness of the computation. Dubois et al. [20] have studied a similar mechanism, an Invalidation Send Buffer, which delays sending write requests for an invalidate protocol so that the number of false sharing misses is reduced. The write cache exploits more locality than the coalescing write buffer that

<sup>2.</sup> Section 2.1 defines more details about the deliver operation.

Glasco proposed [24] because the write cache can combine all write requests between release operations provided the write cache size is sufficient.

The deliver scheme differs from an update protocol with the write cache in three ways. First, the deliver scheme is software-controlled so that we can use deliver operations selectively for those data structures or computations for which the deliver operation works efficiently. For example, as shown in Figure 1-1, the deliver scheme can insert a deliver operation only when consumers use produced values with high probability, while the write cache sends produced values at every release operation. Second, application programs do not have to be synchronized for the deliver scheme, while they must be for the write cache. This is because, in the deliver scheme, processors obtain the ownership before writing a cache line so that write operations for the same address are serialized at the home directory. Third, the deliver scheme may generate more false sharing misses than an update protocol with a write cache. This is because a write cache allows multiple processors to update the same cache line at the same time without obtaining ownership. However, as we will discuss in Section 5.2, false sharing does not significantly impact the miss rate of the deliver scheme for line sizes up to 128 bytes for most of our benchmark applications.

Hagersten [31] has proposed a update cache (Ucache), which collects update requests at the receiver's side. The Ucache is placed between the network interface and the local bus to prevent update requests from congesting the local bus in the receiver of update requests. The Ucache, however, does not reduce the network congestion due to update requests.

#### 1.1.1.2 Hybrid Protocols with a Back-off Technique

Another class of techniques for optimizing cache protocols is a hybrid protocol that combines an invalidate and an update protocol. Competitive snooping [22, 36] is a hybrid cache protocol for bus-based multiprocessors that alternates between the two protocols by using a competitive algorithm. Competitive snooping starts with using an update protocol. The cache has a counter for each cache line that tracks the number of updates that the cache has received. The cache invalidates a cache line when the cache receives a certain number of updates for the cache line without any intervening accesses by the local processor. When all shared copies for the cache line are invalidated, the producer processor

obtains an exclusive copy of the cache line so that the processor can write the cache line without producing bus traffic. Eggers and Katz [22] have shown that the competitive snooping outperforms the update protocol for applications with so-called sequential sharing (i.e., applications that generate relatively long write runs). This is because, in such cases, the update protocol suffers from a large number of update transactions, which competitive snooping can reduce. Grahn at al. [28] have studied the implementation and the performance of a similar protocol — competitive update — for a directory-base cache-coherent NUMA machine.

Archibald [3] has also proposed a similar adaptive protocol. In his protocol, when a single processor writes a cache line three times without any intervening references by any other processor, the adaptive protocol invalidates all cached copies other than the producer's copy. Dahlgren [15] has shown that Archibald's protocol produces less traffic and fewer misses than the competitive snooping for a bus-based multiprocessor. Archibald's adaptive protocol updates all shared copies of the cache line if any of the sharing processors are actively using the cache line. Competitive snooping, on the other hand, updates a shared copy of the cache line only if the sharing processor that has a copy is actively using the cache line. Thus, Archibald's protocol generally keeps shared copies valid for a longer period than the competitive snooping. Since a single bus transaction can update any number of shared copies in a bus-based multiprocessor, Archibald's protocol generates less traffic and fewer cache misses than competitive snooping for the same competitive threshold.

A write cache can also exploit locality to reduce the traffic in hybrid protocols. Dahlgren has evaluated Archibald's protocol for a snoop-cache multiprocessor in [15] and a competitive-update protocol for a directory-cache multiprocessor in [16] with accompanying write caches.

Hagersten et al. [32] proposed a hybrid protocol for a COMA (Cache-Only Memory Architecture) machine. The hybrid protocol uses an invalidate protocol by default and switches to an update protocol when a processor causes a coherency miss (i.e., the proces-

<sup>3.</sup> Eggers and Katz [22] defined the write run as a sequence of write operations that the same processor generates without any intervening accesses from other processors.

sor's cache has an invalidated copy of the cache line). The hybrid protocol uses a back-off technique similar to the competitive snooping; each cache has a update counter to keep track of the number of received updates for each cache line and invalidates a cache line when the cache receives a certain number of updates for the cache line without any intervening accesses by the local processor. Competitive snooping resets the update counter only for local processor's accesses. The hybrid protocol, on the other hand, resets the update counter not only for local processor's accesses but also for data migrations (i.e., changes of the producer processor). Therefore, the hybrid protocol tends to eliminate cache misses without eliminating unused update requests for migratory sharing while the protocol tends to eliminate unused update operations without eliminating cache misses for sequential sharing (sharing patterns with relatively long write runs).

Nilsson [47] has studied a hybrid protocol for a NUMA machine. The hybrid protocol combines a competitive-update protocol and a migratory optimization that was studied for an invalidate protocol by Cox and Fowler [13] and Stenström et al. [55]. The migratory optimization is a technique to reduce the write latency and the network traffic by translating a read request to a read-exclusive request when a read cache-miss occurs for migratory objects. This hybrid protocol is similar to the COMA protocol since both protocols include a mechanism that handles migratory sharing. The major difference between the two is that the Nilsson's protocol focuses on reducing the traffic for migratory objects while the COMA protocol focuses on reducing the miss rate for migratory objects.

The hybrid protocols that we have discussed use a back-off technique that basically switches from an update mode to an invalidate mode when the update mode causes more traffic overhead than a certain threshold. The back-off technique provides a trade-off between the number of cache misses and the amount of the traffic. Hybrid protocols reduce the number of misses while generating extra traffic when in the update mode, or reduce the amount of the traffic while generating cache misses when in the invalidate mode. As we will discuss in Section 4.1, we can add a back-off technique to the deliver scheme (called *competitive deliver*) for a similar trade-off. In the competitive deliver scheme, each cache counts the number of received deliver messages for every cache line. When a cache receives a certain number of deliver messages for a cache without any inter-

vening accesses to that line by the local processor, the cache cancels the subscription of the deliver message for that cache line.

#### 1.1.1.3 Other Protocol Optimizations

Read snarfing (also called read broadcast) has been evaluated by Eggers and Katz [22], Anderson and Baer [2], and Dahlgren [15] for bus-based multiprocessors. This technique assumes an invalidate protocol with a snoop mechanism. If a cache finds a cache line transfer for which the cache has an invalidated copy, the cache reads the cache line from the bus and changes the invalidated copy to a valid one. Thus, when the local processor of the cache reads the cache line, a read hit occurs. This technique reduces the number of misses without generating extra traffic. The transfer unit of produced values is a cache line, instead of a word. Thus, this technique exploits more locality than update protocols without a write cache. If the cache directory keeps track of processors that have an invalidated copy for each cache line, a directory-based cache system can use this technique. This read snarfing, however, is effective only if a relatively large number of processors read a produced value. As we will discuss in Section 4.1, the number of processors that read a produced value is relatively small for most of our benchmark applications. Thus, the read snarfing should be less effective than the deliver scheme for most of our applications.

Veenstra and Fowler [57] studied three hybrid protocols of another class. The first one statically assigns an invalidation protocol or an update protocol to each page. The second one statically assigns either protocol to each cache line. The third one dynamically chooses either protocol for each write. While competitive hybrid protocols use a simple on-line algorithm to select the protocol, Veenstra and Fowler [57] used off-line algorithms and found that the per-line static assignment of the protocol can obtain most of the benefit due to the dynamic assignment of the protocol. These off-line algorithms rely on a cost model for selecting the protocol mode. The cost model defines the cost of each cache operation (i.e., cache hit, invalidate, update, and cache block load), which is the summation of a weighted latency cost and a weighted traffic cost of the operation. The cost of a hybrid protocol is defined as the total cost of all operations that an application program generates. This cost model, however, does not necessarily represent the performance of

the protocol since the performance depends on the trade-off between the number of misses and the amount of the traffic. In this thesis, therefore, for comparing the deliver and the prefetch schemes, we examine a trade-off curve between the number of misses and the amount of the traffic for each scheme so that we can obtain intuition about the performance effect of the two schemes.

Raynaud et al. [49] have proposed an adaptive update protocol, Distance-Adaptive Update Protocol. This work defines an *update distance* as the number of updates that a processor receives between accesses in an update protocol with a write cache. The distance-adaptive update protocol relies on the fact that there is a correlation between two consecutive instances of the update distance and that the correlation is consistent for all processors and for all data structures of the application. If the update distance changes non-deterministically or if the pattern in the update distance is dramatically different among data structures, this adaptive protocol would perform poorly. The deliver scheme should be able to predict access patterns as accurately as this adaptive protocol does for applications with a deterministic sharing pattern since the deliver scheme exploits software knowledge about the sharing pattern. A quantitative comparison between this adaptive protocol and the deliver scheme, however, requires further experiments and is beyond the scope of this thesis.

#### 1.1.1.4 Software-Controlled Primitives

Hill et al. [35] proposed a programming model, Check-In / Check-Out (CICO), in conjunction with simple hardware,  $Dir_ISW$ . In the base CICO model, a check-out annotation is inserted at the expected first use of shared data and a check-in annotation is inserted at the expected last use of shared data, so that simple  $Dir_ISW$  hardware can efficiently support the program. Similar to the deliver annotation, the CICO annotation tries to exploit the knowledge of the expected data-access pattern. Check-in annotations are quite similar to deliver annotations in that they are both placed after the last write to shared data. The check-in operation, however, sends the produced data only to the home node, not to consumer's caches. This is because the major focus of the CICO model is simplifying the hardware while the major focus of the deliver scheme is improving performance.

The KSR1 system supports latency hiding mechanisms including prefetch and poststore [23]. The prefetch and poststore are software-controlled and similar to our prefetch and deliver respectively. The KSR1 is a COMA machine, while our study uses a NUMA machine. In the COMA architecture, each node has a very large (32 Mbyte [23]) memory cache which corresponds to the local memory in the NUMA machine. The prefetch and poststore of the KSR1 move the datum only to the memory cache, not to the processor cache. Therefore, the prefetch and poststore cannot hide memory latencies completely, while our prefetch and deliver can. The poststore, however, should not suffer from the cache interference we observed, since the memory cache is very large. The poststore, moreover, can take advantage of the hierarchical ring network in the KSR1 that supports broadcasting, while our deliver scheme only assumes a point-to-point communication mechanism. The KSR1 also supports read snarfing (called *automatic update*), which is a technique that updates invalidated copies in the memory cache by snooping the ring network.

Previous studies have discussed the latency hiding mechanisms of KSR1. Rosti et al. [51] studied the poststore, using synthetic benchmarks and analytical models. Our study uses a set of real parallel applications that provides a more realistic evaluation environment than synthetic benchmarks. Windheiser et al. [58] evaluated the effectiveness of prefetch and poststore for a sparse solver application on KSR1. Our study discusses more detailed statistics than those two studies, such as the cache-size sensitivity, the efficiency of prefetch/deliver schemes, and the intrinsic/contention latency of read operations.

#### 1.1.2 Combining Shared-Memory and Message-Passing Paradigms

Traditionally two distinct paradigms exist for the architecture of multiprocessors: shared memory and message passing. The program does not have to manage communication explicitly in the shared memory, while the program has to do so in the message passing. Thus, the shared memory is considered to be more programmable than the message passing especially for programs with irregular communication patterns. Explicit communication mechanisms in the message passing, however, allow us to optimize the communication so that the communication and the computation are overlapped.

Software-controlled deliver and prefetch operations provide us an ability of explicit communication on the shared memory. Thus we can consider the deliver and the prefetch schemes as a way to combine the shared memory and the message passing so that we can obtain the benefit of the two paradigms.

Other researchers have proposed to integrate block data transfer in shared-memory multiprocessors [1, 14, 33, 61]. Block data transfer can be implemented as a memory copy primitive (memory-to-memory transfer) on cache-coherent shared-memory systems. Byrd [8] has discussed a block transfer scheme (called StreamLine) for cache-to-cache transfers. Block data transfer is similar to deliver since both schemes provide a sender-initiated explicit data-transfer mechanism in a shared-memory system. Both schemes can transfer data in a pipelined fashion and overlap the communication and the computation. The two schemes, however, are different in four points. First, deliver operations do not affect the correctness of the program, while block data transfers usually affect the correctness of the program. This is because deliver operations do not change the value of any memory location while block data transfers change the value in the destination message buffer. Thus, block data transfers need to be inserted in the program so that not only the performance is improved but also the program works correctly. Second, the block data transfer needs message buffers that are explicitly managed by the programmer or the language system, while the deliver scheme does not. Third, block data transfer can be implemented as a transfer operation to the memory or the cache of the destination processor. The deliver scheme, on the other hand, can be implemented as a transfer operation only to the cache of the destination processor. Fourth, block data transfer requires the programmer or the language system to specify that the destination of the message explicitly, while our deliver scheme requires a hardware mechanism to keep track of potential consumers for each cache line.

#### **1.1.3 Summary**

We have discussed related work for the deliver and the prefetch schemes from two different perspectives: optimizing cache protocols and merging the shared-memory and the message-passing paradigms.

The optimization techniques of cache protocols can be divided into four groups. First, we discussed a set of techniques that delay sending update messages to exploit locality in updating patterns. Second, we discussed a set of techniques that combine the invalidate and the update protocols by using a back-off technique. Third, we discussed other protocol optimization techniques that include read snarfing and distance-adaptive update protocol. Fourth, we discussed software primitives that exploit software knowledge about sharing patterns for simplifying the hardware or for improving the performance. The deliver and the prefetch schemes can be categorized in the fourth group: software primitives to improve the performance.

We also qualitatively compared the deliver scheme with block data transfer, which combines the message-passing and the shared-memory paradigms. While both schemes provide explicit communication primitives on top of the shared memory paradigm, block data transfer is closer to the message passing paradigm than the deliver scheme. In block data transfer, the communication primitive may affect the correctness of the program and the programmer or the language system needs to mange message buffers explicitly. In the deliver scheme, on other hand, the communication primitive does not affect the correctness of the program and the programmer or the language system does not need to manage message buffers.

### 1.2 Research Goals

The goal of this thesis is to compare the characteristics of deliver and prefetch operations by analyzing the communication behavior of parallel applications. This goal is brokendown into two sub goals.

- Analyzing sharing patterns to identify ones that produce unnecessary deliver or prefetch messages.

- Understanding the interaction between application characteristics and architectural parameters to identify advantages and disadvantages of the deliver and the prefetch schemes.

For the first goal, we focus on the communication behavior. Through the analysis of sharing patterns, we examine several techniques that eliminate unnecessary messages. For the second goal, we explore a large design space of architectural parameters and compare the

characteristics of the deliver and the prefetch schemes. For both sub goals, we focus on underlying application characteristics.

We use explicitly-parallelized scientific applications that represent various algorithms for numerical computations and contain a variety of simple and complex memory-access patterns. Further research is necessary for other types of applications (e.g., compiler-parallelized applications and commercial applications), which may have different characteristics from our benchmark applications. Moreover, since the focus is on the interplay between the prefetching strategy and the application characteristics, we do not discuss detailed design issues of hardware and language systems, which also need further research.

#### 1.3 Contributions

The important contributions of this thesis are:

- Analyses of sharing patterns and program structures of parallel applications that explain the behavior of deliver and prefetch operations.

- A proposal and comparison of several techniques that improve the efficiency of deliver operations by using various types of knowledge about sharing patterns.

- An analysis of working-set and communication characteristics of parallel applications that explains the cache behavior for the deliver and the prefetch schemes.

- A quantitative comparison of the deliver and the prefetch schemes in a large design space of architectural parameters.

### 1.4 Organization of Dissertation

Chapter 2 presents hardware and software mechanisms that we assume for the deliver and the prefetch schemes. The two schemes are software-controlled so that we use software knowledge to insert cache transfer operations in applications. The deliver scheme uses an extra hardware mechanism to keep track of past sharing behavior for each cache line. We summarize research issues to improve the accuracy of past behavior as a predictor for future behavior. Furthermore, we qualitatively compare characteristics of the two schemes.

Chapter 3 describes the simulation environment for this thesis. Since a large number of parameters affect the behavior of the deliver and the prefetch schemes, we need to design our experiments carefully to complete a wide range of simulations in a feasible time. We discuss the simulation methodology and the benchmark applications that are used in this thesis.

Chapter 4 analyzes simulation results to examine sharing characteristics of parallel applications and their effects on the behavior of prefetch and deliver operations. For irregular memory access patterns, both schemes may transfer a large number of unnecessary cache lines. For the deliver scheme, we identify sharing patterns that generate unnecessary deliver messages, and we quantitatively examine three techniques that trade off the number of unnecessary deliver messages for the number of eliminated cache misses. For the prefetch scheme, we show that the prefetch scheme has a significant advantage over the deliver scheme since a simple mechanism can eliminate most of unnecessary cache transfers.

Chapter 5 discusses the effect of various architectural parameters for the performance of prefetch and deliver operations. First, we focus on the miss-rate characteristics. One of the most important results in this chapter is that the cache size needs to be about as large as the largest working set of the application before we can obtain most of the benefit due to deliver operations. We examine the working-set and the communication characteristics to understand this behavior of deliver operations. Next, we discuss the traffic characteristics: we compare applications' demand traffic with feasible bandwidth for major system components. Finally, we evaluate the execution-time improvement due to deliver and prefetch operations by simulating the contention delay in the memory system.

Finally, Chapter 6 summarizes our discussions about the behavior of deliver and prefetch operations and the characteristics of parallel applications.

## Chapter 2

## **Producer-oriented and Consumer-oriented Approaches**

In this chapter, we discuss hardware and software mechanisms for the deliver and the prefetch schemes and qualitatively compare the two schemes. Both schemes hide the memory latency by using a software-controlled non-binding mechanism. The schemes are software-controlled; we use software knowledge to insert a cache-line transfer operation — deliver or prefetch — for maximum hiding of memory latencies. The schemes are non-binding; the transfer operation does not bind the transferred value to a shared variable, so that the transfer operation is a performance hint and does not affect the correctness of the program. Other researchers have shown that non-binding mechanisms are necessary to achieve good performance [44]. While both schemes need to exploit hardware and software knowledge for maximum performance gain, the two schemes exploit different kinds of knowledge as we will discuss in the chapter.

This chapter is organized as follows. Section 2.1 describes the concept of the deliver scheme, which includes the strategy for inserting deliver operations, the hardware mechanism, and variations on the deliver scheme. Section 2.2 describes the concept of the prefetch scheme and qualitatively compares the prefetch and the deliver schemes.

## 2.1 Producer-oriented Deliver

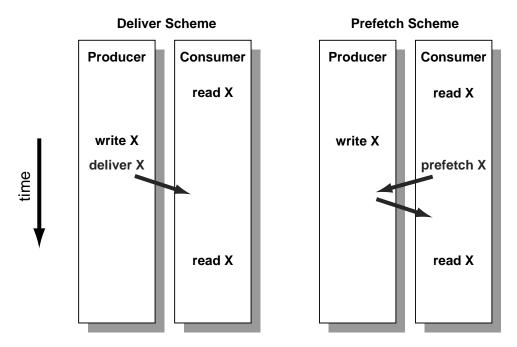

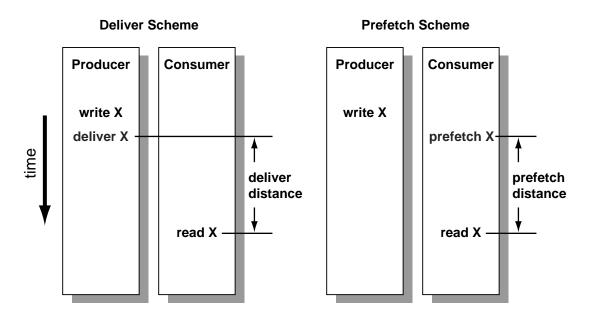

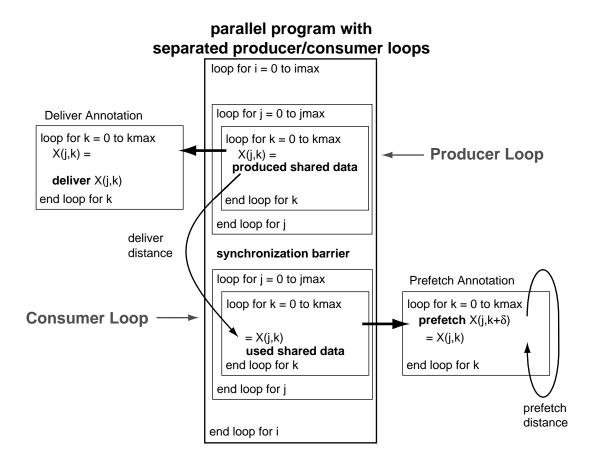

Figure 2-1 illustrates an example of deliver and prefetch operations. The producer transfers the produced value to consumer's caches in the deliver scheme, so that the consumer can read the value without causing a cache miss. In the prefetch scheme, on the other hand, the consumer fetches the produced value. The producer-initiated transfer has several advantages over the consumer-initiated transfer: (1) The producer can transfer the pro-

Figure 2-1: An Example of Deliver and Prefetch Operations

duced value when it is produced, which is the earliest possible time. The consumer, on the other hand, may transfer the value too early before it is produced or too late to use it in time; (2) The latency of the producer-initiated transfer is a one-way latency from the producer to the consumer, while the latency of the consumer-initiated transfer is a round-trip latency between the consumer and the producer; (3) The producer can easily find the address of the value to be transferred, while the consumer may not be able to find the address early enough to obtain the value in time. For example, if the application intensively uses a linked list, the consumer cannot prefetch an element in the list until the consumer fetches another element that contains the address. The producer, on the other hand, knows the address of the value when the value is produced.

While the deliver operation is similar to a send operation in the message passing architecture, the deliver operation is a performance hint. That is, the program works correctly, if no deliver operations are inserted, or even if deliver operations are inserted arbitrarily. In the absence of deliver operations, the cache protocol performs exactly as an invalidate protocol. Conversely, if every write is followed by a deliver operation, the cache protocol performs in a way similar to an update protocol.

A key issue for the producer-initiated transfer is how to predict the consumer that will use the produced value. Our deliver scheme uses hardware knowledge for finding potential consumers. We use a hardware mechanism that keeps track of past sharing patterns. The deliver operation sends a cache line to processors that were sharing the line in a similar manner that the update operation does in the update protocol. The deliver scheme, however, differs from the update protocol in two ways. First, the update protocol does not send update information to processors once their cache replaces the cache line that are being updated. The deliver scheme, on the other hand, can send a cache line to processors even if their cache does not have a copy of the cache line. Second, more importantly, the deliver scheme is much more efficient than the update protocol. The deliver operation aggregates updates for the same cache lines into a single message. The deliver scheme, moreover, uses software knowledge to reduce the amount of the traffic. The programmer or language systems use software knowledge about the program structure to insert deliver operations only where communication is likely to occur.

#### 2.1.1 Strategy for Inserting Deliver Operations

A deliver operation for a shared variable should ideally be inserted where processor-toprocessor communication occurs through the variable. For compiler-parallelized code, the compiler should be able to insert deliver operations in such places since the compiler knows where communication occurs in the code. For explicitly-parallelized code, on the other hand, it is not obvious to find where communication occurs in the code unless the computation is regular.

Our strategy is to use synchronization operations as a hint to find the timing of communication. We insert a deliver operation after the last write of a shared variable before a synchronization operation, so that the written value is sent to prospective readers before they start reading the variable. For synchronized programs, it should be relatively straightforward to find such places for deliver operations. For non-synchronized programs, the ideal location is where a processor finishes a series of writes for shared variables and other processors are likely to read the variables. For the non-synchronized programs that we studied, it was straightforward to find such places.<sup>1</sup>

<sup>1.</sup> MP3D and LocusRoute. See Section 3.2.

```

for loop of i {

for loop of i {

sharedArray[i] = ...

sharedArray[i] = ...

sharedArray[i+1] = ...

deliver(sharedArray + i)

loop

unrolling

*ptr1 = ...

*ptr1 = ...

*ptr2 = ...

*ptr2 = ...

deliver(ptr1)

conditional

if (ptr1 and ptr2 are not in the same block)

deliver

deliver(ptr2)

```

Figure 2-2: Deliver Annotation Techniques.

Because the unit of communication is a cache line, we actually insert the deliver operation after the last write for a cache line containing shared variables instead of the last write for each shared variable. For some applications, this requires transformations to the program if the deliver is to obtain the best performance. Figure 2-2 shows two typical cases. In the first case, the loop is unrolled so that the same line is delivered only once. In the second case, the test statement checks if two writes are to the same line. These modifications increase the probability that a single deliver operation updates all the modified words in the same line, thus reducing the number of deliver messages. These sorts of optimizations are direct analogies to transformations that a compiler or programmer might perform to improve the performance of invalidate protocols by increasing the spatial clustering of shared data in multi-word lines.

In spite of these annotation techniques, the deliver scheme generates some unnecessary deliver messages for applications with irregular computations because communication does not occur after every synchronization operation and because not all of the deliver destinations use the delivered cache line. We use more software knowledge to improve the efficiency of the deliver scheme. Since the performance gain due to the deliver scheme depends on the trade-off between the cache-miss reduction and the traffic overhead, we should insert the deliver operation where the ratio between the number of eliminated cache-misses and the number of deliver-messages is relatively high. We call this technique *Selective Deliver*. Our simulator obtains the ratio for all locations where a deliver operation is potentially inserted. We will examine the simulation results in Section 4.1 to investigate the effect of program structures for the efficiency of deliver operations.

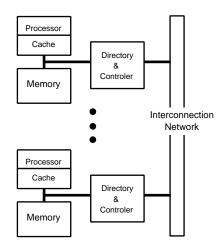

Figure 2-3: NUMA Model.

### 2.1.2 Hardware Mechanisms for the Deliver Operation

We assume a directory-based cache-coherent NUMA machine (e.g. Alewife [10] and DASH [40]), as illustrated in Figure 2-3. The main memory is distributed among processor nodes. Each node has a directory that keeps track of which nodes are caching each memory block of the node. We assume that each processor cache is kept coherent using an invalidate protocol. When a processor writes a shared variable, the processor sends a write request to the home node, which corresponds to the memory address of the variable. Then, the home node looks up the processors sharing the address in the directory and sends an invalidation request to the sharing processors (except the node of the original writer). Those nodes return an acknowledgment message to the home node, which collects all acknowledgment messages and notifies the original writer of the completion of the invalidation.

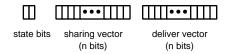

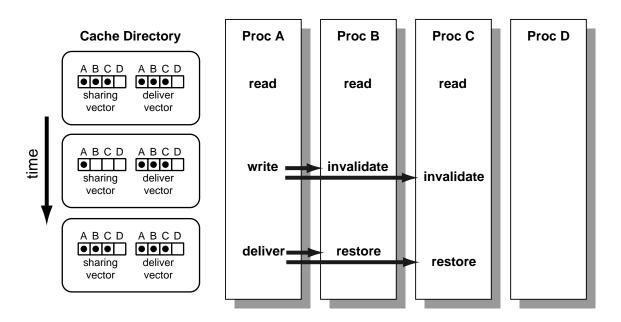

We assume each entry of the cache directory has two bit-vectors as shown in Figure 2-4. One bit-vector, the sharing vector, holds the identity of processors that may be currently sharing the copy of the cache line. The second one, the deliver vector, holds the identity of processors that the deliver operation sends the cache line to. The directory controller manages the sharing vector just as in a conventional cache directory with replacement hints. Each bit of the sharing vector is set when a copy of the line is sent to the corresponding processor, and cleared when the processor's copy is invalidated or replaced. The deliver

<sup>2.</sup> We will discuss more details about the cache protocol in Subsection 5.3.1.

Figure 2-4: Cache Directory Entry for Each Cache Line (*n* processors).

vector, on the other hand, is managed in a different way from the sharing vector. Each bit of the deliver vector is set when a copy of the line is sent to the corresponding processor, but not cleared when the processor's copy is invalidated. If the deliver vector is never cleared, the deliver vector holds the identity of all processors that have touched the line, so that deliver operations probably send a cache line to processors that will not access the line anymore. In the next subsection, we will discuss techniques (e.g., the use of replacement hints) to manage the deliver vector so that it holds only the identity of processors that will probably use the line.

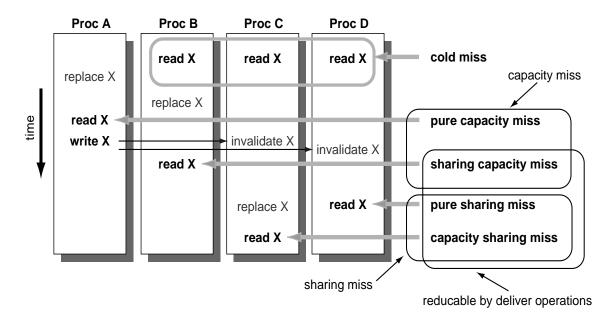

Figure 2-5 illustrates an example of how this cache directory operates for the deliver operation. In this example, three processors (Proc A, Proc B, and Proc C) share the same cache line. A producer (Proc A) writes the cache line, which is read by two consumers (Proc B and Proc C). First, the three processors read the cache line. As the cache directory receives a read request from a processor, the directory turns on the corresponding bit in the sharing

Figure 2-5: An Example of Cache Directory Operations.

and the deliver vectors. Second, Proc A writes the cache line. When the cache directory receives the write request, the directory sends an invalidate request to Proc B and Proc C and turns off the bit for the two processors in the sharing vector. The cache directory does not change the deliver vector, which keeps track of past sharing processors. On receiving the invalidate request, the two processors send back an acknowledgment to the directory. Third, Proc A delivers the cache line to the cache directory. The directory updates the main memory for the cache line, looks up the deliver vector, and forwards the cache line to Proc B and Proc C. On receiving the cache line, the two processors send back an acknowledgment to the directory. Thus, the consumers obtain the new copy of the cache line without causing a cache miss.

Conventional invalidate and update protocols need only one vector, the sharing vector, per cache line. Our protocol assumes two vectors per cache line; the sharing vector is used to identify the processors to which an invalidate request is sent, while the deliver vector is used to identify the processors to which a deliver message is sent. This additional deliver vector allows us to reduce the number of unnecessary deliver messages. We discuss the benefit of the deliver vector by examining a sharing pattern example shown in Figure 2-6. The four processors share the same cache line; Proc A is a producer and the rest of the pro-

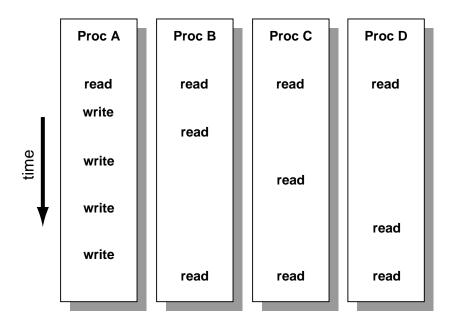

Figure 2-6: An Example of Sharing Patterns. Proc A is a producer and the rest of the processors are a consumer.

cessors are a consumer. First, the four processors read the cache line, so that the sharing vector holds the identify of those processors. Then, Proc A writes the cache line four times. Only one consumer does read the produced value for the first three writes, while all consumers read the produced value for the fourth write. Since the deliver vector remembers past sharing information regardless the current sharing status, we can use deliver operations only when the past sharing pattern is a good predictor of the future access pattern. For the example shown in Figure 2-6, the producer-consumer relation for the first three writes is not ideal for the deliver scheme; only one of the consumers use the produced value. If we insert deliver operations after those writes, we generate unnecessary messages. The producer-consumer relation for the fourth write, on the other hand, is ideal for the deliver scheme; all the consumers use the produced value. Since the deliver vector remembers the past sharing pattern, a deliver operation sends the cache line to all the consumers if we insert a deliver operation immediately after the fourth write. If we do not have the deliver vector, however, the cache directory remembers only the last consumer (Proc D), so that the deliver operation sends the cache line only to Proc D.

Furthermore, the deliver vector allows consumers to reduce the number of unnecessary messages. That is, a consumer can enable or disable the subscription of deliver messages, whether the cache has a copy of the cache line or not. If a consumer knows that it will not access a cache line for a long time, the consumer can cancel the subscription of deliver messages for the cache line by sending a special message to the directory, which turns off the corresponding bit in the deliver vector. We will discuss more details about techniques that manage the subscription of deliver messages in Subsection 2.1.3.

We can reduce the directory space by using several techniques including limited pointer schemes [1]. If the cache directory is controlled by software on a special processor, further reduction is possible. Optimizing the cache-directory space, however, is beyond our scope, and we do not discuss the issue in this thesis.

## 2.1.3 Variations on the Deliver Operation

In this subsection, we qualitatively discuss variations on the deliver operation for maximizing the performance benefit, which will be quantitative examined by using simulation results in Chapter 4 and Chapter 5. As discussed previously, our deliver mechanism relies

| Trade-off Technique  | Initiator | Mechanism | Information for Trade-off                            |  |

|----------------------|-----------|-----------|------------------------------------------------------|--|

| Selective Deliver    | Producer  | Software  | The number of sent messages per eliminated miss.     |  |

| Competitive Back-off | Consumer  | Hardware  | The number of received messages per eliminated miss. |  |

| Subscription Control | Consumer  | Software  | The number of received messages per eliminated miss. |  |

Table 2-1: Three Trade-offs between the Number of Deliver Messages and the Number of Eliminated Misses.

on the past sharing behavior that is stored in the deliver vector. In reality, the past sharing behavior does not always accurately predict the future behavior. Thus, a deliver operation may send an unnecessary message that the destination processor will not use, hence deliver operations may waste some network bandwidth and some space in the cache memory of the deliver destination. The difficulty of predicting future sharing patterns raises two important issues. First, how can we trade off the number of unnecessary deliver messages versus the number of eliminated cache misses? Second, how can we design a replacement policy to minimize the number of evictions of necessary cache lines due to unnecessary deliver messages?

In Section 4.1, we will evaluate three techniques, shown in Table 2-1, to trade off the number of unnecessary deliver messages versus the number of eliminated cache misses. The three techniques are divided into two types: producer-initiated and consumer-initiated. *Selective Deliver* has been discussed in the preceding subsection. This technique is producer-initiated because the producer controls the timing of deliver operations. This technique is also software-controlled because it relies on a software system that analyzes the sharing pattern and controls the insertion of deliver operations. In this study, we select the insertion place for the deliver operation by using a profiling system that counts the number of sent messages per eliminated miss for each candidate of the insertion place.

The other two techniques are consumer-initiated; a consumer manages the deliver vector in the cache directory to trade off the number of unnecessary deliver messages versus the number of eliminated cache misses. *Subscription Control* is software-controlled; it relies on a software system that controls the insertion of a special operation that removes the