# AUTOMATIC COMPUTATION AND DATA DECOMPOSITION FOR MULTIPROCESSORS

Jennifer-Ann Monique Anderson

Technical Report: CSL-TR-97-719

March 1997

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, CA 94305-9040

#### **Abstract**

Memory subsystem efficiency is critical to achieving high performance on parallel machines. The memory subsystem organization of modern multiprocessor architectures makes their performance highly sensitive to both the distribution of the computation and the layout of the data. A key issue in programming these machines is selecting the *computation decomposition* and *data decomposition*, the mapping of the computation and data, respectively, across the processors of the machine.

A popular approach to the decomposition problem is to require programmers to perform the decomposition analysis themselves, and to communicate that information to the compiler using language extensions. This thesis presents a new compiler algorithm that automatically calculates computation and data decompositions for dense-matrix scientific codes. The core of the algorithm is based on a linear algebra framework for expressing and calculating the computation and data decompositions. Using the linear algebra model, the algorithm generates a system of equations that specifies the conditions the desired decompositions must satisfy. The decompositions are then calculated systematically by solving the system of equations. Since the best decompositions may change as different phases of the program are executed, the algorithm also considers re-organizing the data dynamically. The analysis is performed both within and across procedure boundaries so that entire programs can be analyzed.

We have incorporated our techniques into the SUIF parallelizing compiler system. We evaluated the effectiveness of the algorithm by applying the compiler to a suite of benchmark programs, and compared the performance of the resulting code to the performance obtained without using our techniques. We found that our decomposition analysis and optimization can lead to significant increases in program performance.

**Key Words and Phrases:** parallelization, compiler optimization, data decomposition, computation decomposition

© Copyright 1997 by Jennifer-Ann Monique Anderson All Rights Reserved

### Acknowledgements

I would like to thank my advisor Monica Lam for her enthusiasm and support. She dedicated a great deal of time and energy to this work, and she always encouraged me to do my very best. I also feel fortunate to have had John Hennessy and Anoop Gupta on my thesis committee. I thank them for their insightful comments and guidance.

I had the privilege of working with many smart and talented people during my time at Stanford. Saman Amarasinghe wrote a lot of code that was integral to getting the SUIF parallelizer used in this thesis up and running. Also, the interprocedural decomposition algorithm described in Chapter 6 is built on top of Saman's linear inequality framework for parallelizing compilers. Saman is insightful, motivated and creative, and I always enjoyed working with him. The compiler-directed page coloring optimization described in Chapter 2 is joint work with Ed Bugnion, who is both very talented and great fun to work with. I also wish to thank all the members of the SUIF compiler group, including Saman Amarasinghe, Robert French, Mary Hall, David Heine, Shih-Wei Liao, Amy Lim, Dror Maydan, Todd Mowry, Brian Murphy, Jason Nieh, Jeff Oplinger, Karen Pieper, Martin Rinard, Patrick Sathyanathan, Dan Scales, Brian Schmidt, Mike Smith, Steve Tjiang, Chau-Wen Tseng Bob Wilson, Chris Wilson and Michael Wolf. In particular, Bob Wilson and Chris Wilson wrote much of the code that forms the base of the SUIF system, and Chris has done an amazing job of keeping the entire SUIF system running smoothly.

I would also like to thank Digital's Western Research Lab for awarding me a graduate fellowship. Anita Borg was my mentor at WRL, and she is a great source of advice and moral support.

I am fortunate to have a wonderful set of family and friends that encouraged me during my time in graduate school. I thank my parents for instilling in me a love a learning that led me to pursue this degree. Above all, I would like to thank my husband Grant for his constant love, understanding and support. I consider myself extremely fortunate to have such a wonderful husband.

This work was supported in part by ARPA contracts DABT63-91-K-0003 and DABT63-94-C-0054, and a fellowship from Digital's Western Research Lab.

# **Contents**

| A | cknov | ledgeme   | nts                                | V  |

|---|-------|-----------|------------------------------------|----|

| 1 | Intr  | oduction  |                                    | 1  |

|   | 1.1   | Multipro  | ocessor Memory Hierarchies         | 2  |

|   |       | 1.1.1     | Communication Latencies            | 3  |

|   |       | 1.1.2     | Multiprocessor Cache Effects       | 6  |

|   | 1.2   | Problem   | Statement                          | 9  |

|   | 1.3   | Thesis C  | Overview and Contributions         | 11 |

|   | 1.4   | Thesis C  | Organization                       | 13 |

| 2 | Con   | piler Ov  | erview                             | 14 |

|   | 2.1   | Domain    | of Applications                    | 16 |

|   | 2.2   | Pre-Para  | allelization Analyses              | 17 |

|   | 2.3   | Paralleli | zation Analysis                    | 17 |

|   |       | 2.3.1     | Choices of Parallelism             | 18 |

|   |       | 2.3.2     | Global Considerations              | 22 |

|   | 2.4   | Decomp    | osition Analysis Overview          | 23 |

|   | 2.5   | Parallel  | Code Generation and Optimization   | 24 |

|   |       | 2.5.1     | Distributed Address Space Machines | 24 |

|   |       | 2.5.2     | Shared Address Space Machines      | 25 |

|   | 2.6   | Uniproc   | essor Locality Optimizations       | 26 |

|   | 2.7   | Summar    | y                                  | 27 |

| 3 | Con   | nputation | and Data Decomposition Basics      | 28 |

|   | 3.1  | Machin  | ne and Coi   | mmunication Models                                     | 28 |

|---|------|---------|--------------|--------------------------------------------------------|----|

|   | 3.2  | Mathe   | matical De   | ecomposition Model                                     | 31 |

|   |      | 3.2.1   | Virtual P    | rocessor Mapping                                       | 31 |

|   |      |         | 3.2.1.1      | Properties of Affine Decompositions                    | 32 |

|   |      |         | 3.2.1.2      | Relationship between Computation and Data              | 34 |

|   |      | 3.2.2   | Physical     | Processor Mapping                                      | 36 |

|   | 3.3  | Summa   | ary          |                                                        | 38 |

| 4 | A St | atic-De | compositi    | on Algorithm                                           | 39 |

|   | 4.1  | Findin  | g Virtual P  | Processor Mappings                                     | 39 |

|   |      | 4.1.1   | General A    | Approach for Finding Affine Decompositions             | 40 |

|   |      | 4.1.2   | Basic Lir    | near Decompositions                                    | 41 |

|   |      |         | 4.1.2.1      | Formulating the Equations                              | 42 |

|   |      |         | 4.1.2.2      | Examples of Basic Linear Decompositions                | 43 |

|   |      |         | 4.1.2.3      | Solving the Equations                                  | 46 |

|   |      | 4.1.3   | Linear D     | ecompositions with Replication                         | 64 |

|   |      |         | 4.1.3.1      | Formulating Equations with Replication                 | 65 |

|   |      |         | 4.1.3.2      | Examples of Linear Decompositions with Replication .   | 69 |

|   |      |         | 4.1.3.3      | Solving Equations with Replication                     | 70 |

|   |      |         | 4.1.3.4      | Broadcast and Multicast Communication                  | 71 |

|   |      | 4.1.4   | Linear D     | ecompositions with Synchronization                     | 73 |

|   |      |         | 4.1.4.1      | Formulating Equations with Synchronization             | 74 |

|   |      |         | 4.1.4.2      | Examples of Linear Decompositions with Synchronization | 74 |

|   |      |         | 4.1.4.3      | Solving Equations with Synchronization                 | 76 |

|   |      | 4.1.5   | Algorith     | m Summary: Linear Decompositions                       | 76 |

|   |      | 4.1.6   | Finding (    | Offset Decompositions                                  | 77 |

|   | 4.2  | Findin  | g Physical   | Processor Mappings                                     | 80 |

|   | 4.3  | Summa   | ary          |                                                        | 82 |

| 5 | A D  | ynamic- | Decompo      | sition Algorithm                                       | 84 |

|   | 5.1  | Formu   | lation of th | ne Dynamic Decomposition Problem                       | 84 |

|   |      | 5 1 1   | Program      | Representation                                         | 25 |

|   |      | 5.1.2    | Problem Statement                                             | 9   |

|---|------|----------|---------------------------------------------------------------|-----|

|   | 5.2  | Compl    | exity of the Dynamic Decomposition Problem                    | 1   |

|   | 5.3  | Finding  | g Dynamic Decompositions                                      | 3   |

|   | 5.4  | A Dyn    | amic Decomposition Example                                    | C   |

|   | 5.5  | Related  | d Work                                                        | 5   |

|   |      | 5.5.1    | Communication-Free Parallelism                                | 6   |

|   |      | 5.5.2    | Data Parallelism                                              | 7   |

|   |      | 5.5.3    | Loop Nest Parallelism                                         | 2   |

|   |      | 5.5.4    | Discussion                                                    | 5   |

|   | 5.6  | Summa    | ary                                                           | 5   |

| 6 | An l | Interpro | ocedural Decomposition Algorithm 11                           | 7   |

|   | 6.1  | When     | is Interprocedural Analysis Needed?                           | 8   |

|   | 6.2  | Finding  | g Virtual Processor Mappings                                  | C   |

|   |      | 6.2.1    | Mapping Affine Functions Across Calls                         | . 1 |

|   |      | 6.2.2    | Bottom-up Traversal                                           | ,4  |

|   |      |          | 6.2.2.1 Propagating Decompositions into Calling Procedures 12 | 4   |

|   |      |          | 6.2.2.2 Propagating Array Accesses into Calling Procedures 13 | C   |

|   |      |          | 6.2.2.3 Moving up the Call Graph                              | 2   |

|   |      | 6.2.3    | Top-down Traversal                                            | 3   |

|   | 6.3  | Finding  | g Physical Processor Mappings                                 | 5   |

|   | 6.4  | An Inte  | erprocedural Decomposition Example                            | 5   |

|   | 6.5  | Issues   | in Interprocedural Decomposition Analysis                     | .2  |

|   |      | 6.5.1    | Unnecessary Storage Reuse                                     | 3   |

|   |      | 6.5.2    | Array Reshapes                                                | .4  |

|   |      | 6.5.3    | Insufficient Type Information                                 | 6   |

|   | 6.6  | Librari  | es and User-Defined Decompositions                            | .7  |

|   | 6.7  | Summa    | ary                                                           | 8   |

| 7 | Exp  | eriment  | al Results 14                                                 | 9   |

|   | 7.1  | Experi   | mental Setup                                                  | 9   |

|   |      | 7 1 1    | Target Architectures 1/1                                      | c   |

| Bi | bliogi | raphy    |                                          | 183 |

|----|--------|----------|------------------------------------------|-----|

|    | 8.2    | Future   | Work                                     | 182 |

|    |        |          | butions                                  |     |

| 8  | Con    | clusions | S                                        | 179 |

|    |        | 7.2.3    | Summary of Results                       | 177 |

|    |        | 7.2.2    | Centralized Shared Address Space Machine | 166 |

|    |        | 7.2.1    | Distributed Shared Address Space Machine | 158 |

|    | 7.2    | Experi   | mental Results                           | 158 |

|    |        | 7.1.4    | Application Suite                        | 155 |

|    |        | 7.1.3    | Methodology                              | 151 |

|    |        | 7.1.2    | The SUIF Compiler                        | 151 |

# **List of Tables**

| 1.1 | Typical remote memory access times                                    | 4   |

|-----|-----------------------------------------------------------------------|-----|

| 7.1 | Descriptions of the benchmarks                                        | 155 |

| 7.2 | Data set sizes of the benchmarks                                      | 156 |

| 7.3 | Parallel coverage and 32-processor speedups for the benchmarks on the |     |

|     | DASH multiprocessor                                                   | 157 |

| 7.4 | Parallel coverage and 8-processor speedups for the benchmarks on the  |     |

|     | Digital AlphaServer                                                   | 158 |

| 7.5 | Summary of results on the Stanford DASH Multiprocessor                | 168 |

| 7.6 | Summary of results on the AlphaServer 8400                            | 178 |

# **List of Figures**

| 1.1 | An example to illustrate multiprocessor memory hierarchy issues                                  | 5  |

|-----|--------------------------------------------------------------------------------------------------|----|

| 1.2 | Speedups for the SPEC95 benchmark tomcatv on the AlphaServer 8400                                | 8  |

| 2.1 | The design of a parallelizing compiler system for both shared and distributed                    |    |

|     | address space machines.                                                                          | 15 |

| 2.2 | Illustration of parallel execution                                                               | 20 |

| 3.1 | Basic machine model used by the decomposition analysis                                           | 29 |

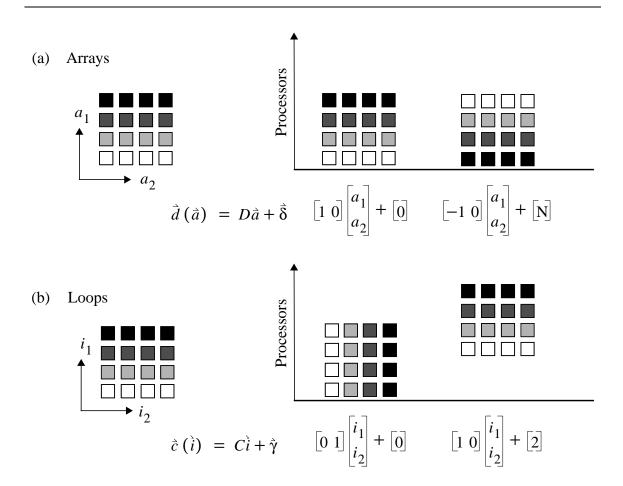

| 3.2 | Sample affine decompositions onto a virtual processor space                                      | 34 |

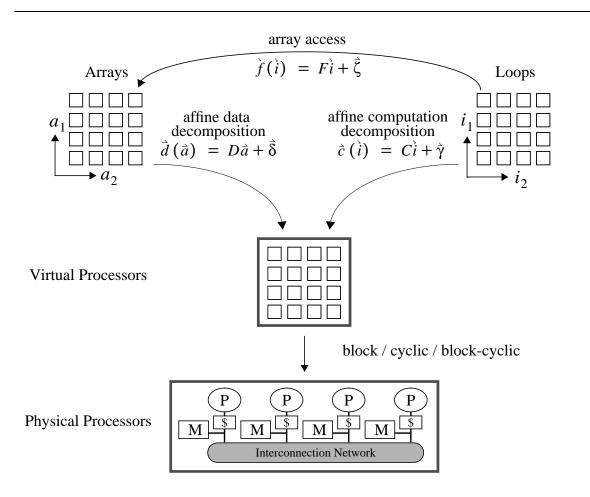

| 3.3 | Two-step model of computation and data decompositions                                            | 36 |

| 3.4 | Example of HPF decompositions and the corresponding virtual and physical                         |    |

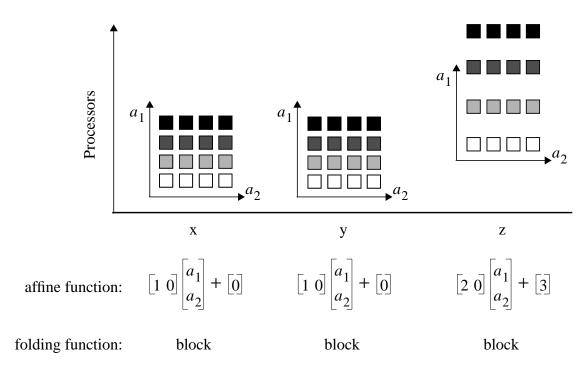

|     | processor mappings under our decomposition model                                                 | 37 |

| 4.1 | Code examples used to illustrate linear decompositions                                           | 44 |

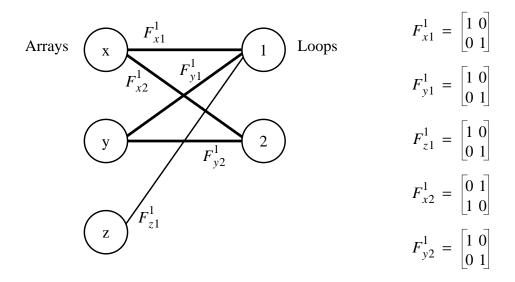

| 4.2 | A sample interference graph                                                                      | 48 |

| 4.3 | Algorithms for mapping between linear data decompositions and linear computation decompositions. | 51 |

| 4.4 | -                                                                                                | 31 |

| 4.4 | Algorithm for propagating the nullspaces of linear decomposition matrices                        | 57 |

| 4.5 | between loop nests and arrays.                                                                   | 31 |

| 4.5 | Algorithm for calculating the nullspaces of the basic linear decomposition                       | 58 |

| 1.0 | matrices.                                                                                        |    |

| 4.6 | Algorithm for calculating the linear decomposition matrices                                      | 62 |

| 4.7 | Code used to illustrate linear decompositions with replication                                   | 65 |

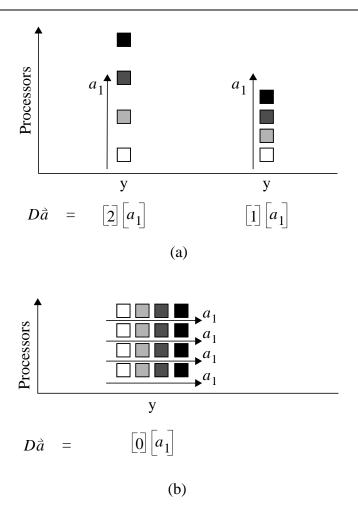

| 4.8 | Example showing linear data decompositions onto a one-dimensional vir-                           |    |

|     | tual processor space with different types of replication.                                        | 66 |

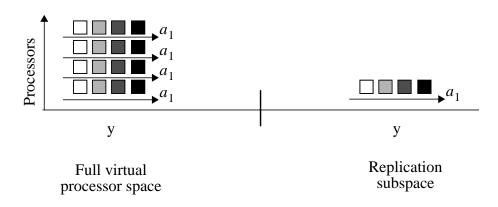

| 4.9  | An example of dimension replication                                         | 67  |

|------|-----------------------------------------------------------------------------|-----|

| 4.10 | Algorithms for calculating linear data decompositions with replication      | 72  |

| 4.11 | Algorithm for calculating the nullspaces of the linear decomposition matri- |     |

|      | ces with multicast and synchronization.                                     | 78  |

| 4.12 | Algorithm for calculating linear decompositions with replication, multicast |     |

|      | and synchronization                                                         | 79  |

| 4.13 | Algorithm for finding static decompositions.                                | 82  |

| 5.1  | Code example used to illustrate dynamic decompositions                      | 86  |

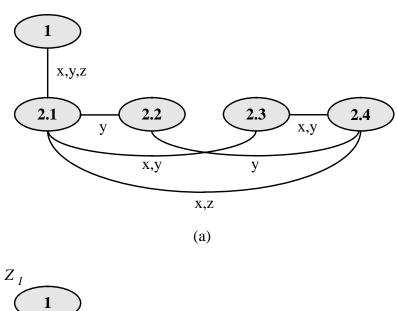

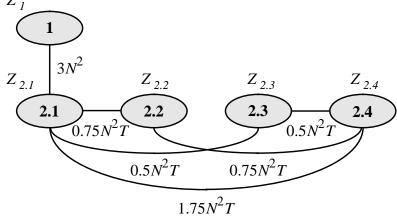

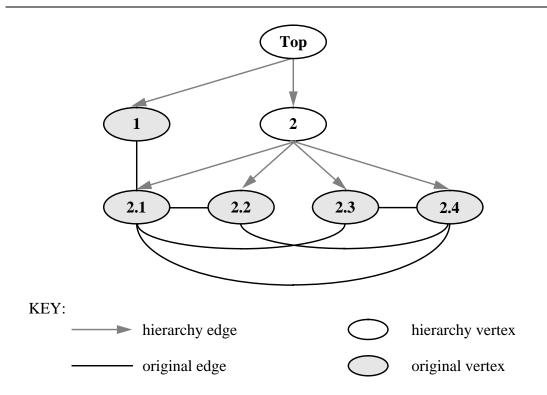

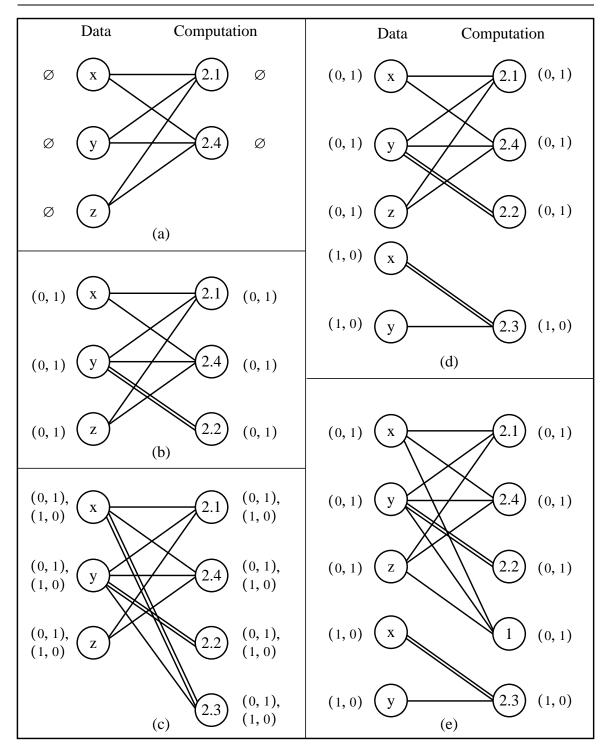

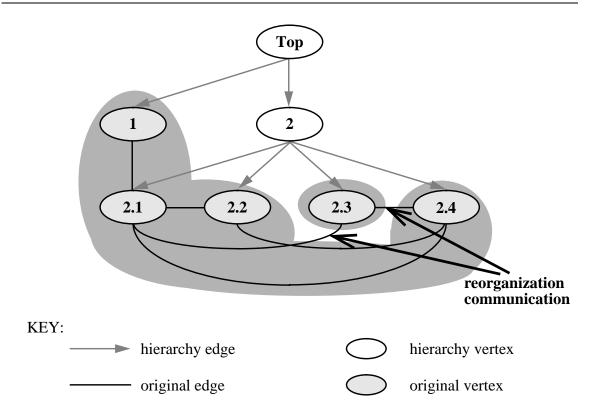

| 5.2  | Example communication graphs                                                | 87  |

| 5.3  | Example communication graph with hierarchical structure                     | 95  |

| 5.4  | Driver algorithm for finding dynamic decompositions                         | 96  |

| 5.5  | Core algorithm for finding dynamic decompositions.                          | 97  |

| 5.6  | Algorithm for finding dynamic decompositions at a single level of the       |     |

|      | communication graph                                                         | 98  |

| 5.7  | Merging loop nests using interference graphs                                | 101 |

| 5.8  | Communication graph with static decomposition regions                       | 104 |

| 6.1  | Code examples used to illustrate interprocedural decomposition analysis     | 119 |

| 6.2  | Algorithm for creating call vertices in the caller's communication graph    | 126 |

| 6.3  | Algorithm for gathering the array accesses in a callee procedure            | 131 |

| 6.4  | Algorithm for propagating decomposition constraints up the call graph       |     |

|      | representing the program.                                                   | 132 |

| 6.5  | Algorithm for recording linear decompositions in the callee's communica-    |     |

|      | tion graph from call vertices in the caller's communication graph           | 134 |

| 6.6  | Algorithm for propagating linear data decompositions down the call graph    |     |

|      | representing the program.                                                   | 136 |

| 6.7  | Interprocedural algorithm for finding decompositions                        | 137 |

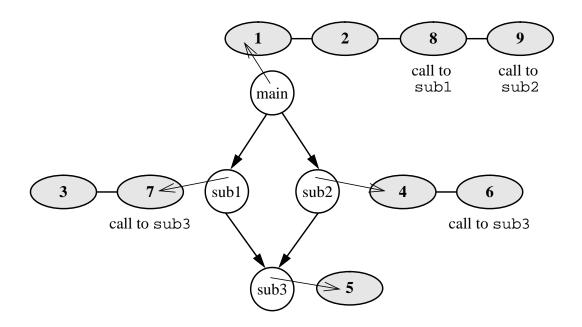

| 6.8  | Sample code with multiple procedures                                        | 138 |

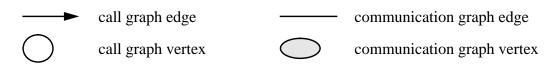

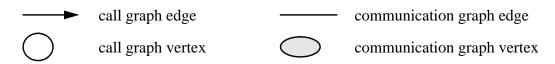

| 6.9  | Call graph and the corresponding communication graphs during the bottom-    |     |

|      | un travarcal                                                                | 130 |

| 0.10 | Can graph and the corresponding communication graphs during the top-    |     |

|------|-------------------------------------------------------------------------|-----|

|      | down traversal                                                          | 141 |

| 7.1  | An overview of the SUIF parallelizing compiler for shared address space |     |

|      | machines.                                                               | 153 |

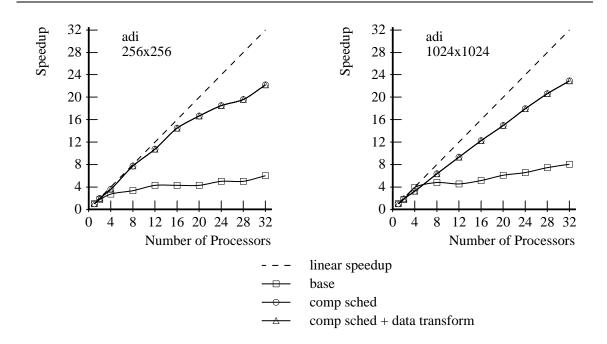

| 7.2  | Speedups for ADI integration on the DASH Multiprocessor.                | 159 |

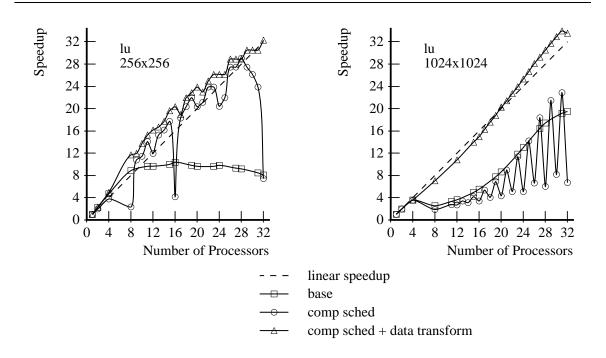

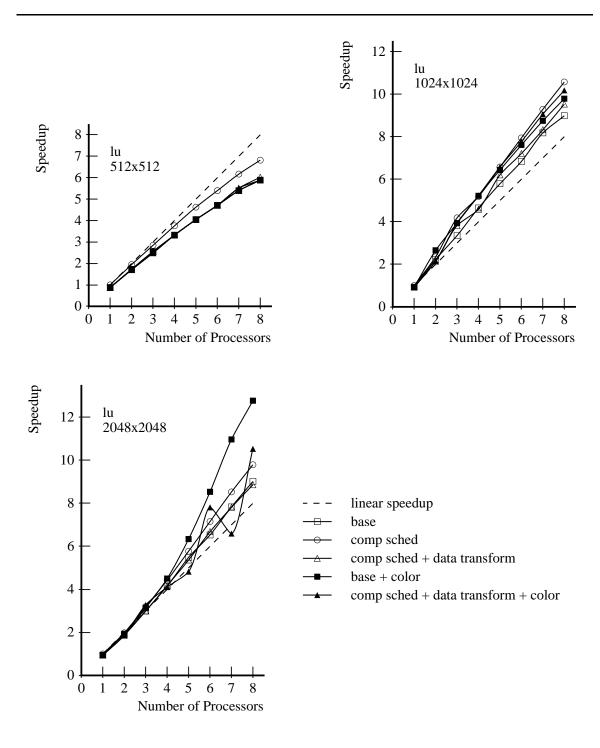

| 7.3  | Speedups for LU decomposition on the DASH Multiprocessor                | 160 |

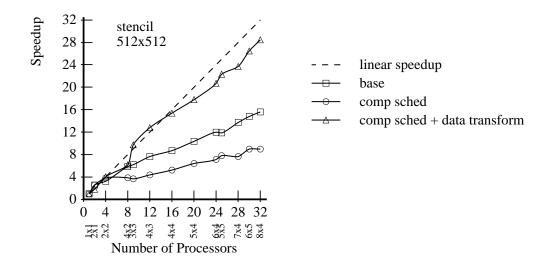

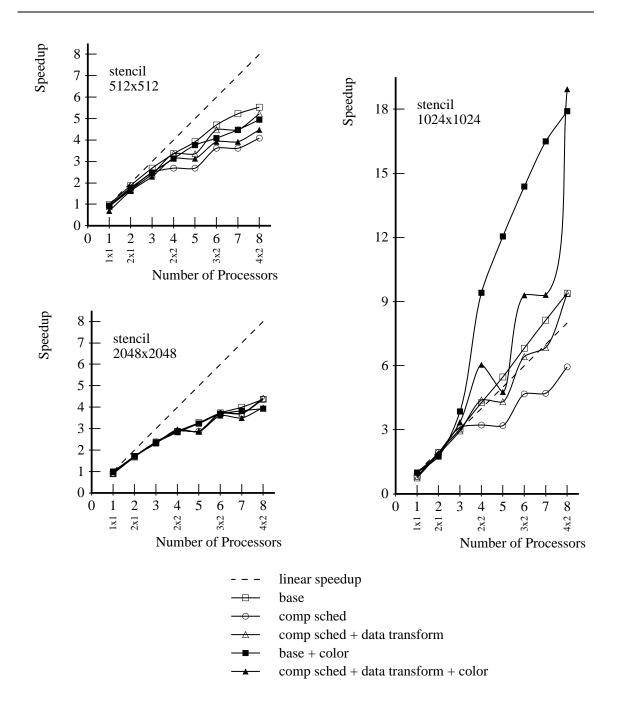

| 7.4  | Speedups for five-point stencil on the DASH Multiprocessor.             | 162 |

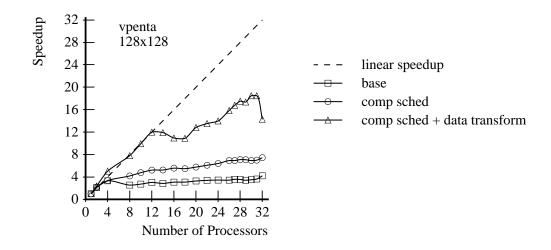

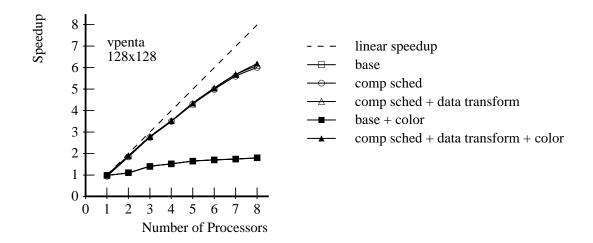

| 7.5  | Speedups for vpenta on the DASH Multiprocessor                          | 163 |

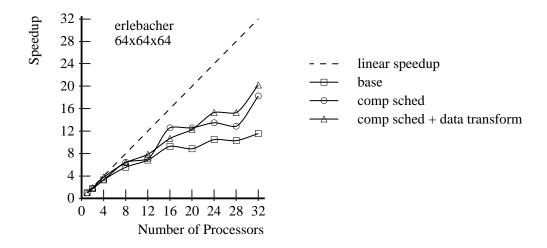

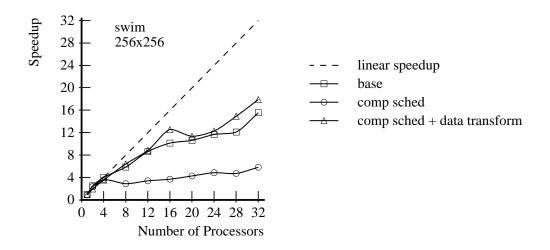

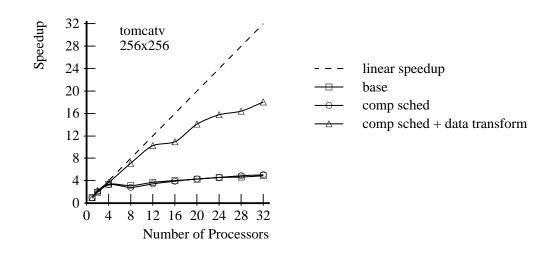

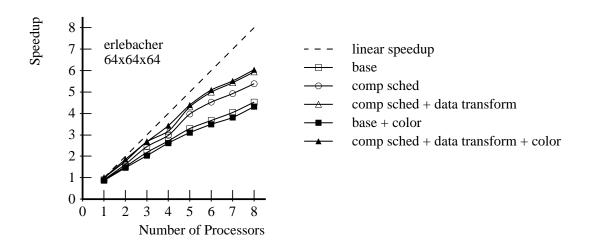

| 7.6  | Speedups for erlebacher on the DASH Multiprocessor                      | 164 |

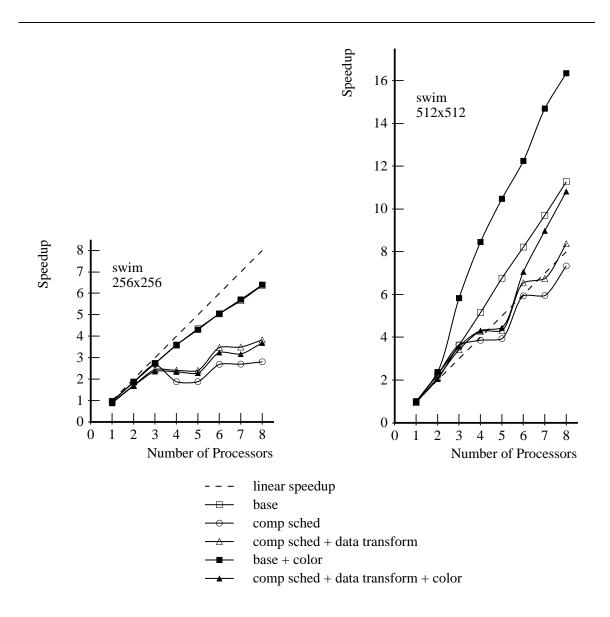

| 7.7  | Speedups for swim on the DASH Multiprocessor                            | 165 |

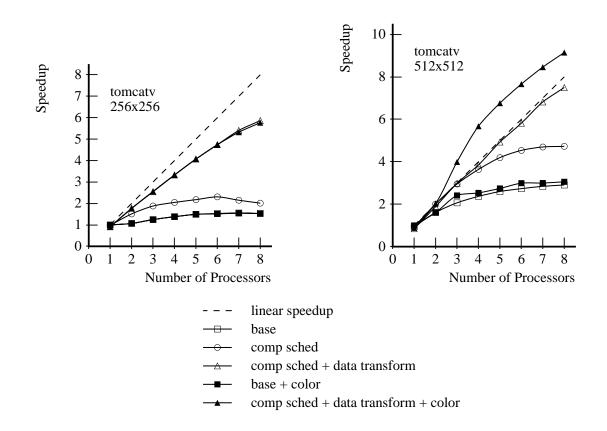

| 7.8  | Speedups for tomcatv on the DASH Multiprocessor.                        | 165 |

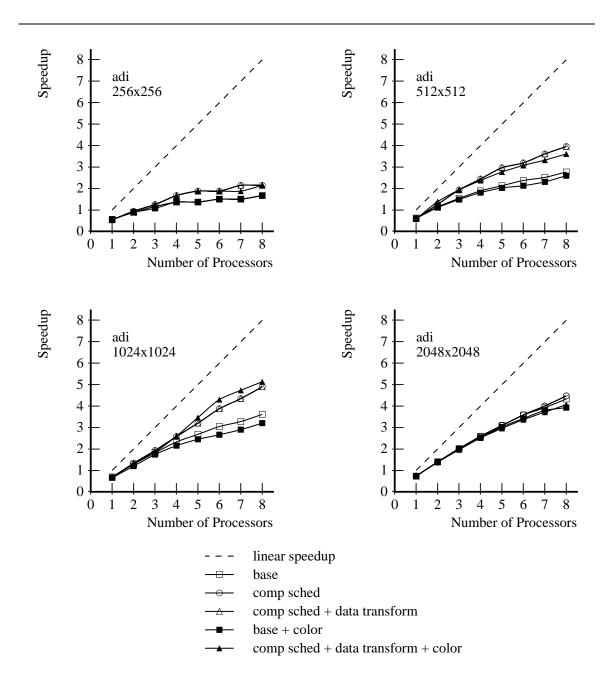

| 7.9  | Speedups for ADI integration on the AlphaServer 8400                    | 167 |

| 7.10 | Speedups for LU decomposition on the AlphaServer 8400                   | 169 |

| 7.11 | Speedups for five-point stencil on the AlphaServer 8400                 | 171 |

| 7.12 | Speedups for vpenta on the AlphaServer 8400                             | 172 |

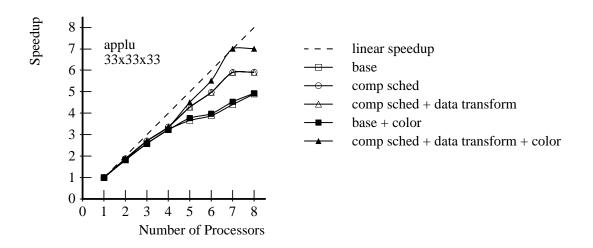

| 7.13 | Speedups for applu on the AlphaServer 8400                              | 173 |

| 7.14 | Speedups for erlebacher on the AlphaServer 8400                         | 173 |

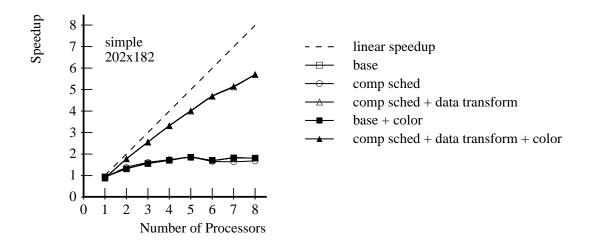

| 7.15 | Speedups for simple on the AlphaServer 8400                             | 174 |

| 7.16 | Speedups for swim on the AlphaServer 8400                               | 175 |

| 7.17 | Speedups for tomcatv on the AlphaServer 8400                            | 177 |

# **Chapter 1**

### Introduction

Processor speeds in modern computer systems are outpacing the memory speeds. The result is that the latency of memory accesses is a bottleneck to achieving high processor utilization. To bridge the gap between processor and memory speeds, computer designers typically use a hierarchy based on different speeds and sizes of memories. Smaller, faster memories or caches are placed close to the processors while successively larger, slower memories are placed farther away from the processors.

The gap between processor speeds and memory speeds is expected to widen. In the last decade, microprocessor performance has been steadily improving at a rate of 50% to 100% every year[39]. Meanwhile, the access times for DRAMs, the components that comprise computer main memories, have been improving at the rate of only 7% per year[39]. As a result, memory subsystem performance will continue to have a great impact on overall computer system performance.

Making effective use of a memory hierarchy relies on a program's *locality of reference*: if a data item is accessed then that data item, or data near it, is likely to be accessed again in the near future. Performance benefits if we are able to keep recently accessed data items in the fastest memories. However, it has been notoriously difficult for scientific codes to make effective use of a memory hierarchy. In fact, various past machines built for scientific computations such as the Cray C90, Cydrome Cydra-5[65] and the Multiflow Trace[24] were all built without caches.

Realizing good memory hierarchy performance on multiprocessors is even more important to application performance than on uniprocessors, but also more difficult. Not only are multiprocessor memory hierarchies supersets of the uniprocessor hierarchy, but the application must also ensure that uniprocessor locality is not compromised by multiprocessor considerations. Any benefits to program performance due to increased parallelism can be quickly outweighed if the program ends up stalled waiting for data. Thus to achieve good performance on parallel systems, programs must take into account both parallelism and locality.

### 1.1 Multiprocessor Memory Hierarchies

There are two principal classes of memory architectures for parallel machines: distributed address space machines and shared address space machines. Distributed address space machines are built from a set of processors connected by a communication network. Each processor has its own local memory that it can access directly; messages have to be sent across the network for a processor to access data stored in another processor's memory. Examples of distributed address space machines include the Intel Paragon, IBM SP-2 and clusters of workstations. In contrast, shared address space machines present the programmer with a single memory space that all processors can access. Many of these machines support hardware cache coherence to keep data consistent across the processors. Shared address space machines may either have a single shared memory that can be uniformly accessed by all the processors, or the memories may be physically distributed across the processors. The former class of machines are often called *centralized* shared address space machines, while the latter class of machines are called *distributed* shared address space machines. Distributing the memories across the processors removes the need for a single shared bus going from all the processors' caches to the memory and thus makes it easier to scale to more processors. Today many computer vendors (e.g. Sun, Digital Equipment, Sequent and Compaq) offer centralized shared address space machines. Examples of distributed shared address space systems include the Stanford DASH[55] and FLASH[54] multiprocessors and MIT ALEWIFE[2] research machines, and the Convex Exemplar, Cray T3D/E and Silicon Graphics Origin commercial machines.

There are two key reasons for why it is more difficult to get good memory subsystem performance on multiprocessors over uniprocessors: long latencies due to inter-processor communication, and multiprocessor-specific cache misses on machines with coherent caches. We discuss each of these reasons in more detail in the following two sections.

#### 1.1.1 Communication Latencies

On current parallel machines, it can cost anywhere from 50 to over 10,000 processor clock cycles to communicate data between processors[39]. The exact communication cost depends on the memory architecture of the machine, the type of interconnection network and the size of the system.

On machines with a centralized memory, cache coherence is typically maintained using an invalidation-based protocol. Data written by one processor is invalidated in the other processors' caches; subsequent reads by the other processors miss in the cache and have to be read from memory. Communication can thus result in cache misses, and the data must be fetched from main memory.

On machines with physically distributed memories, the memory access times are non-uniform. The memory latency to access another processor's memory can be significantly higher than the latency to local memory. In effect, the remote memories on these machines form yet another level in the memory hierarchy. Distributed shared address space machines that support cache coherence in hardware also typically use invalidation-based cache-coherence protocols (e.g. SGI Origin). On these machines, communication results in cache misses where the data must be fetched from the other processor's remote memory. On non-coherent distributed shared address space machines (e.g. Cray T3D/E) remote data is typically not cached, and all remote references result in accesses to another processor's memory.

On distributed address space machines, processors must send explicit messages to communicate data. The cost of communication is the time to send a message to the remote processor and for the receiving processor to process the message. Explicit communication through message-passing involves software and is much more expensive than implicit communication through cache-coherence hardware. For example, Table 1.1 shows the

typical remote memory latencies for a variety of machines with physically distributed memories. The first column lists the machines and the second column shows whether the machines have a shared or distributed address space. The third and fourth columns list the processors used at each node of the machine and the processor cycle times, respectively. The final column gives typical remote access times. For the shared address space machines, the value is the remote load latency; for the distributed address space machines, the value is the round-trip message time (for one word messages). For comparison, accesses that hit in the cache typically take one processor cycle. All the remote access time data is from [39], unless otherwise noted.

| Machine         | Address      |           | Processor  | Remote         |

|-----------------|--------------|-----------|------------|----------------|

|                 | Space        | Processor | Cycle Time | Access Time    |

|                 | Organization |           | (ns)       | (ns)           |

| SGI Origin[69]  | shared       | R10000    | 5.0        | 500 - 1100     |

| Cray T3E[66]    | shared       | 21164     | 3.3        | 1000 - 2000    |

| Convex Exemplar | shared       | PA8000    | 5.5        | 2000           |

| TMC CM-5        | distributed  | Sparc     | 30.0       | 10000          |

| Intel Paragon   | distributed  | i860      | 20.0       | 10000 - 30000  |

| IBM SP-2        | distributed  | RS6000    | 13.0       | 30000 - 100000 |

Table 1.1: Typical remote memory access times. For the shared address space machines, the value is the remote load latency; for the distributed address space machines, the value is the round-trip message time.

The long memory latencies mean that the amount of inter-processor communication in the program is a critical factor for performance. Thus it is important for computations to have good *temporal locality*. A computation has temporal locality if it re-uses much of the data it has been accessing; programs with high temporal locality tend to require less communication.

It is important to take communication and temporal locality into consideration when deciding how to parallelize a loop nest and how to assign the iterations to processors. Consider the code shown in Figure 1.1(a). This code is representative of the tomcatv benchmark from the SPEC92 and SPEC95 benchmark suites. While all the iterations in the first two-deep loop nest can run in parallel, only the inner loop of the second loop nest

```

real x[N,N], y[N,N], z[N,N]

for time = 1 to nsteps do

for i_2 = 1 to N do

/* doall */

for i_1 = 1 to N do /* doall */

x[i_1, i_2] = y[i_1, i_2] + z[i_1, i_2]

for i_2 = 2 to N-1 do

for i_1 = 1 to N do

/* doall */

x[i_1, i_2] = 0.333 * (x[i_1, i_2] + x[i_1, i_2-1] + x[i_1, i_2+1])

end for

(a)

Cache Lines

Processor

Number

0

1

P-1

(b)

(c)

```

Figure 1.1: An example to illustrate multiprocessor memory hierarchy issues: (a) sample code, (b) original data mapping and (c) optimized data mapping. The light grey arrows show the memory layout order.

is parallelizable (parallel loops are also known as *doall* loops and are annotated with the comment /\* *doall* \*/ in the figure). Consider what happens to the data access patterns when we distribute the parallel loops in this example. Assume that when a loop is distributed, each processor executes equal-sized blocks of consecutive iterations. If we distribute both parallel loops in the first loop nest, each processor accesses a two-dimensional block of array elements for each of the arrays. If we distribute the one parallel loop in the second loop nest, each processor accesses a block of rows for each array. There is communication between the two loop nests since the data accessed by each processor differs. However, we can eliminate the communication by distributing only the inner loop in the first loop nest. Now, each processor accesses the same data in both of the loop nests – a block of contiguous rows for each array. In this way, no inter-processor communication is necessary throughout the entire computation. Figure 1.1(b) shows the data accessed by each processor when only the inner parallel loops in both of the loop nests are distributed across the processors. The light grey arrows in the figure show the memory layout order.

#### 1.1.2 Multiprocessor Cache Effects

On multiprocessors that support a shared address space via cache coherence, it is not sufficient to just minimize the essential cache misses caused by communication. Due to characteristics found in typical data caches, multiprocessors also experience non-essential cache misses that can significantly hurt performance[28, 29].

In cache-coherent machines, the cache line size is the default coherence unit. When a processor performs a write, the entire cache line is invalidated in all other processor's caches. In today's machines, cache lines are typically 16 to 128 bytes long. A computation has *spatial locality* if it uses multiple words in a cache line before the line is displaced from the cache. While spatial locality is a consideration for both uni- and multiprocessors, *false sharing* is unique to multiprocessors. False sharing results when different processors use different data that happen to be co-located on the same cache line. Even if a processor re-uses a data item, the item may no longer be in the cache due to an intervening access by another processor to another word in the same cache line.

Assuming the FORTRAN convention that arrays are allocated in column-major order,

there is a significant amount of false sharing in the example from Figure 1.1(b). If the number of rows accessed by each processor is smaller than the number of array elements in a cache line, then every cache line is shared by at least two processors. Each time one of these lines is accessed, unwanted data are brought into the cache. Also, when one processor writes part of the cache line, that line is invalidated in the other processor's cache. This particular combination of computation mapping and data layout will result in poor cache performance.

Another problematic characteristic of data caches is that they typically have a small set-associativity; that is, each memory location can only be cached in a small number of cache locations. *Conflict misses* occur whenever different memory locations contend for the same cache location. Since each processor only operates on a subset of the data, the addresses accessed by each processor may be distributed throughout the shared address space.

Consider what happens to the example in Figure 1.1(b) if the arrays are of size  $256 \times 256$  and the target machine has a direct-mapped data cache of size 8 KB. Assuming that each element is 4 bytes, the elements in every 8th column will map to the same cache location and cause conflict misses. This problem exists even if the caches are set-associative, given that existing caches usually only have a small degree of associativity.

In general, the memory subsystem performance of multiprocessor code depends on how the computation is distributed as well as how the data are laid out. Instead of simply obeying the data layout convention used by the input language (e.g. column-major in FORTRAN and row-major in C), we can improve the cache performance by customizing the data layout for the specific program. Once we determine the data that each processor is going to access, we can further optimize multiprocessor cache performance by making the data accessed by each processor contiguous in the shared address space. Such a layout enhances spatial locality, minimizes false sharing and also minimizes conflict misses. Customizing the data layout benefits all cache-coherent machines, including both centralized and distributed shared address space systems. An optimized data layout that makes each processor's data contiguous for the example from Figure 1.1(b) is shown in Figure 1.1(c).

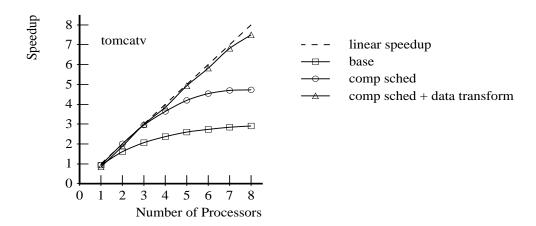

Figure 1.2 illustrates the impact of multiprocessor cache effects on program performance for the full tomcatv benchmark from the SPEC95 benchmark suite. The figure shows the

speedup over the best sequential version for three versions of the benchmark running on a centralized shared address space machine, an 8-processor 300 MHz Digital AlphaServer 8400. The curve labeled *base* shows the speedup obtained without any analysis to eliminate communication across loop nests. In this version of the program, we simply distribute iterations of the outermost parallel loop in each loop nest across the processors. The curve labeled *comp sched* corresponds to Figure 1.1(b), and shows the speedup when the computation is scheduled so as to eliminate communication across loop nests. Finally, the curved labeled *comp sched* + *data transform* shows the speedup obtained when the computation is scheduled to eliminate communication and the data layout is customized to make each processor's data contiguous. This last curve corresponds to Figure 1.1(c). Even though the *comp sched* program has essentially no communication, the performance is still quite poor due to poor spatial locality and false sharing. Only after the data has been transformed does the program achieve scalable performance. Whereas the speedup for the *base* program is only 2.9 on eight processors, the speedup for the *comp sched* + *data transform* version is 7.5.

Figure 1.2: Speedups for the SPEC95 benchmark tomcatv on the AlphaServer 8400.

9

#### 1.2 Problem Statement

To achieve good performance on parallel systems, programs must make effective use of the computer's memory hierarchy as well as its ability to perform computation in parallel. If we can co-locate the data with the processor that accesses the data, then we can minimize the problems specific to multiprocessor memory hierarchies. This means that we have to find a mapping of the data to the processors of the parallel machine, as well as a mapping of the computation to the processors of the machine. In this thesis we use the term *data decomposition* to refer to the data-to-processor mapping and the term *computation decomposition* to refer to the computation-to-processor mapping.

Selecting a good computation and data decomposition for a program is a difficult problem. First, there are many possible ways to assign the data and computation across the processors of the machine. The data decomposition may need to change dynamically as the program executes, for example, if different phases of the program operate on the data in different ways.

Second, the choices of data and computation decomposition are inter-related; it is important to examine both the opportunities for parallelism and the locality of data to determine the decompositions. For example, if the only available parallelism in a computation lies in operating on different elements of an array simultaneously, then allocating those elements to the same processor renders the parallelism unusable. The data decomposition dictated by the available parallelism in one loop nest affects the decision of how to parallelize the next loop nest, and how to distribute the computation to minimize communication.

Third, decomposition analysis must be performed across the entire program. It is not sufficient to just analyze one procedure at a time. If the data decompositions of the variables do not match across procedures, then the program could potentially incur large amounts of communication at every procedure call entry and call return.

A popular approach to the decomposition problem is to solicit the programmer's help in determining the data decompositions. A number of parallelizing compiler systems have been developed that rely on the user to specify the data-to-processor mapping using language extensions[21, 31, 49, 64, 74, 82]. The compiler then infers the computation mapping using the *owner-computes rule*[20, 64, 82]: the processor that is assigned a data element

performs all computation that writes that element. The High Performance FORTRAN (HPF) standard developed by a consortium of academic and commercial organizations also relies upon user-specified data decompositions[48]. These compiler systems are geared towards scientific codes and primarily target distributed address space machines. While the languages provide significant benefit to the programmer by eliminating the tedious job of managing the different address spaces explicitly, the programmer is still faced with a very difficult programming problem. The tight coupling between the mapping of data and computation means that the programmer must, in effect, also analyze the parallelization of the program when specifying the data decompositions. As the best decomposition may change based on the architecture of the machine, the programmer must fully master the machine details. Furthermore, the data decompositions may need to be modified to make the program run efficiently on a different architecture.

Parallelizing compilers for shared address space machines currently do not perform any decomposition analysis; they make no attempt to schedule computation that accesses the same data onto the same processor. These compilers start with a sequential program, but they only analyze one loop nest at a time and will typically always distribute the outermost parallel loop in a loop nest. Of course, the resulting programs still run correctly; however, they may not run as efficiently as possible due to communication, false sharing and poor spatial locality.

In short, current parallelizing compiler systems for distributed address space machines require programmers to perform the decomposition analysis themselves and to communicate that information to the compiler using language extensions. For shared address space machines, current parallelizing compilers do not implement decomposition analysis at all. A compiler that automatically finds the computation and data decompositions for a program relieves programmers from doing the complex analysis themselves and leads to more efficient code. The compiler can then take as input a sequential program – without language extensions for decompositions – and generate high-performance code for both distributed and shared address space machines.

11

#### 1.3 Thesis Overview and Contributions

The computation and data decomposition of a program is critical to performance on a wide variety of parallel machines. Yet, selecting a good decomposition for a program on a particular machine is a complex optimization problem. This thesis presents a compiler algorithm that automatically calculates computation and data decompositions for dense matrix computations that result in efficient, high-performance code. The contributions of this thesis are as follows:

**Decomposition Framework.** We have developed a linear algebra framework for expressing and calculating decompositions. We model decompositions in two steps: first an affine function<sup>1</sup> maps the computation and data onto a virtual processor space, and second a folding function maps the virtual processor space onto the physical processors of the target machine. Using this framework, our algorithm generates a system of equations that specifies the conditions that the desired decompositions must satisfy. We then calculate the decompositions systematically by solving the systems of equations. Our mathematical model allows a rich set of target decompositions and is not limited to an arbitrary set of possible decompositions.

**Decomposition Algorithm.** Our compiler algorithm for finding decompositions is the first complete algorithm based on a linear algebra framework. Our decomposition algorithm operates by partitioning the program into regions that have the same data assignment for all the computation in the region. Within each region, we use the mathematical model to generate a system of equations that describes the decompositions. Communication occurs across regions as the data must be reorganized. The regions are found incrementally by gathering constraints on the data and computation that must be assigned to the same processor in order for a solution to exist to the set of equations. The constraints are gathered starting with the most frequently executed loops in the program. This approach builds regions of the program that have no data reorganization that are as large as possible, and places any necessary communication in the least executed sections of the code. Within

<sup>&</sup>lt;sup>1</sup>An affine function is a linear function plus a constant offset.

the regions, the decompositions we find are optimal in that they are guaranteed to have the largest degree of parallelism with no data reorganization. The algorithm also handles replication of data and explicit synchronization within loop nests.

Our decomposition algorithm has several key features. It is the first algorithm that calculates decompositions directly while simultaneously modeling the benefits of parallelization and the cost of communication. It allows data to be reorganized, if necessary, to benefit the overall execution time of the program. Our algorithm finds decompositions incrementally, and as a result it scales to handle complete programs. Finally, our algorithm also incorporates replication and synchronization which are often needed to generate good code for realistic programs.

Interprocedural Decompositions. Our decomposition algorithm is the first to analyze both within and across procedure boundaries so that consistent decompositions can be found throughout the entire program. The interprocedural decomposition algorithm visits each procedure twice, once in a bottom-up traversal of the call graph and once in a top-down traversal of the call graph. The bottom-up pass uses the base decomposition algorithm to incrementally gather constraints on the decompositions and the top-down pass records the final decompositions at each procedure. Our mathematical representation of decompositions, coupled with the incremental solving method, allows us to succinctly summarize all the necessary information on decompositions within a procedure. Thus when the algorithm analyzes a procedure, it does not have to re-solve for the decompositions for any procedures that are called by the current procedure.

**Implementation and Evaluation.** The algorithms described in this thesis have all been implemented as part of the SUIF parallelizing compiler system[76]. To evaluate the effectiveness of our proposed algorithm, we applied the compiler to a suite of benchmark programs. We ran the compiler-generated code on the Stanford DASH multiprocessor[55] and a Digital AlphaServer 8400, and present a comprehensive study of the resulting performance. Our experiments show that on both of these machines, our decomposition analysis and optimization improves program performance by as much as a factor of four.

13

### 1.4 Thesis Organization

In this thesis we describe our model and algorithm for finding computation and data decompositions. We evaluate the effectiveness of the algorithm by looking at the performance achieved by the compiler-optimized code. We begin in Chapter 2 by describing how the decomposition analysis fits into the context of a complete parallelizing compiler system. We also show that once the decompositions are calculated, the compilation techniques needed for both shared and distributed address space machines are similar. Chapter 3 describes our assumptions about the target architectures and presents the mathematical framework we use to represent decompositions. Chapters 4 and 5 present the details of the intraprocedural decomposition algorithm. In Chapter 6 we then describe the interprocedural version of the decomposition algorithm. In Chapter 7 we compare the performance of the optimized code against un-optimized code and analyze the results. We conclude in Chapter 8 by summarizing the contributions of this thesis.

## Chapter 2

# **Compiler Overview**

A parallelizing compiler takes a sequential program as input and automatically translates it into parallel code for the target machine. In this chapter we describe how the decomposition analysis described in this thesis fits into the context of a complete parallelizing compiler system. We found that there are many similarities in the compiler techniques needed for both shared and distributed address space machines. This led us to design a unified compiler framework for both kinds of architectures.

Our implementation platform is the SUIF compiler system[76]. The SUIF compiler takes as input sequential FORTRAN-77 or C programs. The source programs are first translated into the SUIF compiler's intermediate representation. All program analysis and optimization passes operate on the SUIF representation. The optimized and parallelized SUIF program is then converted into a combination of C and/or FORTRAN and is compiled by the native compiler on the target machine. The SUIF output contains calls to a portable run-time library, which is linked in by the native compiler.

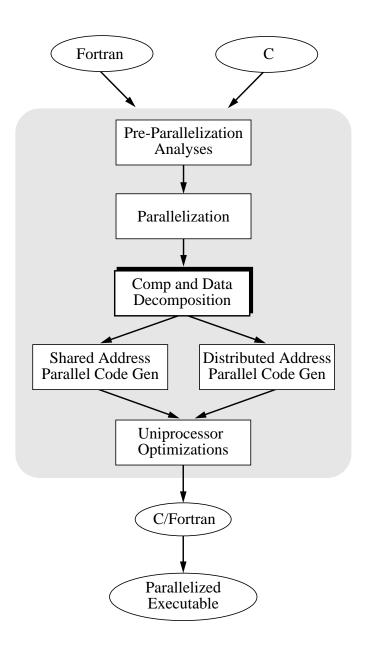

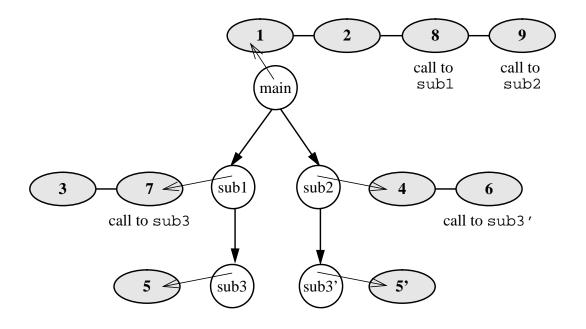

The design of a complete compiler framework that incorporates decomposition analysis is shown in Figure 2.1. The compiler first runs pre-parallelization analyses to gather information needed by the subsequent passes. The parallelization phase transforms the code to find the maximum degree of loop-level parallelism, and these loops are then passed on to the decomposition phase. The computation and data decompositions are used to generate parallel code for both distributed and shared address space machines. Finally, the compiler further optimizes the uniprocessor code that runs on each individual processor. In

Figure 2.1: The design of a parallelizing compiler system for both shared and distributed address space machines.

the remainder of this chapter, we first define the scope of input programs that are amenable to automatic parallelization and decomposition analysis. We then discuss the key compiler phases in more detail, with an emphasis on how the decomposition analysis interfaces with each of the phases.

### 2.1 Domain of Applications

Scientific codes are currently the most common domain for parallelizing compilers. These programs tend to make heavy use of loops to operate over array data structures. Loops can be parallelized by executing different iterations concurrently. In order to parallelize a loop, the parallel version must have the same semantics as the original sequential version. This condition imposes ordering constraints among the iterations in a loop nest. If two iterations may access the same memory location, and at least one of the accesses is a write, then it can change the semantics to reorder the iterations. Thus there is an ordering constraint, or *data dependence*, between the iterations and they must execute in the original serial order. This analysis is called data dependence analysis and is based on integer programming theory[14, 59, 62]. A loop can execute in parallel if and only if there are no data dependences carried by that loop. Data dependence analysis, and thus automatic parallelization, is typically restricted to the domain of affine functions. Specifically, we analyze loop nests of the following general form (the compiler normalizes the step sizes to 1[5]):

```

for i_1 = L_1 to U_1 do \times [f_1(i_1), f_2(i_1), \dots, f_m(i_1)] = \dots for i_2 = L_2(i_1) to U_2(i_1) do \times [f_1'(i_1, i_2), f_2'(i_1, i_2), \dots, f_m'(i_1, i_2)] = \dots ...

for i_l = L_l(i_1, \dots, i_{l-1}) to U_l(i_1, \dots, i_{l-1}) do \times [f_1''(\vec{\imath}), f_2''(\vec{\imath}), \dots, f_m''(\vec{\imath})] = \dots end for ...

end for end for

```

In this loop nest format,  $L_1 ldots L_l$  are affine functions that compute the lower bound of each loop, and  $U_1 ldots U_l$  are affine functions that compute the upper bounds. The access functions for each dimension of the arrays,  $f_1 ldots f_m$ ,  $f_1' ldots f_m'$  and  $f_1'' ldots f_m''$  are also affine functions. In all cases, the loop bounds and array accesses are affine functions of outer nested loop indices and symbolic constants.

### 2.2 Pre-Parallelization Analyses

The compiler runs pre-parallelization symbolic analyses to extract information necessary for subsequent parallelization and optimization passes. These analyses include scalar variable analyses such as constant propagation, induction variable identification and forward propagation, as well as reduction recognition on scalar and array variables.

At this point, it is also desirable for the compiler to transform the code so that each loop nest has as few array accesses as possible. Having fewer array accesses per loop nest reduces the likelihood that the accesses will cause conflicting requirements on the computation decomposition for the loop nest. The *loop fission* transformation can be used to split a single loop into multiple loops that have the smallest number of statements possible. Each of the new loops has the same loop bounds as the original, but contains a subset of the statements[11, 51]. After the decomposition analysis, *loop fusion* can be used to regroup compatible loop nests[19]. Loop fission and loop fusion are not currently implemented in the SUIF compiler.

### 2.3 Parallelization Analysis

The parallelization analysis transforms the code using unimodular transformations to expose the maximum degree of loop-level parallelism, while minimizing the frequency of synchronization. It tries to generate the *coarsest granularity* of parallelism by placing the largest degree of parallelism in the outermost positions of the loop nest. Since no synchronization is needed between iterations of a parallel loop, pushing the parallel loops outermost reduces the frequency of synchronization. Algorithms for analyzing and maximizing parallelism within a loop nest have been well-studied, for example see [5, 77, 79, 80, 83]. The

following two subsections describe the interface between the parallelization analysis and the decomposition analysis in more detail.

#### 2.3.1 Choices of Parallelism

The SUIF compiler uses the algorithm developed by Wolf and Lam[77, 79] to put the loop nests in a canonical form consisting of a nest of the largest possible *fully permutable* loop nests. A loop nest is fully permutable if any arbitrary permutation of the loops within the nest is legal. A fully permutable loop nest of depth l has the property that it can always be transformed to make l-1 degrees of parallelism, that is, l-1 parallel loops[43, 79]. In the special case where the loop nest has no loop-carried dependences, it has l degrees of parallelism.

The compiler transforms the code to create the largest possible fully permutable nests, starting from the outermost loops. This form exposes the maximum degree of parallelism within the loop nest[77]. The compiler also marks those loops in the nest that are *doall* loops and moves them to the outermost possible position within each fully permutable nest. A *doall* loop is simply a parallel loop and can thus execute in parallel with no synchronization. The maximum degree of parallelism for the entire loop nest is the sum of the degree of parallelism contained in each of the fully permutable subnests.

In a fully permutable loop nest of depth l, the l-1 degrees of parallelism can be exploited in many ways. One possibility is to transform the code to have l-1 doall loops[77], and then distribute iterations of the doall loops across the processors. However, it is also possible to distribute iterations of a loop with loop-carried dependences. In this case, explicit synchronization and communication are required to enforce the dependences within the computation of the loop. Loops that are distributed across processors, but require explicit synchronization between iterations, are called doacross loops. Opportunities for exploiting parallelism with doacross loops occur when a fully permutable loop nest contains at least two loops (if there is only a single loop then the synchronization between iterations makes the loop run sequentially and there is no parallelism). To illustrate the different kinds of parallelism that are available within fully permutable loop nests, consider the following example representative of an ADI (Alternating Direction Implicit) integration:

```

real x[N,N]

/* Loop nest 1 */

for i_1 = 1 to N do /* doall */

for i_2 = 2 to N do

x[i_1,i_2] = f_1(x[i_1,i_2], x[i_1,i_2-1])

/* Loop nest 2 */

for i_1 = 1 to N do /* doall */

for i_2 = 2 to N do

x[i_2,i_1] = f_2(x[i_2,i_1], x[i_2-1,i_1])

```

The outer loops are *doall* loops and both loop nests are fully permutable. When iterations of the *doall* loops are run in parallel, neither communication nor synchronization is required within each of the loop nests.

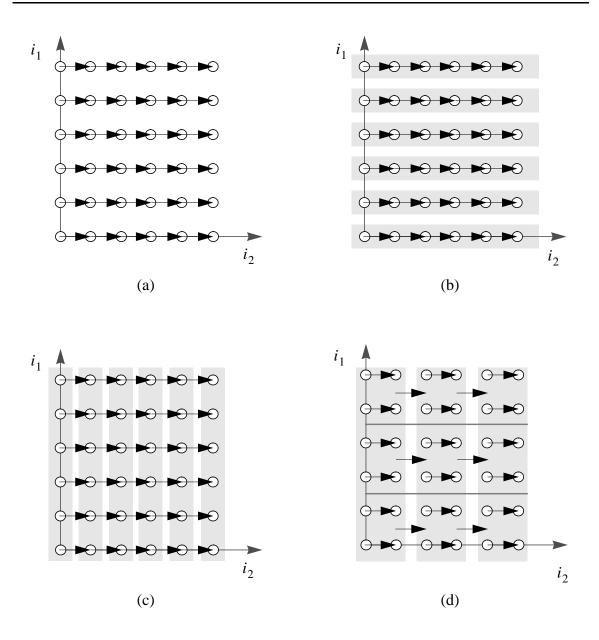

Figure 2.2(a) shows the original *iteration space* for the loop nests. In the figure, the vertical axis corresponds to the outer  $i_1$  loop, the horizontal axis corresponds to the inner  $i_2$  loop and each node represents one iteration in the loop nest. The arrows represent the data dependences between the iterations; the data dependences show the ordering constraints among the nodes that are required to guarantee the same semantics as the original sequential version. The figure applies to both loop nests 1 and 2 since they have the same iteration space. Figure 2.2(b) shows the parallel execution of loop  $i_1$  for both loop nests. The shaded regions in the figure show iterations that are assigned to the same processor. Since the iterations that are ordered by data dependences all execute sequentially on the same processor, no synchronization is needed within the loop nest.

In addition to the *doall* parallelism in the ADI example, *doacross* parallelism is also available in both loop nests. Figure 2.2(c) shows the parallel execution of the  $i_2$  loop using *doacross* parallelism. Let  $i_1'$  be an iteration of the  $i_1$  loop, and let  $i_2'$  be an iteration of the  $i_2$  loop. If processor p executes  $i_2 = i_2'$  and processor p + 1 executes  $i_2 = i_2' + 1$ , then p must communicate all the array elements it writes to p + 1. Synchronization is needed because processor p + 1 cannot execute iteration  $(i_1, i_2) = (i_1', i_2' + 1)$  until p has executed iteration  $(i_1, i_2) = (i_1', i_2')$ . Parallelism is available along a diagonal or wavefront in the

Figure 2.2: (a) Original iteration space for the loop nests in the ADI example. (b)–(d) Iteration spaces showing different ways to execute the loop nests in parallel. The arrows represent data dependences, and the iterations in each shaded region are assigned to the same processor.

iteration space, i.e. p can execute iteration  $(i_1, i_2) = (i_1' + 1, i_2')$ , while p + 1 executes  $(i_1, i_2) = (i_1', i_2' + 1)$ .

Another way to look at the parallelism in this example is to say that in Figure 2.2(b) we allocated iterations along the direction (0,1) to each processor, that is, all pairs of iterations that differ by (0,1) are assigned to the same processor. In Figure 2.2(c) we allocated iterations along the direction (1,0) to each processor. In fact, it is possible to exploit parallelism by allocating to each processor iterations along any direction within the two axes.

When using *doacross* parallelism, it is not very efficient to synchronize and communicate for every iteration of the loop. A general technique that is used to reduce the synchronization frequency and communication volume of parallel loops is *loop blocking* [78, 80] (also known as tiling, unroll-and-jam and stripmine-and-interchange). Blocking transforms a loop nest of depth l into a loop nest of depth 2l. The inner l loops iterate over a fixed number of iterations (given by the block size), while the outer loops iterate across the inner blocks of iterations.

By blocking and then only parallelizing the outer loops, the synchronization frequency is reduced by the size of the block. The reduction in communication volume from blocking is a function of the loop's data dependences. Two array accesses are dependent within a loop i if there is a data dependent pair of iterations i' and i''. The references are said to be dependent with  $distance\ d_i=i'-i''$ . If the array accesses in a loop have small, finite dependence distances such that  $0 \le d_i < b$ , where b is the block size, then only  $d_i$  elements at each block boundary need to move.

Fully permutable loop nests have several properties that are important for efficiently exploiting *doacross* parallelism. First, the fact that the loop nests are fully permutable means that *doacross* parallelism is legal, and the loop nest can be completely blocked[43, 77]. Also, for a fully permutable loop nest of depth l, when the dependences are distances then we know that  $d_i \geq 0$  for all loops  $i = 1 \dots l$ [77]. The result of this is that *doacross* parallelism and blocking can be applied along any dimension in the iteration space of such fully permutable loop nests.

Since the compiler first transforms the loop nests into the canonical form of nests of fully permutable subnests, the blocking transformation is easily applied. Figure 2.2(d)

shows the parallel execution of the  $i_2$  loop from the on-going ADI example using *doacross* parallelism and blocking.

#### 2.3.2 Global Considerations

If we look at each loop nest individually, then distributing the iterations in the direction of the *doall* loops is preferable, as neither communication nor synchronization is necessary within the loop. However, this is not always the case when we analyze multiple loop nests together. Going back to the ADI example, consider what happens if we only try to exploit the parallelism in the *doall* loops. The *doall* loop in the first loop nest accesses rows of array x, whereas iterations of the *doall* loop in the second loop nest accesses columns of array x. Communication will occur between the loop nests because the data must be completely reorganized as the data decomposition switches between rows and columns.

We can avoid reorganizing the arrays between the two loop nests in the ADI example by using *doacross* parallelism in one of the loop nests. For example, in the second loop nest the loop with the loop-carried dependence (the  $i_2$  loop), accesses rows of the array. If iterations of this loop are distributed across the processors, then in both loop nests processors access rows of the arrays. Communication and synchronization are now required within the second loop nest. However, since we use loop blocking to reduce the communication volume and synchronization frequency, the overhead incurred within the one loop nest is typically much less than the overhead to reorganize the data between the loop nests.

As this example illustrates, only exploiting the parallelism in the *doall* loops may not result in the best overall performance. In general, there may be tradeoffs between the best *local* loop-level decompositions, and the best overall *global* decompositions. Thus the loop-level analysis in our compiler transforms the code to expose the maximum degree of loop-level parallelism, but does not make decisions as to how that parallelism is to be implemented. The loop-level analysis leaves the code in a canonical format of nests of fully permutable loop nests, from which the coarsest degree of parallelism can be easily derived.

# 2.4 Decomposition Analysis Overview

The decomposition analysis takes as input the loop nests in the canonical form of nests of fully permutable loop nests. It analyzes the array accesses within the loop nest to calculate the mappings of data and computation onto the processors of the target machine. For each loop nest and for each array accessed in each loop nest, the decomposition analysis outputs a system of linear inequalities that describes the processor mappings.

The decomposition analysis only examines affine array accesses, and any non-affine accesses are ignored. All affine array access within a loop nest are examined, regardless of control-flow within the loop nest. Any non-perfectly nested accesses are treated as if they were perfectly nested, but with conditional guards (this is the model used by the SUIF compiler's parallelization analysis[77]). For example, for the following generalized two-deep loop nest with non-perfectly nested accesses:

```

for i_1 = L_1 to U_1 do x[f_1(i_1)] = \dots for i_2 = L_2(i_1) to U_2(i_1) do y[f_1'(i_1,i_2),f_2'(i_1,i_2)] = \dots end for z[f_1''(i_1)] = \dots end for

```

The compiler models the code as:

```

for i_1 = L_1 to U_1 do

for i_2 = L_2(i_1) to U_2(i_1) do

if i_2 = L_2(i_1) then \mathbf{x}[f_1(i_1)] = \dots

\mathbf{y}[f_1'(i_1,i_2),f_2'(i_1,i_2)] = \dots

if i_2 = U_2(i_1) then \mathbf{z}[f_1''(i_1)] = \dots

end for

end for

```

Of course, this model is only legal if and only if the innermost  $i_2$  loop in the original code executes at least one iteration whenever the outermost  $i_1$  loop does. If we cannot prove this

condition statically, then we must insert explicit checks. Since the decomposition analysis does not take control-flow within the body each loop nest into account, it ignores the guards and treats the non-perfectly nested accesses as if they were perfectly nested.

# 2.5 Parallel Code Generation and Optimization

The parallel code generator takes as input the linear inequalities representing the computation and data decompositions, and emits SPMD (single-program, multiple-data) parallelized code. The generated code is parameterized by the number of processors; each processor gets the total number of processors and its own processor identifier from calls to the runtime library. In this section, we describe parallel code generation for both distributed address space machines and shared address space machines. In the current SUIF compiler, only shared address space code generation is supported. Here we discuss the necessary steps to generate parallel code for both types of machines to show how the decomposition information is used, and to underscore the similarities between the techniques.

## 2.5.1 Distributed Address Space Machines

A parallel code generator for distributed address space machines is responsible for the following three main tasks:

- 1. Distribute the computation according to the computation decomposition. The bounds of the distributed loops are generated by applying a series of projection transformations to the polyhedron represented by the computation decomposition's system of linear inequalities[7, 8]. The resulting loop bounds are parameterized by the processor identifier so that each processor executes only the iterations that it has been assigned.

- 2. Allocate memory locally in each processor's address space for its portion of the distributed arrays. The global array addresses in the original program are then translated into local addresses. Each processor's portion of the arrays is given by the data decomposition.

3. Generate communication code (i.e. send and receive messages) whenever a processor accesses remote data. The decompositions are used to identify accesses to non-local elements. The data and computation decompositions, along with the array accesses, are composed into a single system of linear inequalities. The projection transformation is applied to the resulting system of inequalities to calculate the non-local accesses and the identity of the sending and receiving processors[7].

#### 2.5.2 Shared Address Space Machines

When using decomposition information, the parallel code generator for shared address space machines is similar to the parallel code generator for distributed address space machines. It also performs three main tasks, described below. The items listed as *optional* are strictly optimizations and are not required for generating a correct parallel program.

- 1. Schedule the computation according to the computation decomposition. This step is performed in exactly the same way as for distributed address space machines, described in Step 1 of Section 2.5.1.

- (optional) Make each processor's data contiguous in the shared address space. This

improves the spatial locality of the application and eliminates cache conflicts and

false sharing. The compiler manages the data placement both within a single array

and across multiple arrays.

To make the data of a single array accessed by each processor contiguous, the compiler transforms the data layout of the array in the virtual address space, and translates the array addresses in the original program into new addresses[9]. The data each processor accesses for each array is given by the array's data decomposition. These data transformations are analogous to global to local address translation for distributed address space machines, described in Step 2 of Section 2.5.1.

To make the data across multiple arrays contiguous, we developed a technique called *compiler-directed page coloring*[18]. The operating system's page mapping policy determines the location of memory pages in physically indexed caches (external caches for most current processors are physically indexed). The compiler supplies

the data decompositions of all the arrays to a run-time library. The run-time library then uses that information to direct the operating system's page allocation policy into making each processor's data contiguous in the physical address space. The operating system uses these hints to determine the virtual-to-physical page mapping when the pages are allocated.

3. (*optional*) Eliminate unnecessary synchronization. On shared address space machines, communication is performed by the hardware and explicit communication code (as described in Step 3 of Section 2.5.1) is unnecessary. Although communication analysis to identify accesses to non-local data is not required to ensure correctness, the same analysis can be used to optimize synchronization. Without any optimization, synchronization is implemented by inserting barriers at the end of each parallel loop to prevent potential data races. These barriers, however, cause overhead and can inhibit parallelism. By using the computation and data decompositions to identify exactly when and where accesses to non-local data occur, the compiler can eliminate unnecessary barrier synchronization or replace them with efficient point-to-point synchronization[73].

# 2.6 Uniprocessor Locality Optimizations

After generating the SPMD parallelized code, the compiler further optimizes the code that runs on each of the individual processors. In particular, the compiler optimizes for the memory hierarchy in a single processor. The parallelization and decomposition analysis are run before the uniprocessor locality optimizations because interprocessor communication is the most expensive form of data movement in the memory hierarchy and minimizing such communication is the most critical locality optimization.

The compiler's uniprocessor data locality optimizing algorithm uses the same loop transformation framework as the parallelization analysis [77, 78]. We apply the uniprocessor locality algorithm to the subnest consisting of the distributed parallel loops and their inner loops. The original loop structure differs from this subnest by having additional sequential loops outside the parallel loops. Since these sequential loops must be placed outermost due

2.7. SUMMARY

to legality reasons, the uniprocessor data locality is not compromised by parallelization.

Finally, to avoid a common source of cache conflicts in the on-chip cache, the compiler inserts padding between arrays in the virtual processor space[11]. This causes the starting addresses of the arrays to map to different locations in the cache.

# 2.7 Summary

This chapter described the context of the decomposition analysis within a complete parallelizing compiler system. The current domain of parallelizing compilers is scientific codes; in particular, when calculating computation and data decompositions, we only analyze loop bounds and array accesses that are affine functions of outer nested loop indices and symbolic constants.

The decomposition analysis relies on a pre-pass to optimize the parallelism within each individual loop nest. The parallelization analysis pre-pass puts the loop nests in a canonical form consisting of a nest of the largest possible fully permutable loop nests. This format exposes the maximum degree of loop-level parallelism, but does not constrain how the parallelism is to be implemented.

Once the computation and data decompositions are calculated, the parallel code generator uses the decompositions to create SPMD parallelized code. The transformations needed to generate optimized code for both shared and distributed address space machines are very similar. A unified compiler framework can thus be used for both kinds of architectures.

# Chapter 3

# Computation and Data Decomposition Basics

Decomposition analysis maps a program's computation and data onto the processors of a target machine. This chapter lays the foundation for the decomposition algorithm by describing our parallel architecture model, and by defining our representation of computation and data decompositions. In Section 3.1 we present the basic machine model that our decomposition algorithm targets. There are many different parallel architectures, and it is important to understand how the choice of machine model impacts the quality of the resulting decompositions. We also categorize the types of communication based on the data movement patterns, and discuss the communication costs on the target machine. Then in Section 3.2 we describe the mathematical framework we have developed for representing and calculating decompositions. We also discuss the key properties of the mathematical decomposition model that are fundamental to the decomposition algorithm.

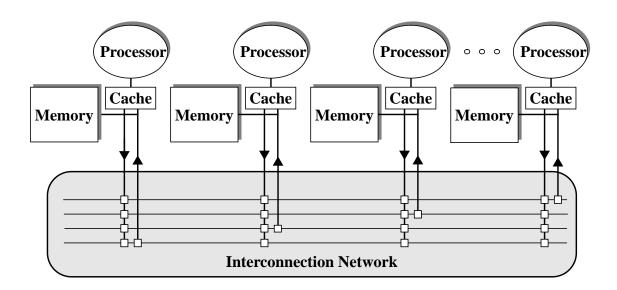

## 3.1 Machine and Communication Models

The decomposition analysis models a machine with physically distributed memories, and each memory is associated with one processor. This architecture is shown in Figure 3.1. The decompositions calculated by the compiler map the computation onto the processors, and map the data onto the local memories associated with the processors. The decomposition

analysis always models a separate memory for each processor, despite the fact that multiple processors may actually share memory on the true target machine. For example, this is the case for centralized shared address space machines, or for machines where each node is itself a centralized shared address space machine (e.g. Stanford DASH, SGI Origin). Regardless of the memory configuration of the true target machine, the fundamental problems we are solving are how to allocate the computation so as to minimize communication while maintaining sufficient parallelism, and how to allocate the data for good memory hierarchy performance. By targeting a machine with separate memories for each processor, we calculate decompositions such that each individual processor accesses the same data as much as possible. The resulting computation decompositions thus minimize inter-processor communication, independent of the memory architecture. The resulting data decompositions specify exactly which data are accessed by each individual processor. This information is then used to tailor the data allocation for the specific target architectures. For example, as described in Section 2.5.2, on shared address space machines the parallel code generator uses the data decompositions to transform the data layout so that each processor's data are contiguous in the shared address space.

Figure 3.1: Basic machine model used by the decomposition analysis.

The interconnection network of the target machine is a key factor in determining the cost of communication. There are many different network topologies that can be used to build the interconnection network for parallel architectures. We model a fully-connected interconnection network, where all processors are directly connected to one another. Examples of fully-connected networks include crossbars and buses. The decomposition analysis assumes that the communication time between any two processors is the same, regardless of the specific processors involved. Thus, the main factor in determining the cost to access a data element is whether that access is to the local processor or to a remote processor. Hot-spotting effects can cause the communication time to a particular processor to become disproportionately large, making the communication costs between different pairs of processors non-uniform. In this case, the remote access times continue to dominate the local access times, and the decomposition analysis will still optimize to eliminate the remote accesses. In general, our communication model is reasonable for most parallel machines today, since the ratio of local access time to remote access time is typically much greater than the ratio of the maximum remote access time to the minimum remote access time. The decomposition analysis models local accesses as having zero cost and models all remote accesses as having equal cost. As a result, the communication costs calculated by the decomposition algorithm are directly proportional to the amount of data accessed by remote processors.

The communication patterns in applications determine the amount of data that is being moved. We make the distinction between two communication patterns, *nearest-neighbor communication* and *data-reorganization communication*. When the communication pattern is nearest-neighbor shifts of data, then the amount of data transferred can be significantly reduced by assigning blocks of contiguous iterations of a distributed loop to the same processor. In this way, any nearest-neighbor communication between the iterations in the same block is eliminated. We describe our use of blocking for reducing the cost of nearest-neighbor communication in more detail in Section 4.2. Data-reorganization communication is unstructured and requires general movement of the entire data structure, for example, transposing a distributed array. We thus consider nearest-neighbor communication to be inexpensive compared to data-reorganization communication.

31

# 3.2 Mathematical Decomposition Model