## **LOW-POWER PROCESSOR DESIGN**

Ricardo E. Gonzalez

**Technical Report No. CSL-TR-97-726**

**June 1997**

#### LOW-POWER PROCESSOR DESIGN

#### Ricardo E. Gonzalez

**Technical Report: CSL-TR-97-726**

June 1997

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

William Gates Computer Science Building, A-408

Stanford, Ca 94305-9040

<pubs@shasta.stanford.edu>

#### **Abstract**

Power has become an important aspect in the design of general purpose processors. This thesis explores how design tradeoffs affect the power and performance of the processor. Scaling the technology is an attractive way to improve the energy efficiency of the processor. In a scaled technology a processor would dissipate less power for the same performance or higher performance for the same power. Some microarchitectural changes, such as pipelining and caching, can significantly improve efficiency. Unfortunately many other architectural tradeoffs leave efficiency unchanged. This is because a large fraction of the energy is dissipated in essential functions and is unaffected by the internal organization of the processor.

Another attractive technique for reducing power dissipation is scaling the supply and threshold voltages. Unfortunately this makes the processor more sensitive to variations in process and operating conditions. Design margins must increase to guarantee operation, which reduces the efficiency of the processor. One way to shrink these design margins is to use feedback control to regulate the supply and threshold voltages thus reducing the design margins. Adaptive techniques can also be used to dynamically trade excess performance for lower power. This results in lower average power and therefore longer battery life. Improvements are limited, however, by the energy dissipation of the rest of the system.

**<u>Key Words and Phrases:</u>** processor design, processor architecture, low-power CMOS circuits, supply and threshold scaling.

Copyright © 1997

by

Ricardo E. Gonzalez

# Acknowledgments

I would never have completed this document without the support, encouragement and guidance of many people. I cannot possibly list everyone that helped make my stay at Stanford a fulfilling experience; I will mention just a few.

First and foremost I would like to thank Mark Horowitz, my principal advisor, for his support, guidance, and encouragement. Working with him for 7 years was a privilege. His ability to understand my ideas before I did and his continuous pursuit of knowledge were always a source of inspiration.

I would also like to thank Kunle Olukotun and Simon Wong for their support an guidance as members of my reading committee. I am also thankful to Bruce Wooley and Arogyaswami Paulraj for participating in my oral examination committee. Noe Lozano did much to convince me to pursue a Ph.D. and arranged the financial support for me to get started.

My family also gave their unwavering support to this enterprise. My parents never stopped asking how my research was progressing. And, more important, never accepted "It's going OK" for an answer. This dissertation is dedicated to them.

My friends and colleagues made my life at Stanford very enjoyable. This document now before you is due to them. They encouraged me, helped me spend time away from my workstation, and were an unending source of interesting conversations.

Finally, I would like to thank all the members of the Stanford Cycling Club especially our coach, Art Walker, for making the past few years of my life so painfully memorable.

This research was supported in part by the Advanced Research Projects Agency under contract J-FBI-92-194. by the School of Engineering at Stanford, and by the Intel Foundation.

To my parents.

# **Table of Contents**

| Chapter 1 | Introduction                                     | 1  |

|-----------|--------------------------------------------------|----|

| Chapter 2 | Energy-Delay Product                             | 5  |

| 2.1 I     | Energy Dissipation in CMOS Circuits              | 5  |

|           | Low-Power Metrics                                |    |

| 2.3 I     | Low-Power Design Techniques                      | 9  |

| Chapter 3 | Micro-architectural Tradeoffs                    | 19 |

| 3.1 L     | ower Bound on Energy and Energy-Delay            | 19 |

| 3.1       | .1 Simulation Methodology                        | 20 |

| 3.1       | .2 Machine Models                                | 22 |

| 3.1       | .3 Comparison of Energy and Energy-Delay Product | 23 |

| 3.2 I     | Processor Energy-Delay Product                   | 24 |

| 3.2       | .1 Simulation Methodology                        | 25 |

| 3.2       | .2 Machine Models                                | 25 |

| 3.2       | .3 Energy Optimizations                          | 26 |

| 3.2       | .4 Energy and Energy-Delay Results               | 29 |

| 3.3 I     | Energy Breakdown                                 |    |

| 3.4 I     | Memory Hierarchy Design                          | 32 |

| 3.4       | .1 System architecture                           | 32 |

| 3.4       | .2 Simulation Methodology                        | 33 |

| 3.4       | .3 Energy and Performance Tradeoffs              | 35 |

| 3.5 I     | Future Directions                                | 41 |

| 3.6       | Summary                                          | 47 |

| Chapter 4 | Supply and Threshold Scaling                     | 49 |

| 4.1 I     | Energy and Delay Model                           | 49 |

|           | Sleep Mode                                       |    |

| 4.3 I     | Process and Operating Point Variations           | 60 |

|           | Adaptive Techniques                              |    |

|           | Adaptive Power Management                        |    |

|           | Summary                                          |    |

| Chapter 5 | Conclusions                                      | 73 |

| 5 1 I     | Future Work                                      | 74 |

| Chapter 6 Bibliography            | 77 |

|-----------------------------------|----|

| Appendix A Capacitance Estimation | 85 |

| Appendix B Memory Power Model     | 87 |

# **List of Tables**

| Table 2.1: | Current processors.                                    | 17 |

|------------|--------------------------------------------------------|----|

| Table 3.1: | Summary of SRAM characteristics.                       | 34 |

| Table 3.2: | Summary of DRAM characteristics                        | 34 |

| Table 4.1: | Circuit element description.                           | 52 |

| Table 4.2: | Process and circuit parameters for a 0.25µm technology | 54 |

| Table 4.3: | Additional process parameters for 0.25µm technology    | 59 |

| Table 4.4: | Operating modes.                                       | 71 |

| Table 4.5: | Power breakdown categories.                            |    |

| Table B.1  | Cache model parameters                                 |    |

# **List of Figures**

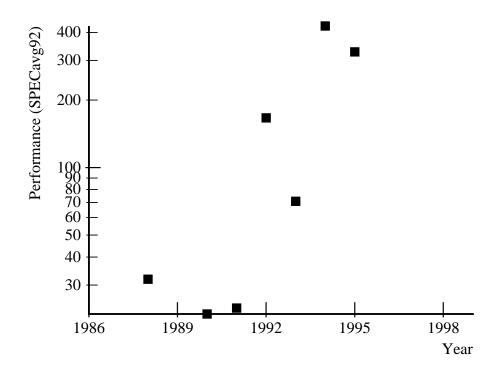

| Figure 1.1:  | Evolution of processor performance.                               | 2  |

|--------------|-------------------------------------------------------------------|----|

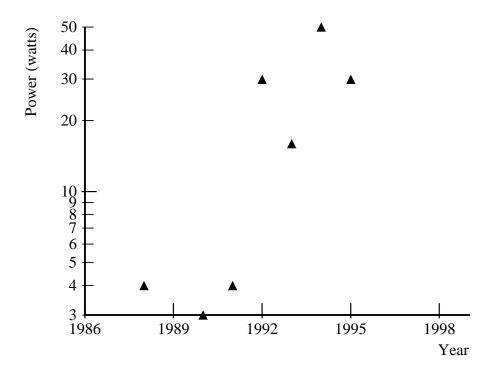

| Figure 1.2:  | Evolution of processor power.                                     | 2  |

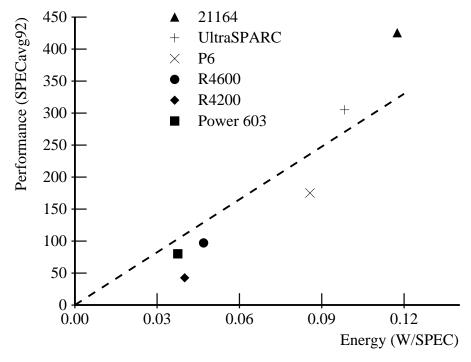

| Figure 1.3:  | Performance and energy of processors.                             | 3  |

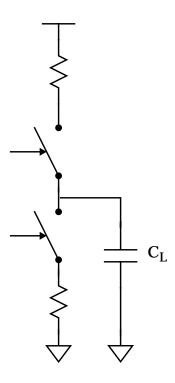

| Figure 2.1:  | CMOS inverter.                                                    | 6  |

| Figure 2.2:  | Performance-energy plane.                                         | 9  |

| Figure 2.3:  | Variation in performance and energy with supply voltage           | 10 |

| Figure 2.4:  | Variation in performance and energy with transistor sizing        | 11 |

| Figure 2.5:  | EDP contours versus transistor size and supply voltage            | 13 |

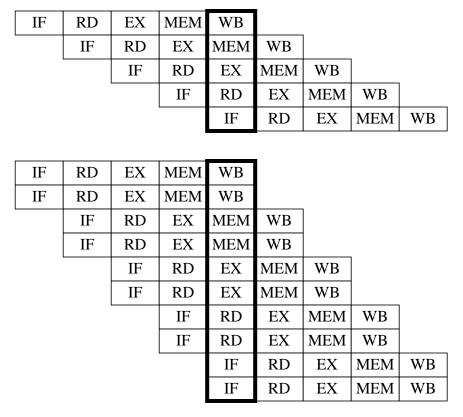

| Figure 2.6:  | Scalar and super-scalar processors pipeline diagrams              | 16 |

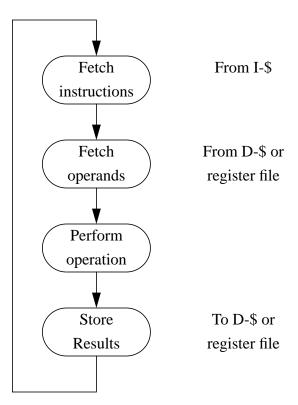

| Figure 3.1:  | Basic processor operation.                                        | 21 |

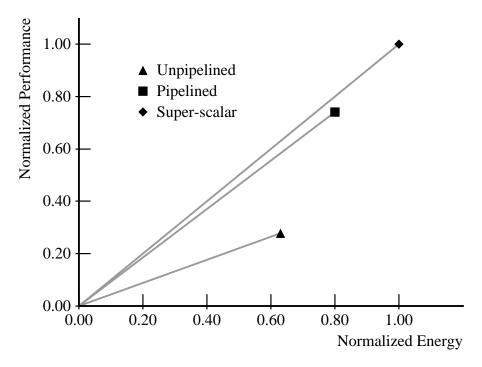

| Figure 3.2:  | Normalized performance and energy of idealized machines           | 24 |

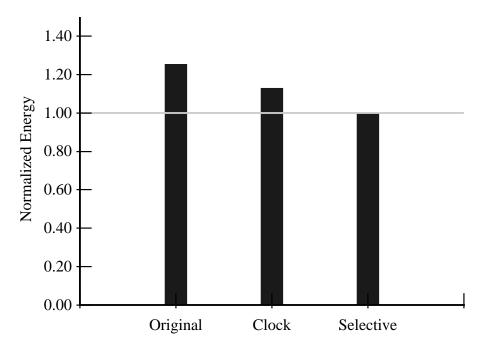

| Figure 3.3:  | Reduction in energy from simple optimizations                     | 29 |

| Figure 3.4:  | Normalized energy and performance for RISC and TORCH              | 30 |

| Figure 3.5:  | Energy breakdown for RISC and TORCH processors                    | 31 |

| Figure 3.6:  | Architecture of processor system.                                 |    |

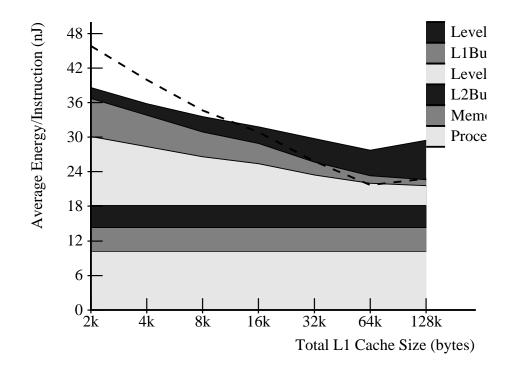

| Figure 3.7:  | Energy breakdown for single level hierarchy                       | 36 |

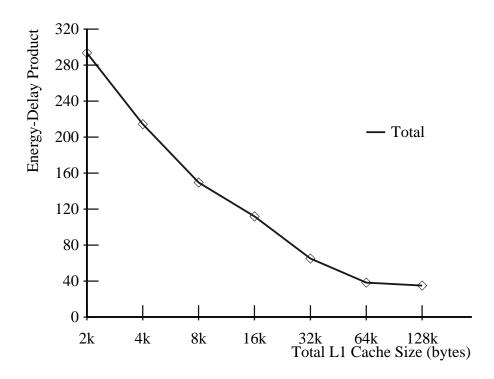

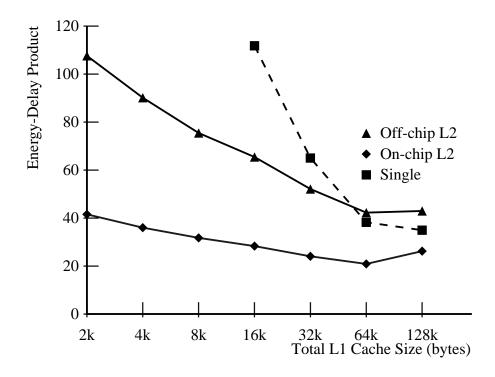

| Figure 3.8:  | Energy-delay product for single level hierarchy.                  |    |

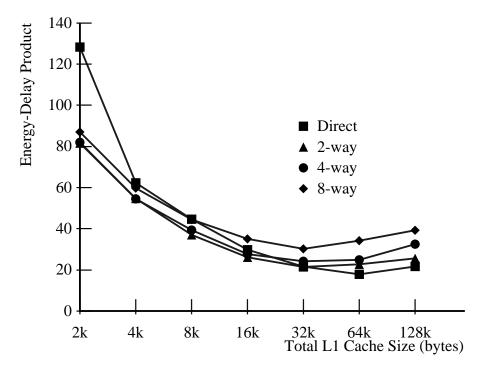

| Figure 3.9:  | Energy-delay versus associativity for single level hierarchy      | 38 |

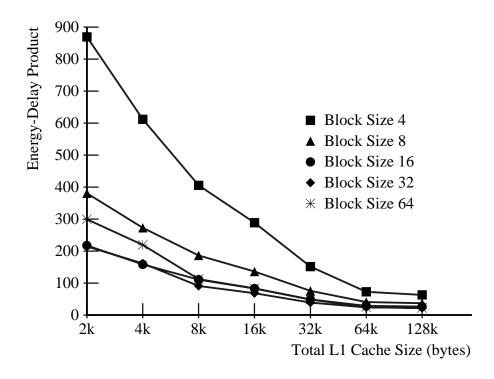

| Figure 3.10: | Energy-delay versus line size for single level hierarchy          | 39 |

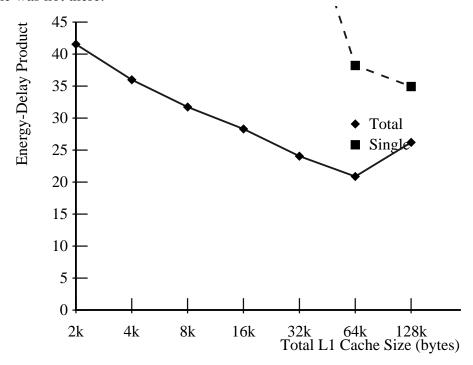

| Figure 3.11: | Energy-delay for two-level on-chip cache hierarchy                | 40 |

| Figure 3.12: | Energy breakdown for two-level hierarchy.                         |    |

| Figure 3.13: | Comparison of three memory hierarchies.                           | 42 |

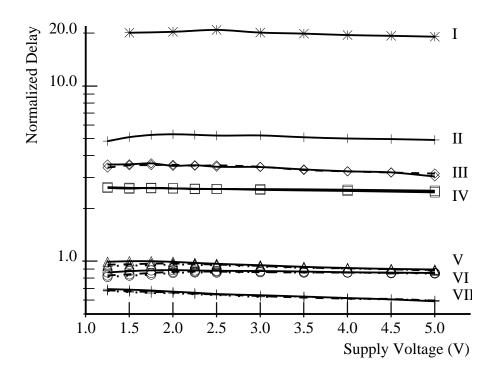

| Figure 4.1:  | Delay of circuit blocks divided by the delay of standard inverter | 52 |

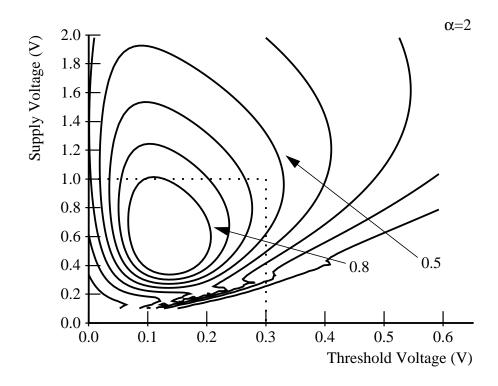

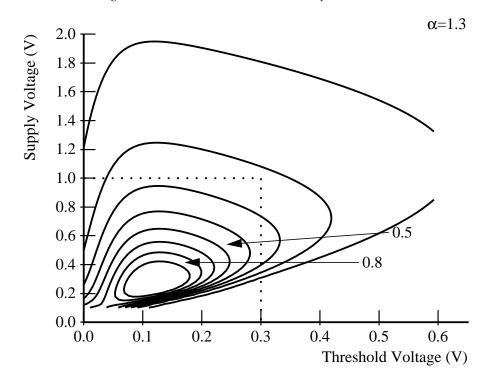

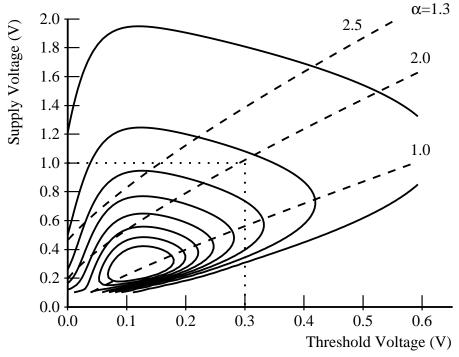

| Figure 4.2:  | EDP contours without velocity saturation                          | 56 |

| Figure 4.3:  | EDP contours with velocity saturation.                            | 56 |

| Figure 4.4:  | EDP and performance contours with velocity saturation             |    |

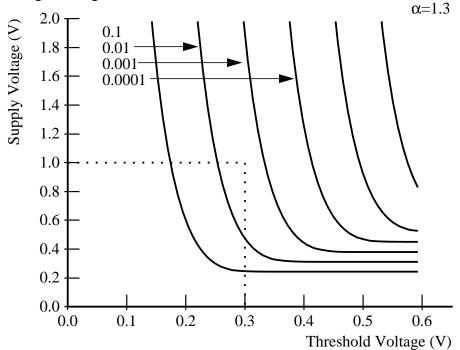

| Figure 4.5:  | Ratio of leakage to total power.                                  |    |

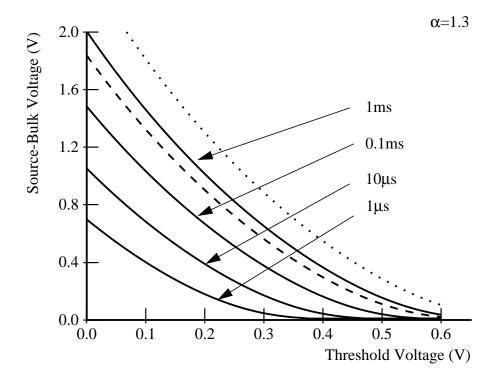

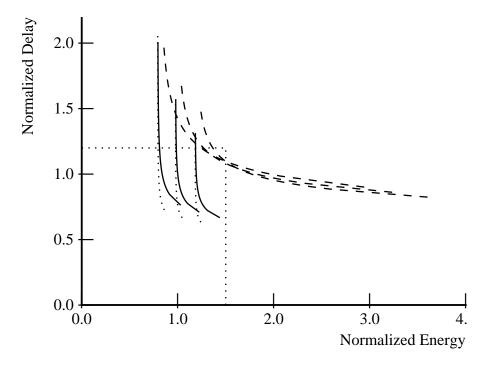

| Figure 4.6:  | Minimum time for threshold adjustment.                            | 60 |

| Figure 4.7:  | Variation in energy and delay.                                    |    |

| Figure 4.8:  | EDP contours with uncertainty.                                    |    |

| Figure 4.9:  | Ratio of EDP without and with uncertainty.                        |    |

| Figure 4.10: | EDP contours using HSPICE models.                                 |    |

| Figure 4.11: | Energy and delay variations with operating conditions             |    |

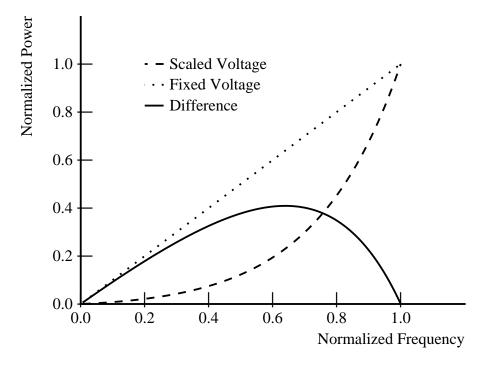

| Figure 4.12: | Power versus performance for fixed and variable supply            |    |

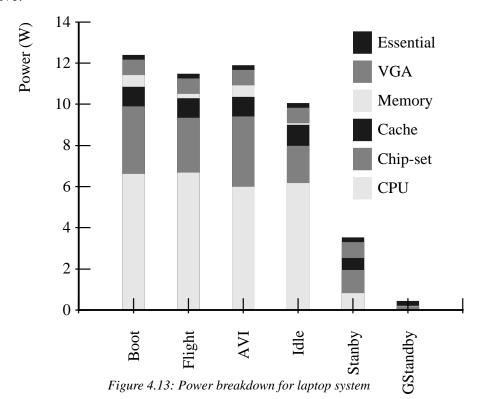

| Figure 4.13: | Power breakdown for laptop system                                 |    |

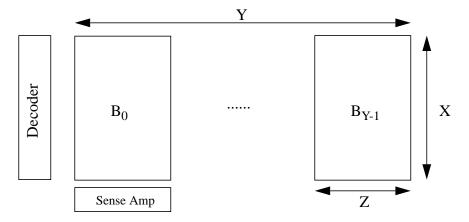

| Figure B.1:  | Cache power model.                                                | 87 |

# Introduction

In the past five years there has been an explosive growth in the demand for portable computation and communication devices, from portable telephones to sophisticated portable multimedia terminals [1]. This interest in portable devices has fueled the development of low-power signal processors and algorithms, as well as the development of low-power general purpose processors. In the digital signal processing area, the results of this attention to power are quite remarkable. Designers have been able to reduce the energy requirements of particular functions, such as video compression, by several orders of magnitude [2], [3]. This reduction has come as a result of focusing on the power dissipation at all levels of the design process, from algorithm design to the detailed implementation. In the general purpose processor area, however, there has been little work done to understand how to design energy efficient processors. This thesis is a start at bridging this gap and explores power and performance tradeoffs in the design and implementation of energy-efficient processors.

Performance of processors has been growing at an exponential rate, doubling every 18 to 24 months, as is shown in Figure 1.1. The bad news is that the power dissipated by these processors has also been growing exponentially, as is shown in Figure 1.2. Although the rate of growth of power is perhaps not quite as fast as the performance curve, it still has led to processors which dissipated more than 50W [4]. Such high power levels make cooling these processors difficult and expensive. If this trend continues processors will soon dissipate hundreds of watts, which is unacceptable in most systems. Thus there is great interest in understanding how to continue increasing performance without also increasing power dissipation.

For portable applications the problem is even more severe since battery life depends on the power dissipation. Lithium-ion batteries have an energy density of approximately 100Wh/Kg, the highest available today [5]. To operate a 50W processor for 4 hours requires a 2Kg battery, hardly a portable device. To address this problem processors manufacturers have introduced a variety of low-power chips. The problem with these processors is that they tend to have poor performance, as is shown in Figure 1.3. This

Figure 1.1: Evolution of processor performance.

Figure 1.2: Evolution of processor power.

figure plots on the Y-axis performance, measured as the average of SPECint92 and SPECfp92 [6], and on the X-axis energy, measured as watt/SPEC.

Figure 1.3: Performance and energy of processors.

In order to compare processor designs that have different performance and power one needs a measure of "goodness". If two processors have the same performance or the same power, then it is trivial to choose which is better—users prefer higher performance for the same power level or the lower power one if they have the same performance. But processor designs rarely have the same performance. In particular when determining whether to add a particular feature designers need to know whether it will make the processor more desirable. Chapter 2 introduces the energy-delay product, or EDP for short, as a measure of "goodness" for low-power designs. This chapter also describes the most common low-power techniques and explores how they affect the energy-delay product of CMOS circuits.

Chapter 2 will show that exploiting parallelism is one important technique enabling the reduction of the energy-delay of a circuit. Thus Chapter 3 explores how microarchitectural choices, which change the amount of parallelism the processor exploits, affect the efficiency of the processor. Since both the performance and energy dissipation of modern processors depend heavily on the design of the memory hierarchy, one must

look not only at the processor itself, but also explore how the design of the memory hierarchy affects the overall efficiency of the system. Using three idealized processor models Chapter 3 shows micro-architectural changes do not significantly improve the efficiency of the processor system. The processor's efficiency is set by a few circuits elements: memories and clocks.

Since memories and clocking circuits are critical components of every digital system, much work already has been done to reduce the energy requirements. A different approach to reduce the energy dissipation of clocks and memories is to change the technology by scaling the supply voltage and the threshold voltage of transistors. Chapter 4 explores tradeoffs in scaling the supply and threshold voltage of CMOS circuits. A simple mathematical model of the EDP predicts large gains in efficiency by scaling the supply and threshold voltages, especially if transistors are velocity saturated. If there is uncertainty in the supply and threshold, however, the gains in EDP are much smaller. Furthermore, to achieve these modest gains it may be necessary to give up large (3X) factors of performance. These tradeoffs are discussed in more detail in Chapter 4 along with a promising method to reduce the effect of variations by using adaptive techniques to control the supply and threshold.

Finally, Chapter 5 summarizes the contributions of this dissertation and proposes areas for future research.

# **Energy-Delay Product**

During the past few years many different techniques for reducing the power dissipation of CMOS circuits have been proposed, but relatively little work has been done to compare the benefits and costs of these different techniques. This chapter provides a review of these techniques and compares the effect they have on power and speed of the circuit. The rest of this thesis will investigate how the most promising of these techniques affect general purpose processors in particular.

This chapter begins by giving a brief description of the sources of energy dissipation in CMOS circuits, since it is important to understand this topic before addressing the question of how to reduce the energy dissipation. It then describes different metrics that can be used to compare designs. An attractive possibility is to represent every design as a point in the performance-energy plane. For CMOS, since energy and performance are highly correlated, it is often enough to compare the energy-delay product, or EDP for short.

## 2.1 Energy Dissipation in CMOS Circuits

There are three sources of energy dissipation in CMOS circuits; dynamic energy, static energy, and short-circuit energy. A simple CMOS gate consists of two transistors, represented as a resistor and a switch, connected to a fixed output load capacitance and a constant voltage source, as shown in Figure 2.1. Dynamic energy is due to the charging and discharging of the load capacitance. If the output node is originally at ground and assuming that it swings full rail, then an amount of energy equal to  $CV^2$  is drawn from the voltage source on a low to high transition. Of this amount,  $1/2CV^2$  is dissipated in the p-transistor to charge the load capacitance and  $1/2CV^2$  is stored in the capacitor itself. The stored energy is dissipated in the n-transistor to discharge the load. Thus  $1/2CV^2$  is dissipated on each transition. The circuit only dissipates dynamic energy when it is active or switching. If the output node remains at a fixed voltage level, then no energy is dissipated. Most nodes in CMOS circuits transition only infrequently; therefore the energy per cycle is usually written as,

$$E = \frac{nCV^2}{2} \tag{2.1}$$

where n is the number of transitions during the period of interest. If the circuit is synchronous and clocked at a frequency f then the average power can be written as,

$$P = aCV^2 f (2.2)$$

where a is the probability of a transition at the output node divided by 2. If a node transitions every cycle then a=0.5.

Figure 2.1: CMOS inverter.

Static energy is due to resistive paths between the supply and ground. The two main sources of static energy are analog or analog-like circuits which require constant current sources, and leakage current. Although there is some leakage current through the reverse biased diode between the source/drain and the bulk, the more important component is leakage through the channel when the transistor is nominally off [7]. The leakage current density (current per  $\mu$ m of gate width) is proportional to  $e^{-V_{th}/\gamma V_t}$ , where  $V_{th}$  is the threshold voltage of the transistor,  $V_t$  is the thermal voltage, and  $\gamma$  is a constant slightly

larger than 1. Static energy is important because it can limit the energy dissipation when the circuit is idle or in standby mode and there is no dynamic energy dissipation.

Short-circuit energy is due to both transistors being on simultaneously while the gate switches. Troutman [8] and Chatterjee [9] provide good descriptions of short-circuit current in CMOS circuits. As these papers show this component is usually small and therefore will be ignored for the remainder of this thesis.

For most CMOS circuits in today's technologies dynamic energy dissipation dominates. For example, in a  $0.6\mu m$  technology with  $V_{th}$ =0.9V leakage current is 4-5 orders of magnitude smaller than dynamic current (for one inverter in a 31 element ring oscillator). That is, only when the circuit is idle for 99.99% of the time does leakage current become an important consideration. As the amount of on-chip transistor width increases or the threshold voltage of the transistors decreases, leakage current becomes more significant. Chapter 4 explores in more detail how the energy efficiency of CMOS circuits changes as the threshold voltage changes.

In order to reduce the energy dissipation it is necessary to reduce one or more of  $\alpha$ , C, or V. The next section describes and compares how some often proposed low-power design techniques attempt to reduce these quantities and how they effect the power and performance of CMOS circuits.

## 2.2 Low-Power Metrics

When optimizing a design for low power it is necessary to have a metric that can be used to compare different alternatives. The most obvious choice is power, measured in watts. Power is the rate of energy use, or P=dE/dT. A more useful definition, however, is average power, or the energy spent to perform a particular operation divided by the time taken to perform the operation  $P_{avg}=E_{op}/T_{op}$ . How to define the operation of interest is arbitrary and depends on what is being compared. In the case of a processor, it could be the energy to run a benchmark to completion, or the energy to execute an instruction—as long as all processors compared execute the same instructions.

Power is important for two reasons. The first is that it determines what kind of package can be used for the chip. For example, a small plastic package, the cheapest form of packaging, can only dissipate a few watts. A processor which dissipates more than that will have to be sold in a more expensive package. The second reason power is important is

because it limits how long the system battery will last. But power as a metric of "goodness" of low-power designs has some drawbacks. The most important drawback is that power is proportional to the operation rate, so one can reduce the power by slowing down the system. In CMOS circuits this is very easy to do, one simply reduces the clock frequency.

Regardless of what definition of an operation one uses, the basic problem with power remains, that power decreases simply by extending the time required to complete an operation. Power, therefore, is only a good metric to compare processors that have similar performance levels. If two processors can perform computation at the same rate, then clearly whichever dissipates less power is more desirable. If the processors run at different rates the slower processor will almost always be lower power.

An alternative metric is the energy per operation, measured in jules/op, or its inverse, measured in SPEC/watt or MIPS/watt. This metric does not depend on the time taken to perform the operation, since running the processor at half the frequency means you need to accumulate the power for twice as long. The problem with this metric is that, from Equation (2.1) the energy per operation can be made smaller by lowering the supply voltage. However, the supply voltage also affects the speed or performance of the basic CMOS gates, with lower supplies increasing the delay per operation. Thus low energy solutions might (and often do) run very slowly.

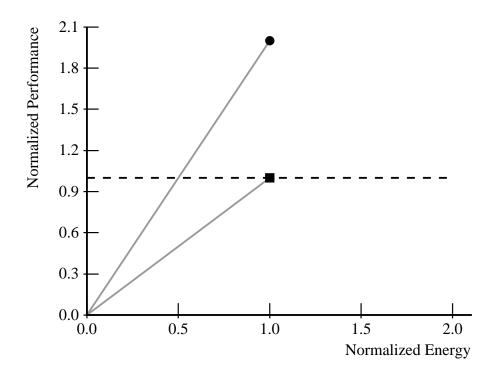

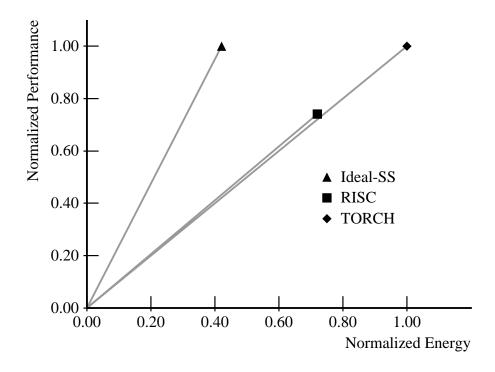

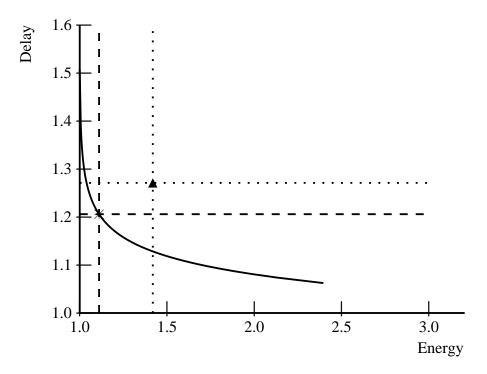

Another alternative is to use both metrics, energy and speed. Rather than representing designs by a single number they are represented as a point in the performance-energy plane, as in Figure 1.3 and Figure 2.2. Given some requirements, such as minimum performance or maximum energy, one can determine which is the best solution available. The problem with this representation is how to compare designs which have different performance or energy levels. Without additional requirements, such as area or cost, there is no way to decide which solution is better.

From an optimization standpoint one possible metric is the product of energy and delay, measured in jules-sec, or its inverse, measured in SPEC<sup>2</sup>/watt. Optimizing the energy-delay product will prevent the designer from trading off a large amount of performance for a small savings in energy, or vice versa. As will be described later the energy-delay is also an attractive metric for other reasons. In Figure 2.2 the EDP corresponds to the inverse of the slope of a line that connects a design point to the origin. Thus finding a solution with a low EDP corresponds to finding a solution which lies on a steeper line.

Figure 2.2: Performance-energy plane.

## 2.3 Low-Power Design Techniques

From Equation (2.1) one simple way to reduce the energy per operation is to lower the power-supply voltage. However, since both capacitance and threshold voltage are constant, the speed of the basic gates will also decrease with this voltage scaling. The delay of a CMOS gate can be modeled as the time required to discharge the output capacitance by the transistor current,  $T_g = CV/I$ . Using the current model presented by [10] this gives,

$$T_g = K \frac{V}{(V - V_{th})^{\alpha}} \tag{2.3}$$

where  $\alpha$  is the velocity saturation coefficient and K is a technology specific constant. When transistors are not velocity saturated  $\alpha$ =2.0 and the equation reduces to the quadratic model for transistor current. As transistors become more velocity saturated  $\alpha$  decreases towards one. For typical 0.25 $\mu$ m technologies  $\alpha$ =1.3-1.5.

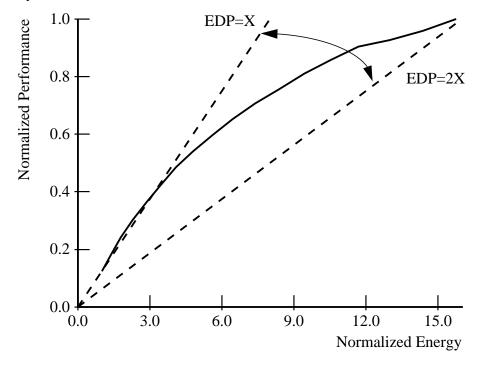

Figure 2.3 plots the normalized speed of operation versus the energy per operation of a CMOS gate as the supply voltage is scaled. The speed and energy were found by simulating an inverter in a 0.6µm technology using HSPICE. The threshold voltage is held constant in this example. At large voltages reducing the supply reduces the energy for a modest change in delay. This causes the curve to bend over. At voltages near the device threshold, small supply changes cause a large change in delay for a modest change in energy. But from  $V=1.5V_{th}$  to  $V=6V_{th}$  changes in energy and delay cancel each other and the curve approaches a straight line, which corresponds to a constant energy-delay product. Over this region the EDP remains within a factor of 2. In this case scaling the supply voltage reduces the power dissipation but at the expense of the speed of the gates. Looking at Equation (2.3), we see that one way to gain back the performance lost is to scale the threshold voltage. But this increases the leakage current. Chapter 4 explores the tradeoff between power and performance from scaling the supply and threshold voltages. It will be shown, however, that when leakage power is a very small fraction of the total power, as is the case in most technologies today, scaling the supply voltage does not significantly affect the EDP.

Figure 2.3: Variation in performance and energy with supply voltage.

Another technique to reduce the energy per operation is to reduce the size of all transistors in the gate. This reduces the capacitance that needs to be switched when one of the input

switches. Unfortunately it also decreases the current drive of the gate, making it slower. This can be partly compensated by making the next gate smaller. At some point, however, the load of the gate will no longer be dominated by the input capacitance of the following gates, but rather by the capacitance of the interconnect between gates.

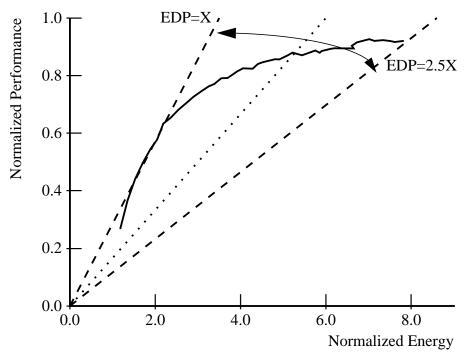

Figure 2.4 graphs the normalized energy per operation versus the speed of operation of a CMOS gate as the percentage of loading that is due to gate capacitance varies from 20% to 80%. The diffusion capacitance also depends on transistor width and therefore the percent of loading that depends linearly on the transistor width is larger than shown in the figure. The dotted line indicates the point at which 80% of loading is proportional to transistor width. The load will be mostly wire capacitance for small transistor, and will be mostly gate capacitance for large devices. Continuing to increase the transistor sizes gives very small gains in performance for a large energy cost. This causes the curve to be almost flat. But for the points shown in the figure the difference in EDP is a factor of 2.5.

Figure 2.4: Variation in performance and energy with transistor sizing.

Clearly, real circuits are more complex. The gate and wire capacitance is different for every gate, nodes transition at different frequencies, and not all gates are on the critical path. While this problem is difficult to solve precisely, the basic tradeoff remains the same.

Sizing the transistors allows the designer to tradeoff speed for power. At either extreme (very large or very small transistors) the tradeoffs become poor.

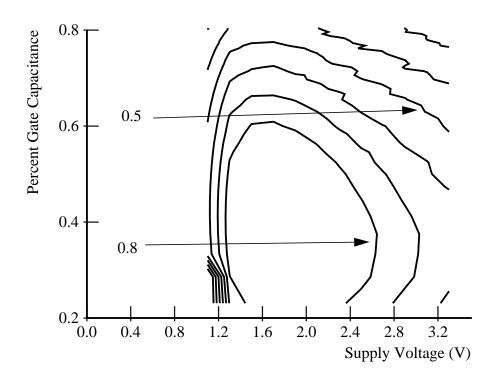

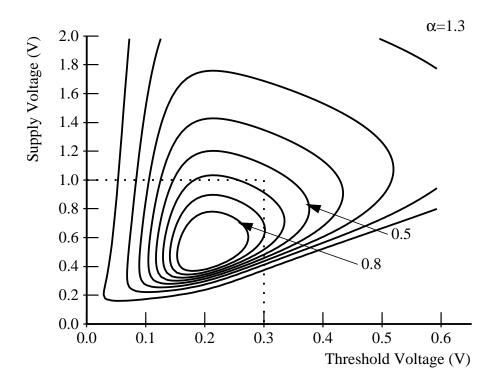

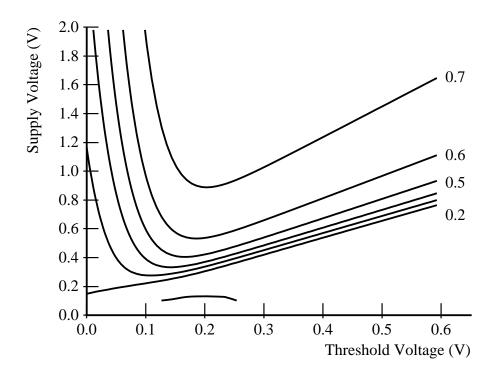

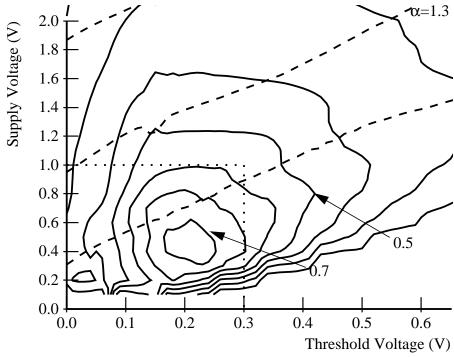

Often one wants to optimize two, or perhaps more, variables simultaneously. For example one may want to find the optimal supply voltage and transistor size. One way to visualize the data is to plot contours of energy, delay, and perhaps energy-delay, on the supply voltage vs transistor size plane. Figure 2.5 is an example of such a plot, and gives contours of inverse relative EDP versus transistor size and supply voltage. The Y-axis shows the percent of the total load that is due to gate capacitance, and the X-axis shows the supply voltage. For the range of supply voltage and gate loading shown in this figure there is a local minimum in the EDP at V=1.7V and 40% gate loading. The relative EDP is the EDP normalized to the minimum value. The figure plots contours of the inverse of this metric. Thus the value at the minima is 1 and decreases as one moves away from the minima. The contour labeled 0.5 has twice the minimum energy-delay. The advantage of representing the data this way is that it is much easier to understand how the variables of interest (energy, delay, energy-delay) change with the optimization variables (supply voltage, transistor sizing). If the data were plotted in the energy vs. performance plane then understanding whether decreasing the supply voltage is a win is harder. In Chapter 4 this technique is used to visualize how energy and delay change over a broad range of supply and threshold voltages.

The reason the energy-delay product can be used to represent the performance-energy plane is that these low-power techniques allow the designer to trade excess performance for lower power. In Figure 2-2, for example, using voltage scaling the performance of the design marked with a circle can be reduced until it just meets the performance target. At that point it dissipates less energy than the design marked with a box so it is clearly a better choice. Moving the design to a steeper line, that is reducing the energy-delay, will result in a lower energy solution for the same performance. Using the EDP relies on the assumption that it is possible to almost linearly trade performance and energy. If this were not true, then one would again have to resort to the performance-energy plane. Fortunately this condition is true for most circuits today. For the reminder of this thesis, except for Chapter 4, the EDP is often used to compare different design alternatives. Scaling the threshold voltage can make this condition no longer true. In that case the performance and energy are used.

Adiabatic or charge-recovery circuits are another method that allow a designer to trade energy for performance [11], [12]. These circuits resonate the load capacitance with an

Figure 2.5: EDP contours versus transistor size and supply voltage.

inductor, which recovers some of the energy needed to charge the capacitor. The energy loss in switching the load can be reduced to  $CV^2T/\tau$ , where T is the intrinsic delay of the gate, and  $\tau$  is the delay set by the LC circuit. By changing the time constant of the LC circuit it is possible to linearly trade speed for switching energy leaving the EDP constant. The problem with these circuits is that for a given performance level they have larger energy requirements than normal CMOS gates [13]. Thus adiabatic circuits become attractive only when one needs to operate at delays beyond the range viable by voltage scaling and transistor sizing standard CMOS.

To increase the energy efficiency of the circuits it is necessary to move to a steeper line on the performance-energy plane. As was described earlier voltage scaling and transistor sizing do not dramatically change the EDP. One of the best techniques to improve the energy-delay product is to improve the technology. Under ideal scaling [14] if the minimum transistor length shrinks by a factor  $\lambda$ , then the energy per operation will shrink by a factor  $\lambda^3$  and the delay will shrink by  $\lambda$ . Thus the EDP will decrease by  $\lambda^4$ . Therefore a 0.7 shrink of a chip will result in 1/4 the energy-delay. At the same performance the processor will dissipate 1/4 the power. Unfortunately most technologies do not scale ideally [15]. Often the threshold voltage does not scale linearly with  $\lambda$ . Furthermore, the performance of the processor, as will be shown in Chapter 3, depends heavily on the

performance of the external memory system, which also does not scale linearly with the technology. Even if the threshold voltage does not scale, the reduced capacitance improves both the energy and the delay, so their product scales at least as  $\lambda^2$ .

Another way to improve the energy-delay product is to avoid wasting energy—avoid causing unneeded node transitions. One common approach to solve this problem is to make sure that idle blocks do not use any power. In CMOS circuits this can be accomplished by disabling the clock of that block therefore preventing any more transitions in the block. This technique is called selective activation because only blocks which produce a useful result are activated. The key to selective activation is to control objects that dissipate a significant amount of power. Chapter 3 explores in more detail what power savings are possible in a processor by using selective activation, and which blocks are likely candidates for selective activation.

Processors designers have used selective activation at many levels in order to reduce the power dissipation. Banked caches—only part of the memory array is activated on every access [16]—are common in low-power processors, such as the MIPS **R4200** [17] and **R4600** [18], the **PowerPC 603e** [19], and the **StrongArm-110** [20]. Some low-power processors, such as the **PowerPC 603e**, also contain control logic which determines, on a cycle by cycle basis, which functional units need to be activated.

Another common technique to reduce wasted power is to slow down the clock frequency when the processor is idle. All of the low-power processors listed before have a reduced power mode where the clocking frequency is reduced to a fixed multiple of the system clock. In some cases the processor clock can be stopped completely. Reducing the clock frequency when idle will, on average, extend battery life. But it will not make the processor more efficient *per se*. Reducing transitions while the processor is active can give some power savings but, as will be shown in Chapter 3, these savings are limited to less than a factor of two or three. In order to obtain larger savings it is necessary to look at the problem from the system level.

Re-thinking an algorithm can give orders of magnitude improvement in energy-delay. Accessing memories, for example, is relatively expensive in energy terms, while performing computation is relatively cheap. For many applications it is possible to reduce the energy dissipation by performing more computation in order to reduce the number of memory accesses [21]. In many cases rethinking the algorithm gives an improvement in both energy and delay, which means the energy-delay decreases as the square of the gains.

If an algorithm requires two operations in series—each of which requires one unit of time and one unit of energy—then changing the algorithm so that it only requires one operation will decrease the EDP by a factor of four, a factor of two from the energy and a factor of two from the delay. Tsern and Gordon [22], [3] estimate that redefining the DSP compression algorithm provided at least an order of magnitude reduction in the energy-delay product.

Unfortunately designers of general purpose processors cannot re-think the algorithm. That is something only the system programmer can do. Fortunately, however, redefining the algorithm is not the only way to attack the problem at a system level.

One can improve the energy-delay product by reducing either the energy or the delay per operation. One way to reduce the effective delay without affecting the energy—to a first approximation—is to exploit parallelism. For example, if one functional unit can execute one operation every cycle, then adding a second functional unit in parallel will double the performance, to two operations per cycle, but leave the energy per operation unchanged. This is because it now takes roughly twice the energy to compute two results. The EDP is cut by half. Ideally the energy-delay goes down with N, the degree of parallelism. In reality, however, there is always some energy and delay overhead to distribute the operands and to collect the results. Furthermore, the amount of parallelism may be limited—the second functional unit may be idle part of the time—so the actual improvements in both performance and EDP will be smaller than N. However, exploiting parallelism is a very powerful general technique to increase the energy efficiency of circuits.

The improvements in energy-delay is independent of how the parallelism is extracted (pipelining, parallel machine, etc.) although the overhead factors will be different. For DSP applications with a large amount of parallelism, the performance gains allow the resulting systems to run at very low supply voltage, use small transistor sizes, and still meet their performance targets [23].

Exploiting parallelism has been a common way to increase the performance of processors. In the late 80's RISC processors popularized pipelining as a way of exploiting parallelism. Pipelining overlaps the execution of instructions, so that even if an instruction takes more than one cycle to execute, it appears as if the processor can execute one instruction per cycle. During the early 90's super-scalar machines, which can execute more than one instruction per cycle, became popular. These machines exploit parallelism both by

pipelining and by executing more than one instruction per cycle, as is shown in Figure 2.6 In the past few years the maximum issue size of processors has increased, to try to exploit more parallelism. Unfortunately the parallelism available in typical programs is very limited [24], [25], [26]. Researchers have found that for realistic machines the cycles per instruction (CPI) is greater than 0.5. This means on average less than two instructions start execution on every cycle. Trying to extract additional parallelism often results in decreased performance because the added hardware increases the cycle time. Therefore even if the amount of parallelism available is larger [27] the performance gains are limited.

Figure 2.6: Scalar and super-scalar processors pipeline diagrams.

One surprising fact is that parallelism does not seem to greatly affect the energy-delay of processors. Table 2.1 shows more information for the same processors as in Figure 1.3. The SPEC<sup>2</sup>/W metric, which is inversely proportional to the energy-delay, does not seem to correlate with the maximum issue size of the machine, as previous paragraphs suggest. This result is rather surprising since designers of signal processing chips have used parallelism to dramatically improve the efficiency of their circuits. The next chapter explores the effectiveness of exploiting parallelism in improving the energy-delay product of processors, and explains why the results are modest.

|                      | Dec 21164 | UltraSPARC | P6      | R4600   | R4200   | Power 603 |

|----------------------|-----------|------------|---------|---------|---------|-----------|

| SPECavg92            | 426.00    | 305.00     | 175.00  | 97.00   | 42.50   | 80.00     |

| Power                | 50.00     | 30.00      | 15.00   | 5.500   | 1.80    | 3.00      |

| SPEC <sup>2</sup> /W | 3629.50   | 3100.83    | 2041.70 | 1710.33 | 1003.47 | 2133.33   |

| $L_{min}$            | 0.50      | 0.45       | 0.60    | 0.64    | 0.64    | 0.50      |

| $SPEC^2/W\lambda^2$  | 4480.90   | 3100.83    | 3629.69 | 3459.51 | 2029.73 | 2633.74   |

| Max Issue            | 4         | 4          | 3(3)    | 1       | 1       | 2         |

Table 2.1: Current processors.

2.3 Low-Power Design Techniques

# **Micro-architectural Tradeoffs**

This chapter explores how the micro-architecture of a processor changes its energy efficiency. One common technique to speed-up processors is to overlap the execution of instructions, i.e. to exploit the parallelism available at the instruction level. This can be accomplished by simply pipelining the execution of instructions, or more aggressively by executing more than one instruction at once. The next section investigates the tradeoffs in energy-delay of exploiting instruction level parallelism (ILP) using idealized models of pipelined and super-scalar processors. The results show that pipelining gives a large boost in efficiency while super-scalar issue only gives a small improvement. Then Section 3.2 explores how far current implementations are from these inherent limits by looking at two processor implementations, a simple RISC machine and TORCH—a super-scalar processor designed at Stanford. In Section 3.3 the energy dissipation of these realistic machines is categorized into four components. The section shows that most of the energy dissipation is in clocking and storage circuits.

Simply increasing the rate at which the processor can execute instructions is not enough. Often the memory system cannot provide enough instructions and data for the processor to operate on. That is, the performance is limited by the memory system. Furthermore, the memory system dissipates a considerable amount of power, sometimes more than the processor itself. Section 3.4 explores how the design of the memory hierarchy affects the energy-delay product of the system as a whole.

Finally the last section of this chapter investigates how more sophisticated architectural features, such as non-blocking caches and out-of-order issue, will affect the energy-delay of processors.

## 3.1Lower Bound on Energy and Energy-Delay

Although there have been several papers that have presented dramatic reductions in the power dissipation of processors, there has been no work to investigate what is the lower bound on the energy and energy-delay product. Therefore one cannot determine if the

reductions accomplished represent a large fraction of the potential improvements. This section investigates what these bounds are by looking at three idealized machines: an unpipelined processor, a simple pipelined RISC processor, and a super-scalar processor.

All processors fundamentally perform the same operations, they sequence through the steps shown in Figure 3.1. They fetch instructions from a cache, use that information to determine which operands to fetch from a register file, then either operate on this data, or use it to generate an address to fetch from the data cache, and finally store the result. These operations are sequenced using a global clock signal. High performance processors have sophisticated architectural features that improve the instruction fetch and data cache bandwidth and exploit more instruction level parallelism. But they must still perform these basic operations for each instruction. In a real processor, of course, there is much more overhead. For example, often many functional units are run in parallel and only the "correct" result is used. In addition considerable logic is needed to control the pipeline during stalls and exceptions. However, since this overhead depends on the implementation and in some sense is not essential to the functionality of the processor it will be neglected. Most of the operations outlined above require either reading or writing one of the on-chip memories—instruction and data caches, and the register file. Only one of the steps requires computation. So it will be aggressively assumed that the energy cost of performing computation is zero, and also that communication costs within the datapath is also zero. Only the energy needed to read and write memories, and, where required, the energy to clock essential storage elements, such as pipeline latches is considered. Furthermore these ideal machines only dissipate energy when it is absolutely necessary. Most processors perform some operations speculatively, in the hope that the result is useful. These ideal machines have perfect knowledge so there is never a need for speculative operations or unwanted transitions, such as glitches.

## 3.1.1 Simulation Methodology

To estimate the energy dissipation of these idealized machines a simple trace based method is used. In these machines all the energy is dissipated in memories or storage elements, and is independent of the data values. The energy required to read a memory is independent of the data value read. The number of memory accesses is computed from the instruction trace. The product of the energy per operation times the number of operation of each type gives the total energy dissipation. The clock energy is found by determining the capacitance of a single latch and multiplying by the minimum number of latches to maintain the processor state and ensure correct operation.

Figure 3.1: Basic processor operation.

The memory power model developed by Amrutur (described briefly in Appendix B) was used to estimate the power of the caches. The memory model was developed for a 0.8µm process, so this process is used throughout this chapter for the simulations. The power of the register file was estimated by using a modified version of Amrutur's models to account for the difference in size and the number of read/write ports needed. The power model of the register file takes into account the number of active ports so the power requirements depend on the number of operands being read and written.

The latency of the functional units only depends on the particular implementation and is independent of the processor micro-architecture. The latency of the functional units can be characterized by the number of equivalent fanout-of-four inverters which have approximately the same delay<sup>1</sup>. The cycle time of the processor, if it is pipelined, can be measured using the same units. For current processors the cycle time is in the order of 30 fanout-of-fours. Chapter 4 will explain in more detail why using the equivalent number of fanout-of-four inverter delays is a good metric. The latencies of the functional units, in inverter delays, are assumed to be as follows: branch 60 (2 cycles), ALU 90 (3 cycles), and load/store 120 (4 cycles).

<sup>1.</sup> A fanout-of-four inverter drives four equally-sized inverters.

The energy dissipation depends also on the benchmark being run, since it determines how many times the on-chip memories must be accessed. Due to the limited simulation speed (only about 1 Hz when simulating the complete machines described in the next section) only two benchmarks from the SPEC benchmark suite were used: compress and jpeg. The first is typical of integer programs that have many unpredictable branches. The second is typical of multimedia programs which are becoming popular. Due also to the slow simulation speed the benchmarks were run with reduced inputs. The benchmarks were compiled using the TORCH optimizing C compiler or the MIPS C compiler, depending on the target machine.

### 3.1.2 Machine Models

The simple machine is the most basic compute element, similar to DLX [28]. The processor consists of a state machine that fetches an instruction, fetches the operands, performs the operation and stores the result. The processor is not pipelined so each instruction completes before the next one is fetched. Since this machine is not pipelined no energy is dissipated in clocking. Only the energy required to read and write the caches and register file is taken into consideration. This implementation should have the lowest average energy per instruction; however, since it does not take advantage of the available parallelism, it will have relatively poor performance and high energy-delay product.

To improve performance one can create a pipelined processor that is similar to the previous one, except that it uses pipelining to exploit instruction level parallelism. That is, more than one instruction is executed concurrently. Thus the change in energy-delay product of this machine compared to the ideal will be due entirely to pipelining. This machine uses the traditional MIPS or DLX [28] 5-stage pipeline shown in Figure 2.6. In a pipelined machine, because multiple instructions are being executed simultaneously, it is necessary to have some synchronization or storage elements, such as flip-flops or latches, in the datapath portion of the machine to ensure that data from different instructions do not corrupt each other. Therefore in addition to the energy required to read and write memories the energy required to clock the latches in the pipeline and the PC chain is also taken into account.

The ideal super-scalar processor is similar to the pipelined machine, except that it can execute a maximum of two-instructions per cycle. One can classify super-scalar processors into two groups, statically scheduled and dynamically scheduled. Statically scheduled processors rely on the compiler to determine an instruction execution sequence

that guarantees program correctness. The compiler must ensure that before an instruction is executed all of its source operands are available. Dynamically scheduled processors rely on on-the-fly dependency analysis to determine which instructions can be executed concurrently. In these machines the hardware ensures that when an instruction is executed its source operands are available. For this idealized machine how the ILP is found is not important, since the energy dissipated in the control logic is not taken into account. What matters is how much parallelism is exploited. Therefore the experiments were done using an aggressive static scheduler from TORCH [29] which gives comparable performance to a dynamic scheduled machine. Since most integer programs do not have enough parallelism to fill both issue slots regularly, this machine supports some conditional execution of instructions as directed by the compiler. This machine is an idealization of the TORCH machine that is described in a later section. The difference in energy-delay product between this machine and the previous one will be due to the ability to exploit more parallelism by executing two instructions in parallel each cycle.

### 3.1.3 Comparison of Energy and Energy-Delay Product

Figure 3.2 shows the total energy required to complete a benchmark on the three machines versus their performance. All numbers in this section have been normalized to the corresponding value for the super-scalar processor. As expected the unpipelined machine has the lowest energy dissipation, and the super-scalar machine has the highest. The unpipelined machine, however, has relatively poor performance. One can instead build a pipeline processor, which dissipates slightly more energy but has much better performance. Thus it has a much lower energy-delay—about 2X lower than the unpipelined machine. Super-scalar issue only gives a small improvement in energy-delay product. The performance gain is smaller and the energy cost is higher. In this simple model, a processor with a wider parallel issue would be of limited utility for reducing the EDP. The basic problem is that the amount of instruction level parallelism (in the integer benchmarks used) is limited, so the effective parallelism is small. Yet increasing the peak issue rate increases the energy of every operation, even in this ideal machine because the energy of the memory fetches and clocks will increase. Furthermore, the speedup of the super-scalar processor is limited by Amdahl's law. All three processors spend the same number of cycles waiting for data from memory because the memory hierarchy is the same for all three. As the performance of the processor increases the stall time becomes a larger fraction of the total execution time, so that the corresponding decrease in energydelay product will be smaller. As will be shown in the following section, the overhead in a

super-scalar machine is actually worse than that of a simple machine, and overwhelms the modest gain in energy-delay product gained from parallelism.

Figure 3.2: Normalized performance and energy of idealized machines.

# 3.2 Processor Energy-Delay Product

To see how real machines compare with the ideal machines described in the previous section, this section looks at two processors designed at Stanford, a simple RISC machine and a super-scalar processor called TORCH. For the real processors all sources of overhead were considered, including control, communication, and all architecturally defined state. This is unlike the idealized machines where attention was focused only on the essential operations. As has been shown before [17], [30], [19], [31], some simple optimizations can yield significant gain in energy dissipation. So these optimizations, which are described in Section 3.2.3, were performed on our processors as well.

The simulation framework for evaluating these machines is given next, and is followed by a brief description of the two machines we simulated. Having described the simulation setup the energy and delay results are presented and then are compared to the idealized machines presented earlier.

## 3.2.1 Simulation Methodology

CMOS gates dissipate energy only when their outputs transition. Thus the energy dissipation over time depends on the particular input sequence chosen. For a processor this implies that the energy to run a benchmark depends on the data used by the program. This makes simulating the real machines hard, since it is necessary to model the machines in great level of detail.

In order to estimate the total energy dissipation it is necessary to know how many times each node transitioned, and what the total capacitance of that node is. Fortunately a complete RTL (Verilog) description of both processors under investigation was available. The model includes the main datapaths, instruction and data caches, co-processor 0 (system or privileged state), TLB, and external interface; although it does not include a floating point unit. The model can stall, take exceptions and interrupts, or suffer cache misses. Specialized CAD tools were developed to estimate the total capacitance at each node in the model. The operation of the CAD tools is described in Appendix A. A commercial Verilog simulator is used to run a benchmark on the processor model. During the simulation a special tool accumulates the number of transitions on every node. The total energy dissipation is proportional to the sum over all nodes of the transition count times the capacitance.

The on-chip memories are modeled by assuming a certain energy dissipation every time the memory is read or written. For example, whenever the instruction cache access signal is enabled all of the access energy is added to the total. No toggle or capacitance information is kept for the internal nodes of the memories. The processors implemented contain a TLB which is also modeled using a modified version of Amrutur's model. For the TLB it is important to model the power dissipation of the match lines. On an access they are all pre-charged high and all but one transition low. The power of the TLB was 150mW at 100MHz.

To ensure accurate comparisons with the idealized machines the same benchmarks were run on these processors. See Section 3.1.1.

#### 3.2.2 Machine Models

The simple RISC processor is similar to the original MIPS R3000 described by Kane [32], except that it includes on-chip caches. The processor has the same five-stage pipelined that was shown in Figure 2.6. This processor is similar to the ideal pipelined machine

except that it accounts for all the energy required to complete the instruction and it includes all the overhead associated with the architecture, such as the TLB and coprocessor 0. The difference in energy-delay product between this processor and the pipelined ideal machine represents a limit on possible improvements in efficiency by focusing only on the logic required to execute an instruction.

TORCH [29] is a statically scheduled two-way super-scalar processor, which uses the same five stage pipeline that was shown in Figure 2.6. TORCH supports conditional execution of instruction directed by the compiler. The processor includes shadow state that can buffer the results of these conditional instructions until they are committed. To improve the code density a special NOP bit is used to indicate that an instruction should be held for a cycle before it is executed. This is important in programs that do not have enough parallelism to keep both datapaths busy because it improves the instruction cache performance and reduces the number of cache accesses needed to complete a program. Instructions are encoded in a 40-bit word which are packed in main memory using a special format that improves the instruction fetch efficiency. Instructions are unpacked as they are written in the first level instruction cache.

TORCH is a good example of a low-power super-scalar processor since it should have a smaller overhead than a dynamically scheduled machine. And because TORCH has similar performance as a dynamically scheduled machine [29] TORCH should have lower energy-delay. Section 3.5 examines in more detail the energy cost of out-of-order issue.

## 3.2.3 Energy Optimizations

The additional energy associated with a particular architectural feature can be divided into overhead and waste. Overhead is that part of the energy that cannot be eliminated with careful design. For example, adding additional functional units will increase the average wire length thus increasing the overhead of the architecture. Other sources of energy can simply be designed away. For example, in a pipelined design clock gating can be used to eliminate unwanted transition of the clock during interlock cycles. A good implementation will reduce waste as much as possible. However, the designer must carefully weigh the gains in power dissipation versus the cost in complexity or cycle time. If a particular optimization causes a large increase in cycle time then dissipating slightly more energy but running at a higher frequency may be better.

As this section will show eliminating all of the waste is difficult because much of it is scattered among a large number of functional units. The key to effectively reducing

energy waste is to find points that have large leverage such that a small design change will produce large energy savings. Thus nodes which have a large amount of capacitance, such as clocks and buses, are prime target for selective activation. Furthermore large structures, such as memories are also good candidates since they dissipate a large amount of energy and can be easily controlled. Most memories have a read enable and write enable signals. Following are a few techniques that were used to reduce waste in the implementations.

Clock gating can be used to eliminate transitions that have no effect. In these implementations latches in the datapath are qualified when the instruction does not produce a result or when the processor is stalled waiting for data from the outside world. In TORCH densely coded NOP's improve the code density and reduce the number of instruction cache accesses. However, they introduce extra instructions into the pipeline which can cause spurious transitions. Using clock gating can eliminate these spurious transitions. Also, all latches that are not in the main execution datapath are qualified. These latches tend to be enabled only infrequently, and clocking them every cycle is inefficient. For example, latches in the address translation datapath only need to be enabled on a load or store instruction, or during an instruction cache miss.

Most of the latches in the control sections are not qualified since this can introduce clock skew. Control sections are automatically synthesized and therefore it is not possible to have very fine control over the implementation of clock gating. However, the power dissipated in the control sections is only a small fraction of the total power, and the clock power is only a fraction of that. Some control signals are qualified to prevent spurious transitions in the datapath buses. If an instruction has been dynamically NOPed then preventing the datapath latches from opening is not sufficient. If the control signals to the datapath change, this can cause spurious transitions on some of the datapath buses, which can cause significant energy consumption. Since buses have large amounts of capacitance spurious transitions can dissipate significant amounts of power.

The use of clock gating saved approximately one third (33%) of the clock power or close to 15% of the total power. Most of the latches in datapath blocks have an enable signal. To further reduce the energy it would be necessary to either make the enabling signal more restrictive or qualify latches in the control sections. In either case further improvements would require a larger effort and provide smaller returns.

Selective activation of the large macro-cells was used to reduce power dissipation. Obviously the most important step was to eliminate accesses to the caches and the register file when the machine is stalled. Also important was to eliminate accesses to the instruction cache when an instruction is dynamically NOPed. In this case the instruction has already been read on the previous cycle so there is no need to re-read the cache. By doing so approximately 8% of the power dissipation was saved.

Speculative operations are commonly used to improve the performance of a microprocessor. For example two source operands are read from the register file before the instruction is decoded. This reduces the critical path but consumes extra energy, since one or both operands may not be needed. One simple way to eliminate the waste is to predecode the instruction as they are fetched from the second-level cache, and store a few extra bits in the instruction cache. Each bit would indicate whether a particular operand should be fetched from the register file. Since the energy required to perform a cache access is not a strong function of the number of bits accessed the cost will be small.

The designers of the DEC 21164 chip used a similar idea [4]. The second level cache is 96KB 3-way set-associative. To reduce the power dissipation the cache tags are accessed first. Once it is known in which bank, if any, the data is resident in, only that bank is accessed. This reduces the number of accesses from 4 to 2, reducing the power dissipation. However, the first-level cache refill penalty increases by one cycle.

The idea of reducing speculative operations should not be taken too far. In TORCH, as in most microprocessors, computing the next program counter (PC) is one of the critical paths. The machine must determine whether a branch is taken, and then perform an addition to either compute the branch target or to increment the current PC. To remove the adder from the critical path, TORCH performs both additions in parallel, while the outcome of the branch is determined, and then uses a multiplexer to select one of the two results. The energy saved by eliminating the extra addition is negligible, while the cycle time penalty is large. Thus designers should carefully consider the tradeoff when eliminating speculative operations.

Figure 3.3 shows the energy saved using the simple optimizations presented in this section. The bar labeled "Original" refers to the un-optimized processor. In "Clock" only clock qualification is enabled. In "Selective" clock qualification and selective activation of the caches and register file are enabled. The numbers have been normalized to the energy of the fully optimized design. Thus simple optimizations can save almost 20%-25% of the total power. However further gains would be harder to come by because—as will be

shown later—the energy is dissipated in a variety of units, none of which accounts for a significant fraction of the total energy.

Figure 3.3: Reduction in energy from simple optimizations.

### 3.2.4 Energy and Energy-Delay Results

Figure 3.4 shows the energy and performance for the ideal super-scalar machine, the simple RISC machine, and TORCH. All figures in this sections have been normalized to the corresponding value for TORCH. As expected TORCH requires the most energy to execute a program, closely followed by the RISC processor. The difference in energy between the ideal machine and TORCH represents an upper bound on potential future improvements from eliminating waste. Since TORCH and the ideal super-scalar machine have identical execution models they have the same execution time. The super-scalar processors have a 1.35X speedup when compared to the single issue machine. With an ideal memory system the speedup would have been 1.6X. This highlights the importance of the external memory system, even in low-power applications. This topic is discussed in more detail in Section 3.4. TORCH and the simple RISC processor have nearly the same efficiency. Super-scalar issue provides a small gain in performance. Unfortunately it also increases the energy cost of all instructions. The net result is no significant improvement in energy-delay product.

Figure 3.4: Normalized energy and performance for RISC and TORCH.

We expect the power dissipation of the super-scalar processor core to be about 1W-2W at 100MHz in a 0.8µm technology.

The ideal super-scalar processor is roughly twice as efficient as the real machine. This means that no important sources of energy dissipation were overlooked in the idealized machines. In order to understand how to improve the efficiency of TORCH the next section looks at where the excess energy is dissipated.

## 3.3 Energy Breakdown

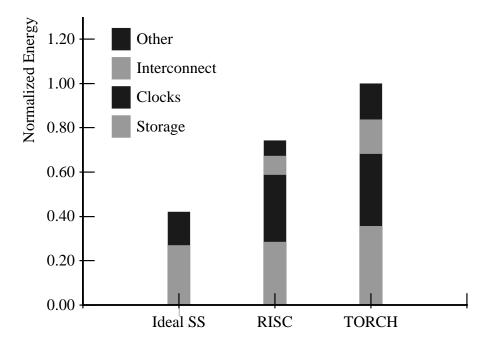

In this section the energy dissipation is broken down into four categories. The first is energy dissipated in reading and writing memories, such as the caches, and the register file. The second category is energy dissipated in the clock network. The third is energy dissipated in global interconnect nodes, such as the instruction bus, operand buses, and so on. The final category comprises everything not in one of the previous categories, and includes all control and data logic.

Figure 3.5 shows the energy breakdown for three of the five machines simulated. The figures have been normalized to the total energy dissipation of TORCH. The energy

dissipated in the on-chip memories is almost the same in the ideal machines and in our implementations. This means that the optimizations to reduce the number of unnecessary cache accesses were successful. The clock power in the real machines is slightly higher since there is a large amount of state that was not considered in the ideal machines. Although each storage element dissipates very little energy, the sum total represents a significant fraction. Global interconnect and computation each represent about 15% of the total energy. The most important point in this graph is that further improvements in energy-delay product will be hard to come by because the energy is dissipated in many small units. To reduce the energy significantly one would have to reduce the energy of many of these small units.

Figure 3.5: Energy breakdown for RISC and TORCH processors.

This section ignored the energy required to communicate with the external memory system and the energy dissipated in the external memories. Since such a large percentage of the energy is dissipated in the on-chip memories it is only natural to wonder how the energy and delay of the processor depend on the organization of the external memory hierarchy. The next section explores these tradeoffs.

# 3.4 Memory Hierarchy Design

The number of different ways to organize the memory system is almost unlimited, which explains the large number of papers related to memory hierarchy design. Przybylski [33] presents an excellent description of memory hierarchy design for high performance. This section extends that analysis to cover power as well as performance. This section describes the typical architecture of processor systems, followed by a description of the simulation methodology used. Then Section 3.4.3 explores how different memory system parameters affect the performance and power of the system.

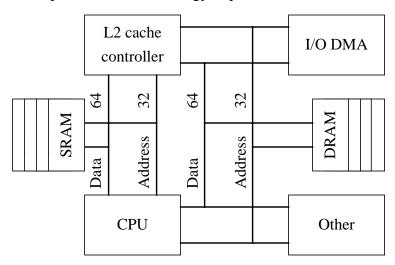

#### 3.4.1 System architecture

Processor systems are generally organized as shown in Figure 3.6. A fast bus connects the processor, second level cache (L2) and the cache controller (CC), although increasingly the cache controller is integrated with the processor. This bus usually operates at a high frequency (~100MHz), and requires special termination in order to guarantee signal integrity. Therefore the power dissipated to drive the bus can be significant, even if the total capacitance is not large. The processor, cache controller, and main memory are also connected to the main processor bus. Other chips, such as the I/O controller and memory controller that need to read or write main memory are also connected to the processor bus. The processor bus operates at only a fraction of the speed of the L2 bus. Due to the large loading on the main processor bus the energy required to drive it is also considerable.

Figure 3.6: Architecture of processor system.

Normally the first level cache (L1) is on the processor itself. Some systems contain only one level of caching. In this case the L2 cache and the L2 bus disappear. If present, the

second-level cache can be on- or off-chip. An external L2 cache is built using standard SRAM parts. The tag portion of the cache can be built using SRAM's or can be integrated with the processor. Main memory is built using standard DRAM chips. The caches are assumed to be write-back in order to reduce accesses to lower-levels.

#### 3.4.2 Simulation Methodology

In this section the processor is modeled as dissipating a fixed amount of energy per instruction executed. As was discussed earlier most of the energy is dissipated in essential functions that all instructions must perform, so differences in the energy dissipation of instructions are small. It is also assumed the processor on average executes 1.45 instruction every cycle. This corresponds to 0.688 cycles per instruction (CPI)—same as TORCH with a perfect memory system. The actual CPI of the processor is the base CPI plus the average CPI contribution due to the memory hierarchy.

A trace-driven simulator [34] was used to find the miss rate of the SPECint92 benchmarks on a particular memory organization. The timing model presented by Wilton and Jouppi [35] is used to find the access time of the on-chip caches. It is assumed that the cycle time of the processor is the maximum of a base number (7ns) or the access time of the L1 cache. For most processors accessing the instruction and data caches are two of the critical paths. Increasing the size of the caches decreases the maximum operating frequency. Only for very small sized caches is the cycle time limited by other logic on the processor. The model presented by Amrutur [16] and described in Appendix B is used to find the energy dissipation of on-chip caches. The access time of external components (L2 and main memory) is set by the access time of the chips, plus some overhead to do processing.

Table 3.1 and Table 3.2 describe important characteristics of the SRAM and DRAM chips used to built L2 and main memory. The simulated DRAM's are extremely fast in order to make the simulations conservative. Since DRAM power is specified as a constant  $I_{DD}$  current while the part is active reducing the access and cycle time reduces the energy dissipation per access. Furthermore, it reduces the processor performance degradation that is due to the memory system. One very important consideration is how the DRAM chips are accessed. To build a 32-bit wide memory, it is possible to access 4 8-bit wide chips or 8 4-bit wide chips (ignoring parity for this example). Part of the energy dissipated in accessing a DRAM is fixed overhead, and the remainder is linearly dependent on the number of bits read. The overhead is due, among other things, to DRAM's reading thousands of bits during the row access (RAS). These bits are held in the sense amplifiers

and are then driven off-chip during column access (CAS). Increasing the access width will amortize the overhead over a larger number of bits, reducing the energy dissipation. The increasing size of DRAM chips also encourages designers to use wider DRAM's because it allows the user to add main memory in smaller increments.

| Manufacturer             | Cypress                              |

|--------------------------|--------------------------------------|

| Size                     | 1Mbit (64K x 18)                     |

| Active $I_{DD}$ current  | 265mA                                |

| Standby $I_{DD}$ current | 20mA                                 |

| Access width             | 18 bits (16 bits data, 2 bit parity) |

| Pad capacitance          | 5pF                                  |

| Access time              | 10ns                                 |

| Miss time                | 6 cycles                             |

Table 3.1: Summary of SRAM characteristics.

In Table 3.1 miss time refers to the number of processor cycles from the moment the L1 cache detects a miss until the second level cache returns the first word. The transfer time depends on the line size.

| Manufacturer             | NEC              |

|--------------------------|------------------|

| Size                     | 16Mbit (1M x 16) |

| RAS time                 | 60ns             |

| CAS time                 | 40ns             |

| Active $I_{DD}$ current  | 170mA            |

| Refresh $I_{DD}$ current | 170mA            |

| Standby $I_{DD}$ current | 110μΑ            |

| Access width             | 16 bits          |

| Pad capacitance          | 5pF              |

| Access time              | 100ns            |

| Miss time                | 19 cycles        |

Table 3.2: Summary of DRAM characteristics.

In Table 3.2 miss time refers to the number of processor cycles from the moment the processor detects a miss until it receives the first word from the DRAM.

The results shown below ignore the energy dissipated in the DRAM refresh. Although the  $I_{DD}$  current during refresh is comparable to the active  $I_{DD}$  current, time spent doing refresh is much smaller than the time spent in active mode. The refresh power is in the order of 10mW, which is much smaller than the access power. One needs to worry about the refresh energy only when the processor is idle for extended periods of time but the DRAM's are not in standby mode.

For these simulations it was assumed the L2 bus uses series termination such that the energy dissipation can be modeled as  $1/2CV^2$ . Using series-parallel termination would add 10mW-40mW of power to the bus, due to short-circuit paths between supply and ground. Using parallel termination would add a fraction of that power, depending on how often the driver pulls against the resistor. Assuming a random distribution half the cycles would have static current, so the additional power would be 5mW-20mW. For comparison the dynamic power of a 50pF capacitor at 100MHz is in the order of 15mW, assuming random distribution of inputs. The power dissipation of the processor bus is also modeled as  $1/2CV^2$ . The capacitance of the bus depends on how many chips are connected to it because pads are a significant source of capacitance. For these simulation it is assumed the processor, all the memory chips, and two more devices are attached to the bus. The capacitance of the bus also depends on the physical length of bus. PCB traces have a capacitance of approximately 1.25pF/cm of length. The bus is assumed to be 20cm long. The total capacitance of the bus is 125pF/cm

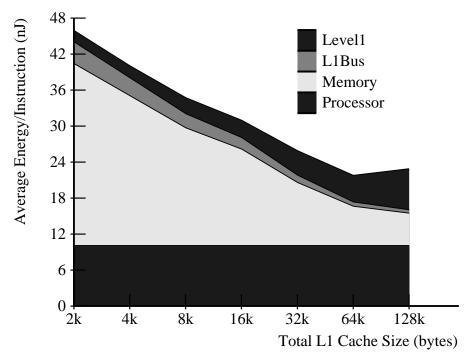

## 3.4.3 Energy and Performance Tradeoffs

Figure 3.7 shows the average energy per instruction dissipated in the external memory hierarchy broken up into the different components, as the combined (instruction plus data) size of the first level cache increases. The energy dissipated in the processor is also shown. The instruction and data caches are of equal size. There is no second level cache. The main point to notice is that DRAM's dissipate large amounts of energy per access. Therefore small caches are inefficient because main memory must be accessed often. As the size of the first level cache increases the DRAM's are accessed less frequently. It is not until the first level cache is relatively large (32K) that the energy dissipation of the DRAM's becomes comparable to that of the first level cache. Having a small cache does not only affect the energy dissipation, it also affects the performance. As the size of the

first level cache increases, the miss rate decreases. Figure 3.8 shows a plot of the energy-delay product for the same memory hierarchy. Most of the change in energy-delay comes from a lower CPI due to a lower miss rate. Ideally as the cache size increases the energy-delay should decrease quadratically. But this ignores the fact that the cycle time of the processor changes as the L1 cache size changes. If the cache is small increasing the size increases the performance because the performance gain due to lower miss rate is larger than the performance lost due to slower cycle time. As the miss rate curve flattens out, increasing the cache size results in decreased performance. The other drawback of increasing the cache size is that the die area and on-chip power increase. For many applications die area and power are tightly constrained—for example power must be less than 1W-1.5W if the processor is to be sold in a plastic package. In this case system efficiency must be traded off for lower processor cost.

Figure 3.7: Energy breakdown for single level hierarchy.