# HIGH PERFORMANCE INTER-CHIP SIGNALLING

**Stefanos Sidiropoulos**

**Technical Report No. CSL-TR-98-760**

**April 1998**

This research has been supported by ARPA contract DABT63-94-C-0054.

#### HIGH PERFORMANCE INTER-CHIP SIGNALLING

#### **Stefanos Sidiropoulos**

**Technical Report: CSL-TR-98-760**

**April** 1998

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

Stanford, California 94305-4055

#### **Abstract**

The achievable off-chip bandwidth of digital IC's is a crucial and often limiting factor in the performance of digital systems. In intra-system interfaces where both latency and bandwidth are important, source-synchronous parallel channels have been adopted as the most effective solution. This work investigates receiver and clocking circuit design techniques for increasing the signalling rate and robustness of such channels.

One of the main problems arising in the reception of high speed signals is the adverse effects of high frequency noise. To alleviate these effects, a new class of receiver structures that utilize current integration is proposed. The integration of current on a capacitor based on the incoming signal polarity effectively averages the signal over its valid time period, therefore filtering out high frequency noise. An experimental transceiver prototype utilizing current integrating receivers was designed and fabricated in a 0.8 µm CMOS technology. The prototype achieves a signaling rate of 740 Mbps/pin operating from a 3.3-V supply with a bit error rate of less than  $10^{-14}$ .

The second major challenge of inter-chip communication is the design of clock generation and synchronization circuits. Delay locked loops are an attractive alternative to VCO-based phase locked loops due to their simpler design, intrinsic stability, and absence of phase error accumulation. One of their main problems however is their limited phase capture range. A dual loop architecture that eliminates this problem is proposed. This architecture employs a core loop to generate finely spaced clock edges, which are then used by a peripheral loop to generate the output clock through phase interpolation. Due to its digital control, the dual loop can offer great flexibility in the implementation of phase acquisition algorithms. A dual DLL prototype was fabricated in a 0.8 µm CMOS technology. The prototype achieves 80KHz-400MHz operating range, 12-ps rms jitter and 0.4-ps/mV jitter supply sensitivity.

**Key Words and Phrases:** High Speed Signalling, Receivers, Delay Locked Loops

Copyright © 1998

by

Stefanos Sidiropoulos

## Acknowledgments

This work would not have been possible without the help and support of many people.

First, I would like to thank my advisor Prof. Mark Horowitz. There way too many things I could say to thank Mark. Instead of restating well known facts, I will just say that I really feel that I could not have had a better advisor. It has really been a privilege working with him these past years.

I would also like to thank Prof. Tom Lee for discussing many of my ideas, and for reading this thesis along with my associate advisor Prof. Kunle Olukotun. Thanks also are due to Prof. Bruce Lusignan who served in my orals examination committee, along with Prof. Bruce Wooley who also proofread many of my papers. I am also grateful to Dr. Norm Jouppi and Mark Johnson for being a source of technical information and criticism, and to my M.Sc. advisor Prof. Manolis Katevenis and Prof. Fouad Tobagi for being the original reason I came to Stanford.

I also want to acknowledge ARPA for their financial support, DEC-WRL for allowing me to do part of my research while working there over a summer, and the people at Rambus who helped me finish writing this dissertation in the middle of a tape-out.

It has been a real pleasure to work with the staff of both the Center for Integrated Systems and the Computer Systems Laboratory at Stanford. In particular I am grateful for the technical support of Charlie Orgish, and the administrative support of Darlene Hadding, Ann Guerra and Terry West.

My time at Stanford has been a memorable experience. This is mainly due to the interaction I had with other graduate students. In particular I would like to thank Ken Yang for our collaboration on the chip described in the third chapter of this thesis, Sha Rabii and Marc Loinaz for being the ideal office-mates providing me both with technical advise and friendship, and Birdy Amrutur, Ricardo Gonzalez, Hesham Al-Twaijry, and Gu Wei for being there to discuss and challenge my ideas. I am also grateful to John Maneatis, Tom Chanak, Don Ramsey, Clem Portmann, and Drew Wingard for helping me in my early years of research. John, Tom and Don were particularly instrumental in convincing me to

join Mark Horowitz's group – a decision I will never regret. Drew left me with the mixed blessing of supporting the VLSI CAD environment at Stanford – a decision I will never regret as well.

It is certainly impossible to find appropriate words to thank my wife Lena Tsakmaki. I would not have completed this effort without her, and so this thesis – for all it's worth – is dedicated to her..

# **Table of Contents**

| Acknowledgments                               |     |

|-----------------------------------------------|-----|

| Table of Contents                             | v   |

| List of Tables                                | vii |

| List of Figures                               | ix  |

| Chapter 1 Introduction                        | 1   |

| 1.1 Motivation                                | 1   |

| 1.2 Overview of this work                     | 3   |

| Chapter 2 Signalling and Clocking             | 5   |

| 2.1 Limitations of Conventional Busses        | 6   |

| 2.2 Source Synchronous Interfaces             | 8   |

| 2.2.1 High Speed Busses                       | 9   |

| 2.2.2 Point to Point Links                    | 10  |

| 2.3 Noise Considerations                      | 12  |

| 2.4 Signalling Methods                        | 16  |

| 2.4.1 Low Impedance Signalling                |     |

| 2.4.2 High Impedance Signalling               |     |

| 2.5 Clocking Methods                          | 24  |

| 2.6 Summary                                   | 28  |

| Chapter 3 Source Synchronous Interface Design | 29  |

| 3.1 Signalling Circuits                       | 30  |

| 3.1.1 Line Driver Design                      | 31  |

| 3.1.2 Receiver Design                         | 35  |

| 3.2 Clocking Circuits                         | 36  |

| 3.2.1 Delay Locked Loop Design                | 37  |

| 3.2.2 Duty Cycle Adjuster Design              | 41  |

| 3.3 Experimental Results                      | 43  |

| 3.4 Summary                                   | 46  |

| Chapter 4 Current Integrating Receivers               | 49  |

|-------------------------------------------------------|-----|

| 4.1 Reference Noise in Pseudo-Differential Signalling | 50  |

| 4.2 Concept of Operation                              | 54  |

| 4.3 Circuit Design                                    | 59  |

| 4.3.1 Current Integrator Design                       | 61  |

| 4.3.2 Charge Injection Offset Cancellation            | 64  |

| 4.3.3 Current Integrator Biasing                      | 68  |

| 4.3.4 Amplifier and Latch Design                      | 70  |

| 4.4 An Interface Using Current Integrating Receivers  | 71  |

| 4.4.1 Clocking Circuits                               | 73  |

| 4.4.2 Peripheral Circuits                             | 77  |

| 4.5 Experimental Results                              | 78  |

| 4.6 Summary                                           | 82  |

| Chapter 5 Dual Interpolating Delay Locked Loop        | 85  |

| 5.1 Loop Architecture                                 | 86  |

| 5.1.1 Dual Delay Locked Loop Architecture             | 91  |

| 5.1.2 Dual Loop Dynamics                              | 93  |

| 5.2 Circuit Design                                    | 97  |

| 5.2.1 Core Delay Locked Loop                          | 99  |

| 5.2.2 Phase Interpolator                              | 102 |

| 5.2.3 Peripheral Loop Control                         | 108 |

| 5.3 Experimental Results                              | 112 |

| 5.4 Summary                                           | 116 |

| Chapter 6 Conclusion                                  | 117 |

| 6.1 Future Work                                       | 118 |

| Deferences                                            | 121 |

# **List of Tables**

| Table 4-1: | Performance summary of the prototype transceiver | 83  |

|------------|--------------------------------------------------|-----|

| Table 5-1: | Performance summary of the prototype DLL         | 116 |

# **List of Figures**

| Figure 2.1:  | Conventional bus block diagram                                       | 6      |

|--------------|----------------------------------------------------------------------|--------|

| Figure 2.2:  | High speed bus block diagram                                         | 10     |

| Figure 2.3:  | Point to point parallel link                                         | 11     |

| Figure 2.4:  | Model of a low impedance series-terminated signalling system         | 17     |

| Figure 2.5:  | Alternative implementations of low impedance, series-terminated s    | ignal- |

|              | ling                                                                 | 19     |

| Figure 2.6:  | Model of a high impedance parallel-terminated signalling system      | 22     |

| Figure 2.7:  | Alternative implementations of low impedance, series-terminated s    | ignal- |

|              | ling                                                                 | 23     |

| Figure 2.8:  | Optimal sampling point and timing margins                            | 25     |

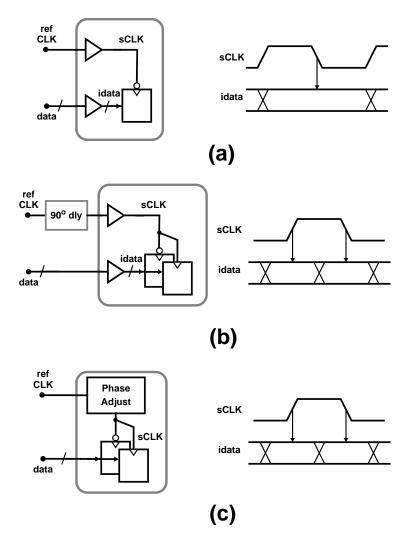

| Figure 2.9:  | Receiver clocking alternatives                                       | 26     |

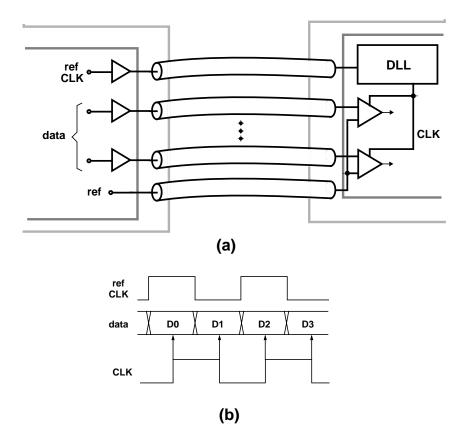

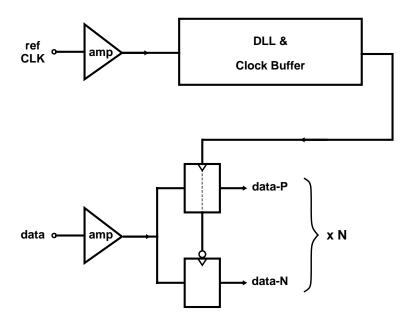

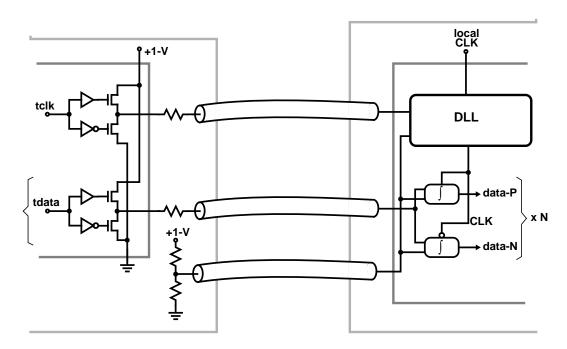

| Figure 3.1:  | Interface block diagram (a), and timing (b)                          | 30     |

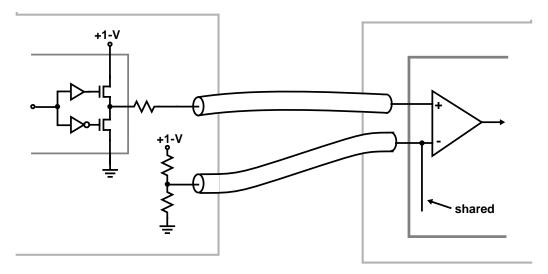

| Figure 3.2:  | Interface signalling scheme                                          | 31     |

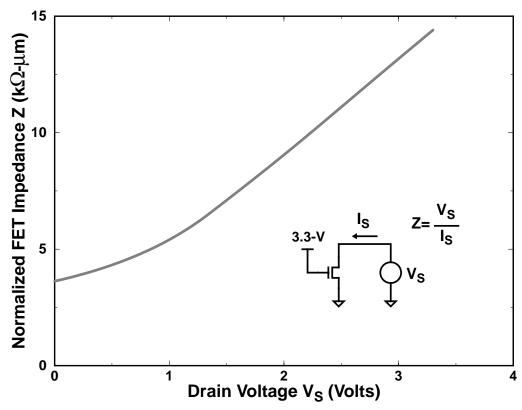

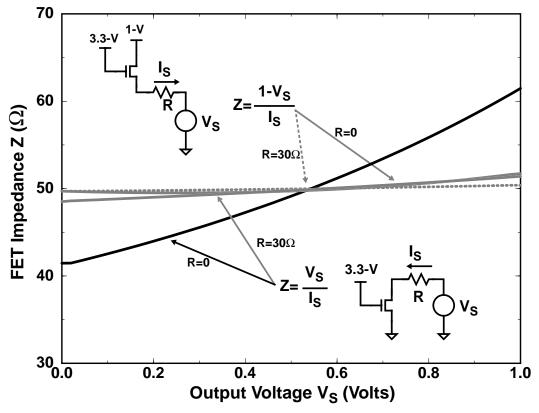

| Figure 3.3:  | Large signal impedance of full-swing driver                          | 32     |

| Figure 3.4:  | Large signal impedance of low-swing driver                           | 34     |

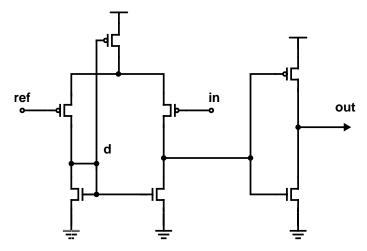

| Figure 3.5:  | Input receiver schematic diagram                                     | 35     |

| Figure 3.6:  | Simplified receiver block diagram                                    | 36     |

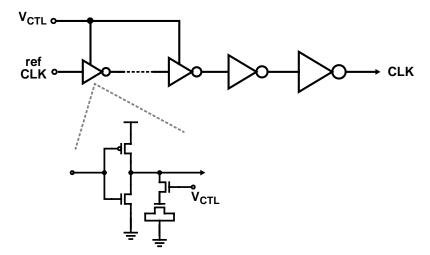

| Figure 3.7:  | Delay line schematic                                                 | 37     |

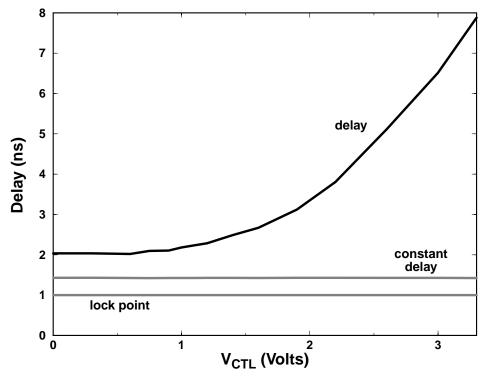

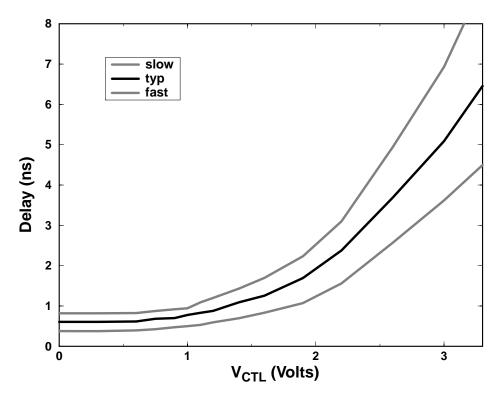

| Figure 3.8:  | Simulated delay line transfer function                               | 38     |

| Figure 3.9:  | Simulated delay line effective transfer function                     | 38     |

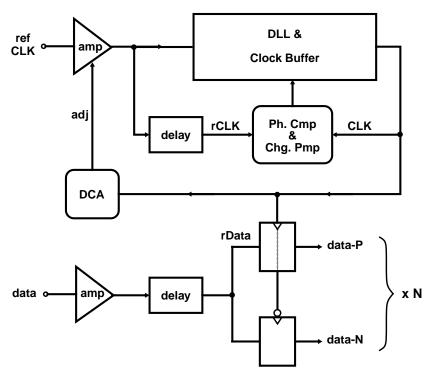

| Figure 3.10: | Detailed block diagram of the receiver                               | 39     |

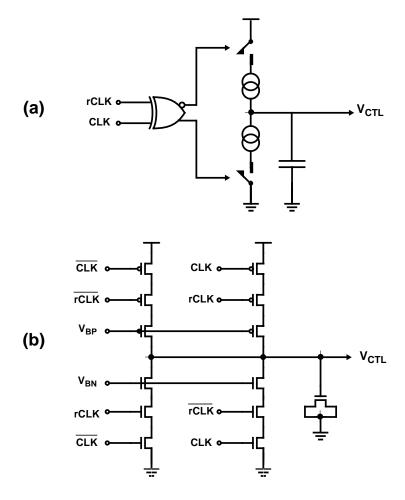

| Figure 3.11: | Phase detector: (a) conceptual diagram, and (b) implementation       | 41     |

| Figure 3.12: | Duty cycle adjuster schematic                                        | 42     |

| Figure 3.13: | Chip photomicrograph                                                 | 43     |

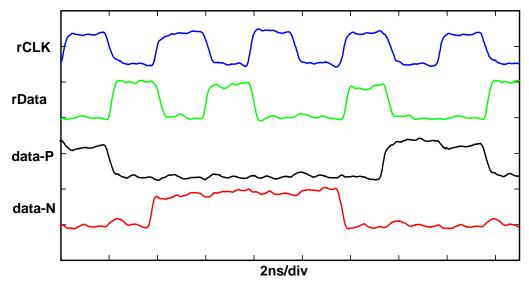

| Figure 3.14: | Received signal waveforms at 500 Mbps/pin                            | 44     |

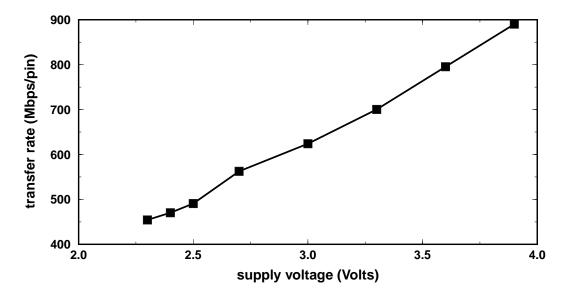

| Figure 3.15: | Prototype operating range                                            | 45     |

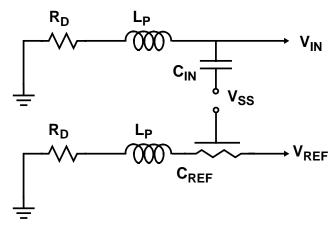

| Figure 4.1:  | Simplified noise injection model in a pseudo-differential interface  | 51     |

| Figure 4.2:  | Reference and input signal frequency response to on-chip supply nois | se52   |

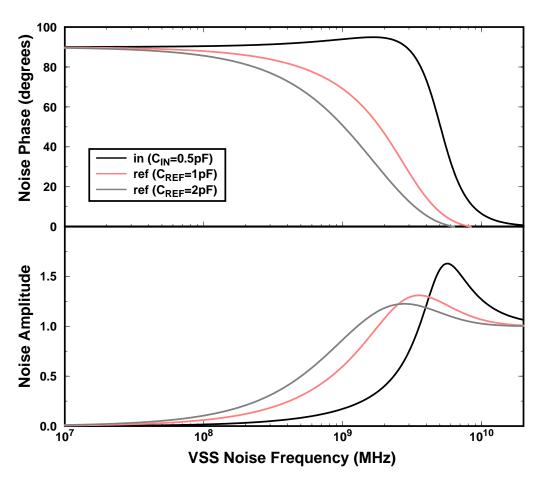

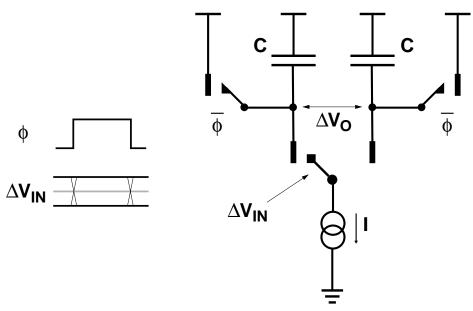

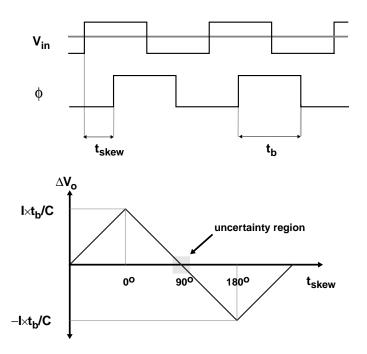

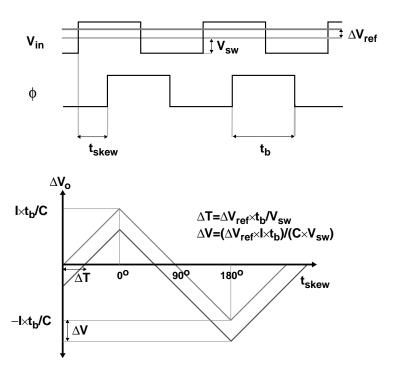

| Figure 4.3:  | Ideal current integrating receiver                                   | 55     |

| Figure 4.4:  | Ideal current integrating receiver phase characteristics             | 56     |

| Figure 4.5:  | Integrate-and-dump filter phase characteristics                      | 57     |

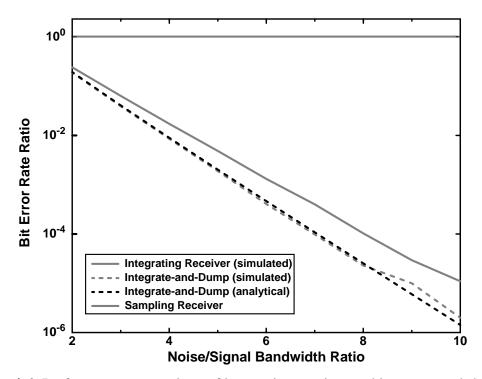

| Figure 4.6:  | Performance comparison of integrating receiver and integrate-and-    | dump   |

|              | filter                                                               | 58     |

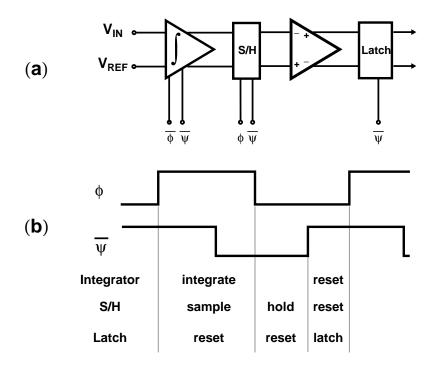

| Figure 4.7:  | Receiver block diagram and timing                                    | 60     |

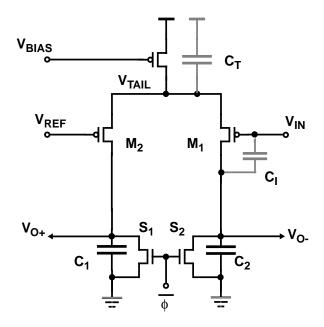

| Figure 4.8:  | CMOS current integrator schematic                                       | 61    |

|--------------|-------------------------------------------------------------------------|-------|

| Figure 4.9:  | Effect of charge injection in the integrator characteristics            | 63    |

| Figure 4.10: | Initial current integrator implementation                               | 64    |

| Figure 4.11: | Phase characteristics of the initial integrator implementation          | 65    |

| Figure 4.12: | Improved integrator implementation.                                     | 66    |

| Figure 4.13: | Phase characteristics of the improved integrator implementation         | 67    |

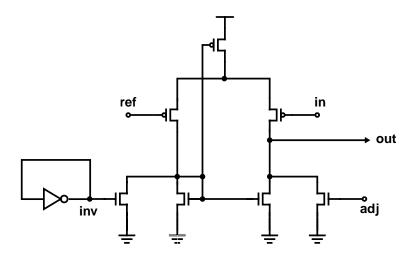

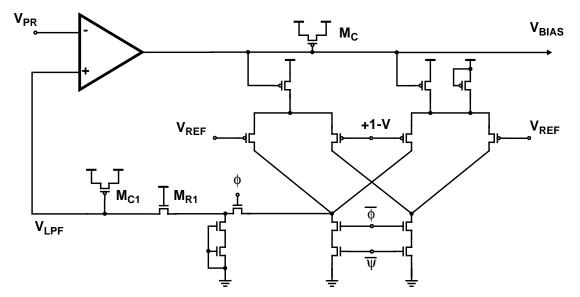

| Figure 4.14: | Current integrator replica-feedback biasing circuit.                    | 68    |

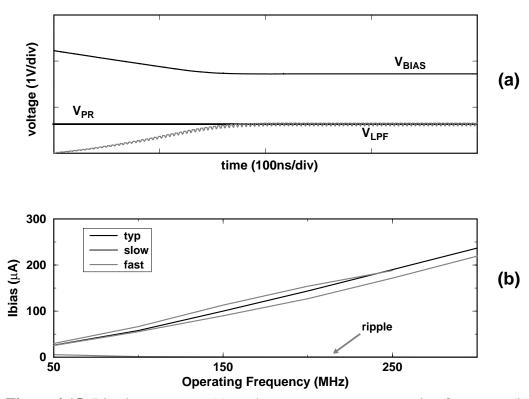

| Figure 4.15: | Bias loop start-up (a), and output current vs. operating frequency (b). | 69    |

| Figure 4.16: | Amplifier and latch schematic                                           | 70    |

| Figure 4.17: | Interface block diagram                                                 | 71    |

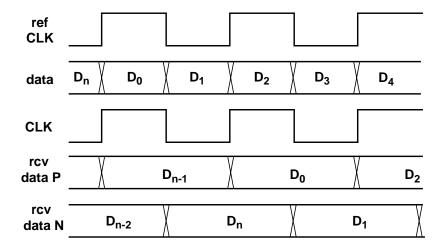

| Figure 4.18: | Timing of the interface signals                                         | 72    |

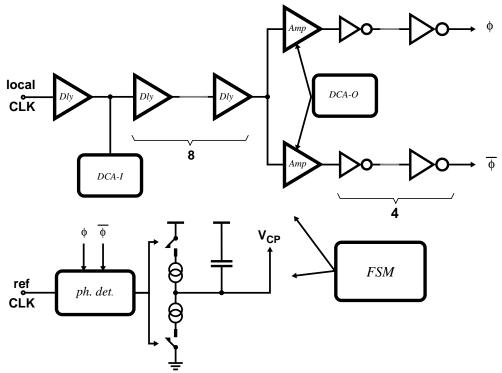

| Figure 4.19: | DLL block diagram                                                       | 74    |

| Figure 4.20: | Delay element schematic                                                 | 75    |

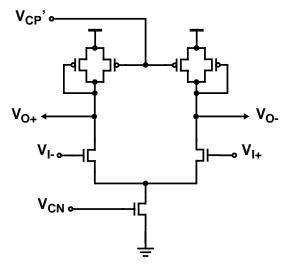

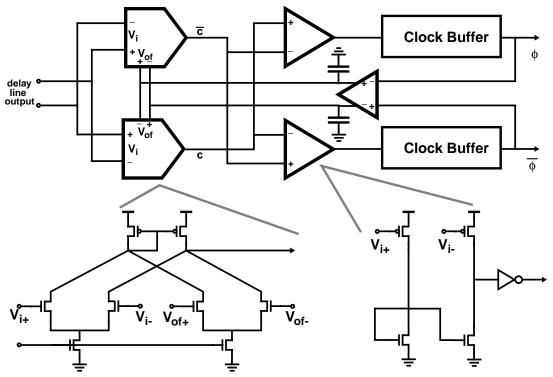

| Figure 4.21: | Output DCA schematic                                                    | 77    |

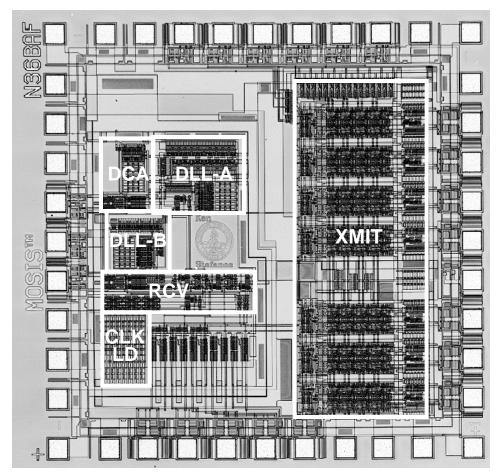

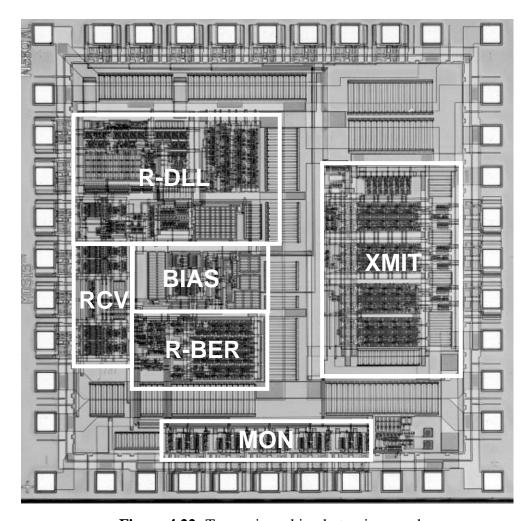

| Figure 4.22: | Transceiver chip photomicrograph                                        | 79    |

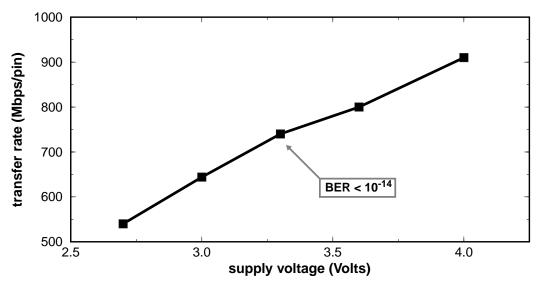

| Figure 4.23: | Prototype operating range                                               | 80    |

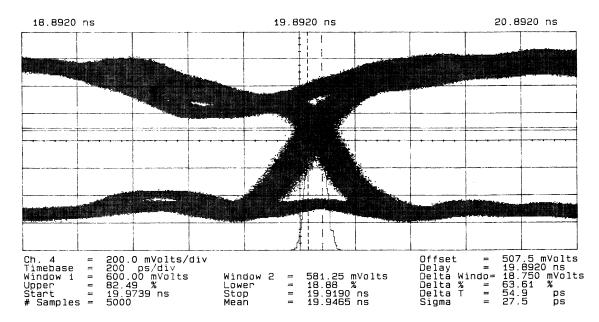

| Figure 4.24: | Received data eye diagram                                               | 81    |

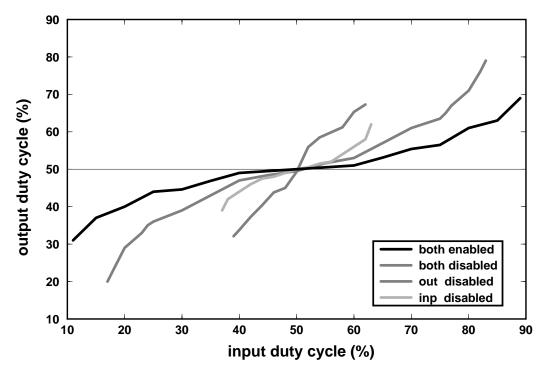

| Figure 4.25: | Duty cycle adjuster effectiveness                                       | 82    |

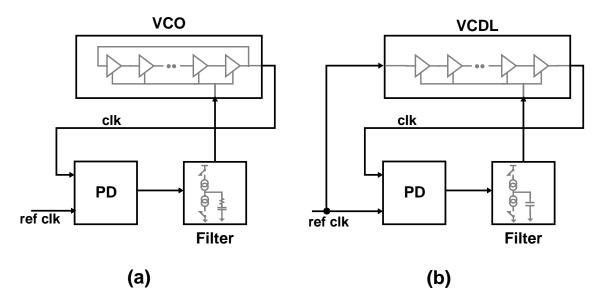

| Figure 5.1:  | Phase locked loops (a), and Delay locked loops (b)                      | 87    |

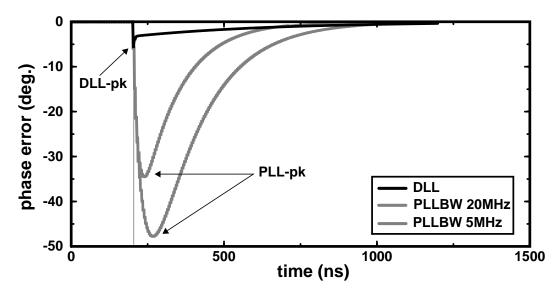

| Figure 5.2:  | Simulated supply step response of a PLL and DLL                         | 89    |

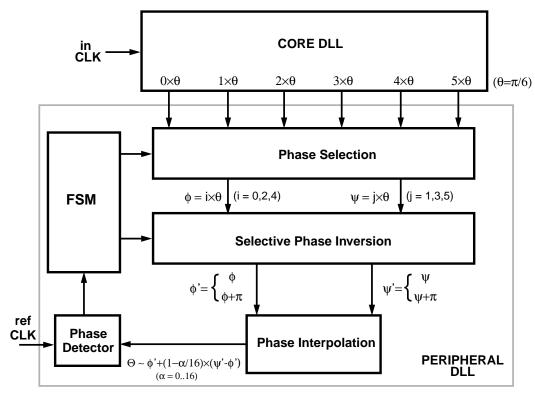

| Figure 5.3:  | Dual interpolating DLL architecture                                     | 92    |

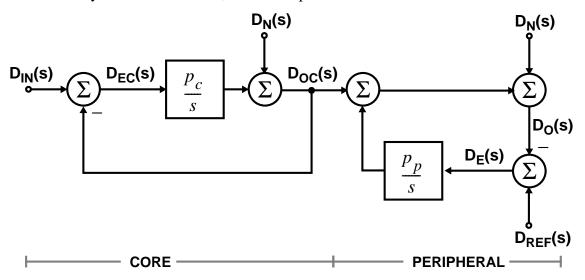

| Figure 5.4:  | Linearized dual DLL model                                               | 94    |

| Figure 5.5:  | Dual loop step-response to: change in clock period (a), and supply      | noise |

|              | (b)                                                                     | 96    |

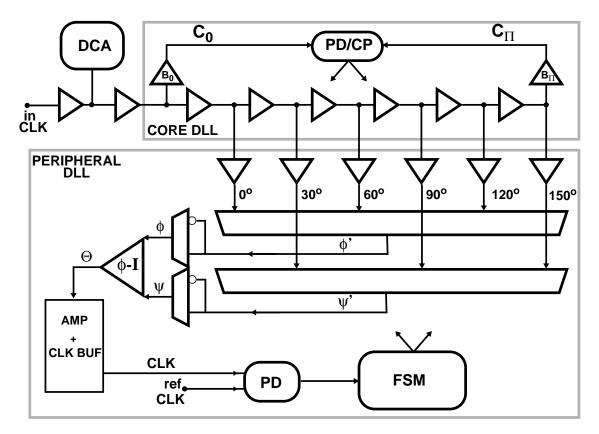

| Figure 5.6:  | Dual DLL block diagram                                                  | 98    |

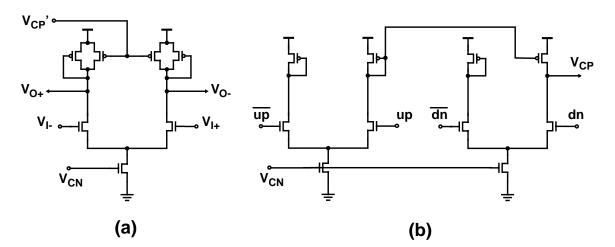

| Figure 5.7:  | Core loop delay buffer (a), and charge-pump (b)                         | 99    |

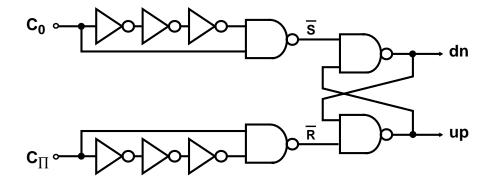

| Figure 5.8:  | Core loop linear phase detector                                         | 101   |

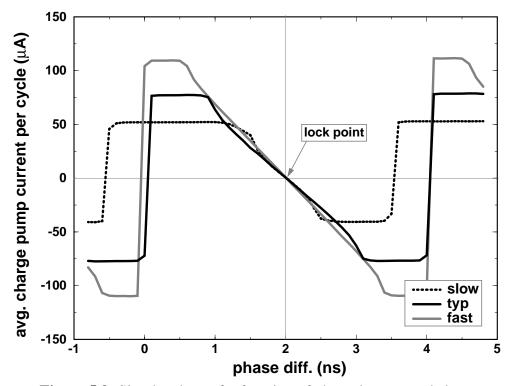

| Figure 5.9:  | Simulated transfer function of phase detector and charge pump           | 102   |

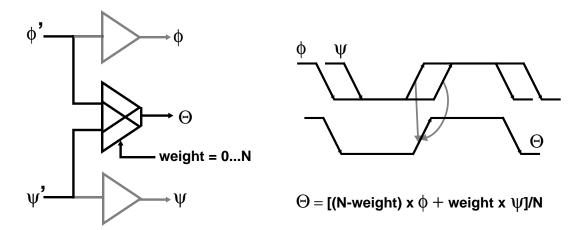

| Figure 5.10: | Timing generation using phase interpolators                             | 103   |

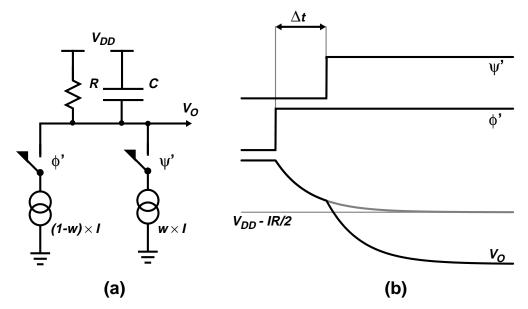

| Figure 5.11: | Simplified model of the phase interpolator                              | 104   |

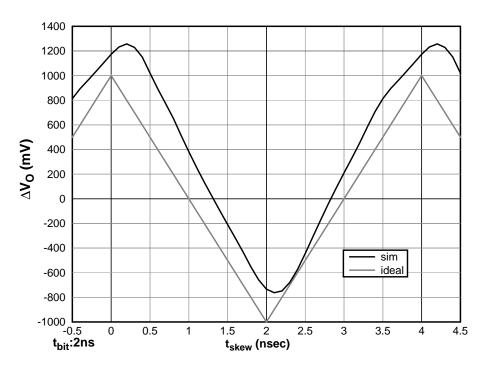

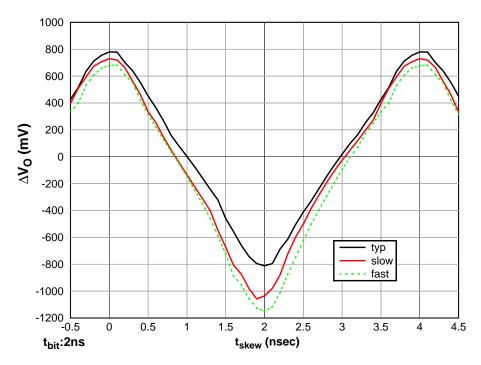

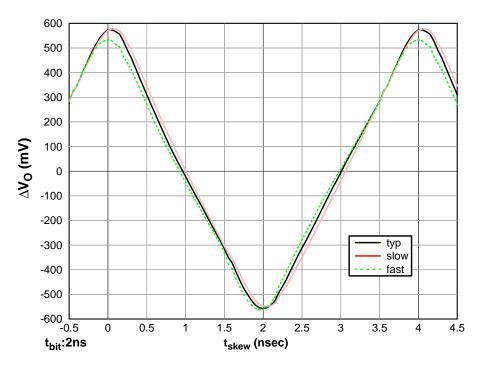

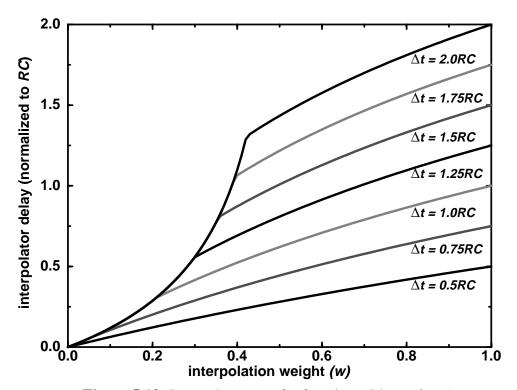

| Figure 5.12: | Interpolator transfer function with varying Δt                          | 105   |

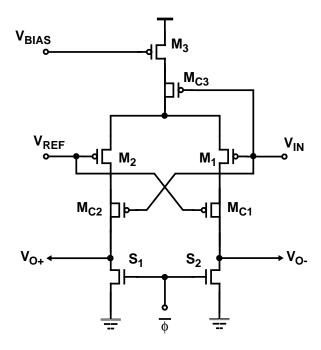

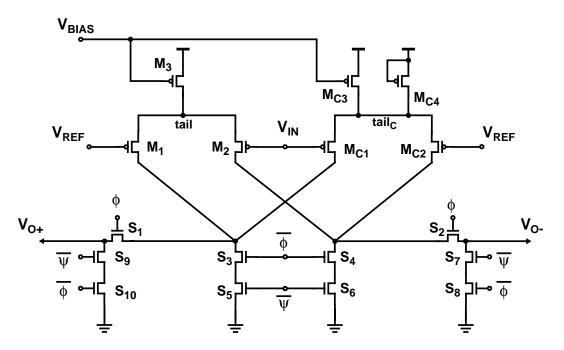

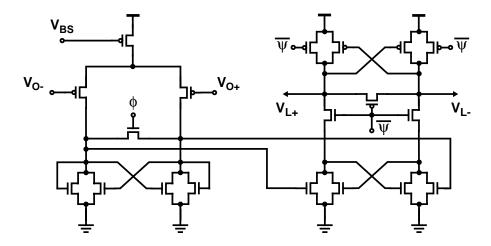

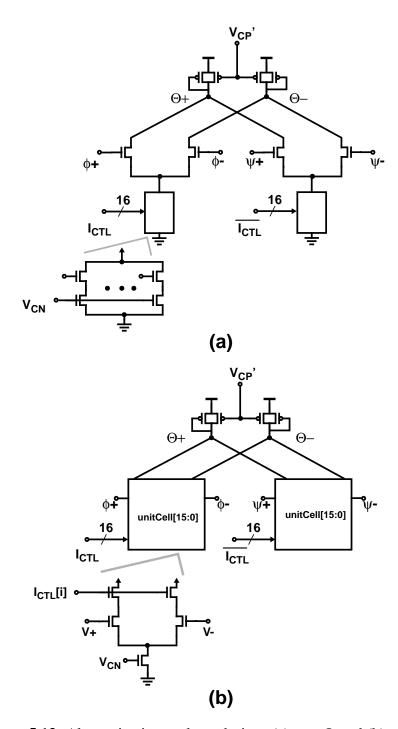

| Figure 5.13: | Alternative interpolator designs (a) type-I, and (b) type-II            | 106   |

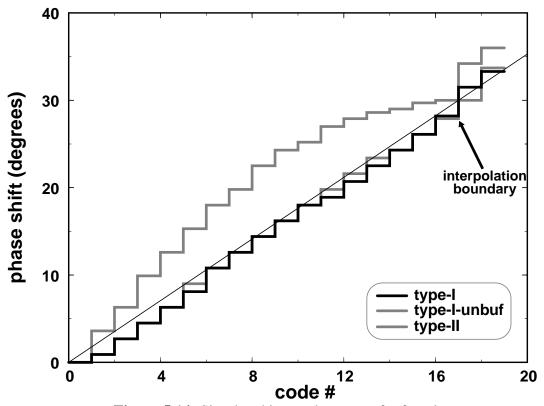

| Figure 5.14: | Simulated interpolator transfer function                                | 107   |

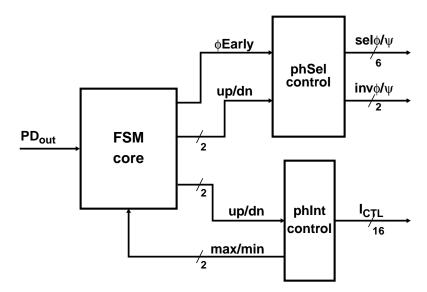

| Figure 5.15: | Peripheral loop controller block diagram                                | 108   |

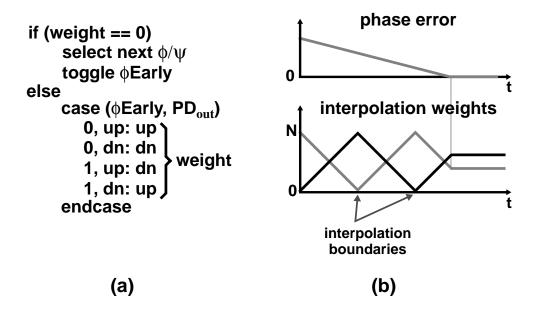

| Figure 5.16: | Simplified FSM algorithm (a) and resulting loop behavior (b)            | 109   |

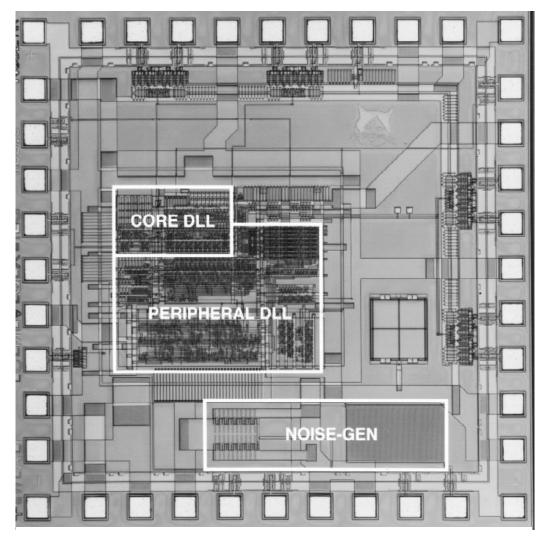

| Figure 5.17: | Prototype chip photomicrograph                                          | 112   |

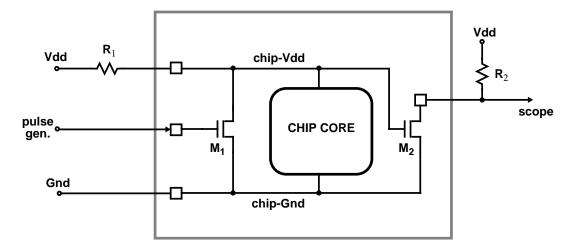

| Figure 5.18: | Noise generation and monitoring circuits                                | 113   |

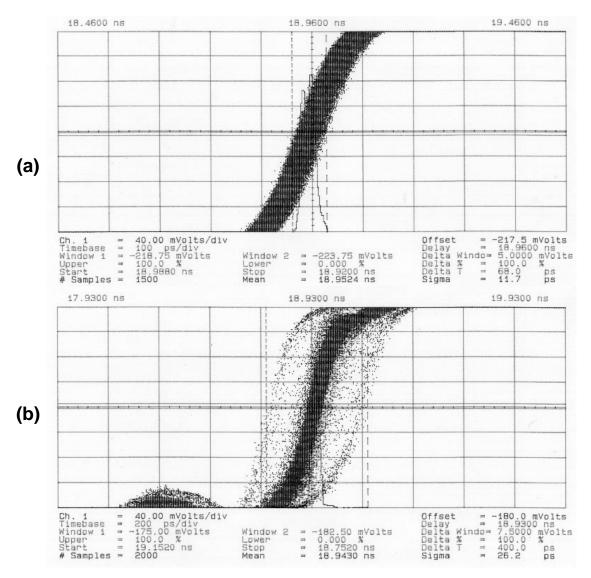

| Figure 5.19: | Jitter histogram with: (a) quiet, and (b) noisy supply                  | 114   |

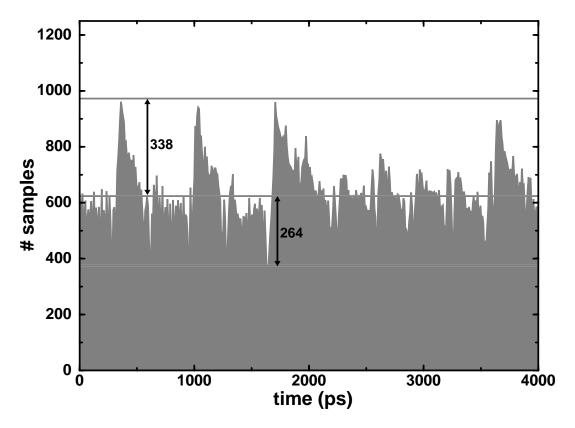

| Figure 5.20: | Clock histogram with continuously rotating clock                        | 115   |

## Chapter 1

## Introduction

#### 1.1 Motivation

Advances in IC fabrication technology coupled with aggressive circuit design have led to an exponential growth of the speed and integration levels of digital IC's. In order for these improvements to truly benefit the overall system performance, the communication bandwidth between IC's must scale accordingly. Rent, in his 1960 memorandum [1]-[3] related the gate count of a digital system (Ng) to its external interconnections (Np) in a formula which came to be known as Rent's rule:

$$Np = Kp Ng^{\beta} \tag{1-1}$$

where  $\beta$  and Kp are empirically determined constants. Regardless of the absolute accuracy with which Rent's formula can predict the pin count of future IC's, its main implication is that *in order to maintain a balanced system the communication I/O bandwidth of IC's must scale with integration levels*. This thesis examines the problems associated with the design of high-bandwidth interfaces, and proposes techniques for increasing their speed and robustness while maintaining low latency and system cost.

Traditionally, system designers have addressed the increasing bandwidth demands by increasing the number of pins and wires interconnecting digital IC's. So it is not uncommon today, to have 128-bit wide busses in high-end workstation systems, and gate-array IC's packaged in 1000-pin ball grid arrays. However, this bandwidth improvement does

not come for free. Increased number of pins, printed-circuit-board (PCB) traces, connectors, and cables drive up the overall system cost. To minimize that cost, designers need to maximize the bandwidth of the data that can be transmitted per low-cost IC pin. Moreover, in many applications communication latency must be kept to a minimum, in order for the bandwidth increase to really benefit the system performance.

There are two main approaches to high-speed signalling. In serial interconnects, such as those used in local area networks, data is transmitted from one IC to another in a plesiochronous manner [4]. The receiving IC has to recover the clock encoded in the data transitions, and retime the data to its local clock. The main design goal in these systems is to increase the data transfer rate. The latency added into the system by the clock and data recovery circuits is a secondary concern, since the overall latency is usually dominated by the communication channel delay. Additionally, since serial links are not replicated in large numbers and usually employ a fiber optic based channel, the incremental circuit cost is not a major concern. So, this increased cost and latency imposed by the required clock recovery and data retiming circuits [5]-[10], make serial links more applicable to inter-system interconnects such as communication links between two computer systems.

High-speed parallel links are an alternative more amenable to interconnections within a single system, such as a workstation, a supercomputer, or a network switch [11]-[15]. The operation of these links derives from the conventional bus paradigm. Timing information is carried from one IC to another by means of a separate signal line, or alternatively, both IC's synchronize to a global system clock. The common timing is then used by the receiving IC to sample the data carried over a number of parallel channels. In this way, the cost of the extra timing line and the associated phase adjusting circuitry is amortized over a number of data lines. Since many of these parallel links need to be integrated within a single system, the overall overhead (area, power, latency) of the increased communication bandwidth is a key constraint. These constraints dictate a simpler design for the driver and receiver circuits and lower bandwidth per communication channel, when compared to serial links. It is these types of circuits that this thesis focuses on. Although the majority of this work was done with the particular application of multiprocessor interconnection networks in mind, the resulting techniques are general enough and can be applied directly to

other application areas, such as high bandwidth processor to memory interfaces [11], and high bandwidth communication switching systems [16].

#### 1.2 Overview of this work

This thesis comprises six chapters of which this introduction is the first. Since system interface design has been addressed and studied extensively, Chapter 2 starts with an overview of parallel interface architectures, namely conventional multi-drop busses, and higher speed "source-synchronous" busses and parallel point-to-point links. Since some of the main limitations of the achievable bandwidth in existing designs are imposed by the system environment, the chapter continues by reviewing noise introduced both by transmission media and active circuits. The chapter concludes with an overview of signaling and synchronization methods.

A baseline high-speed interface design is the topic of Chapter 3. The trade-offs involved in the design of the signalling circuits, input receivers, and clocking circuits are described, along with the results obtained from a fabricated prototype [15]. The limitations of this simple design were the main motivation for the receiver and clocking circuits discussed in Chapters 4 and 5

One of the main limitations of existing parallel interface designs is that low swing, high speed signals have to be received in the noisy environment of a digital chip. The noise coupling becomes even worse in the most economical class of pseudo-differential interfaces. In these systems the maximum achievable bandwidth is limited by high frequency noise and by the fact that the high speed data is sampled only once per valid-bit period. Chapter 4 proposes a receiver design which integrates the incoming data over its valid time period, effectively filtering out high frequency noise [17], [18], [19]. The circuit design issues of the first stage integrator along with its associated biasing and sampling issues are discussed next. The chapter concludes with the description of a complete interface design utilizing current integrating receivers and the experimental results measured on a prototype fabricated in a 0.8-µm CMOS technology.

#### 1.2 Overview of this work

Another important issue is the design of clock phase alignment circuits which are necessary to generate the timing events used in the reception of the high speed signals. Chapter 5 addresses the design of these circuit blocks. A class of circuits known as Delay-Locked Loops (DLL's) offers many advantages over more conventional Voltage Controlled Oscillator (VCO) based Phase Locked Loops (PLL's). The main limitation of DLL's is their limited phase capture range. A new dual DLL architecture that eliminates this problem, while keeping the clock jitter and offset low is proposed. The implementation of the circuit building blocks and the results from a fabricated prototype are also discussed [20], [21].

The final chapter summarizes the contributions of this work and discusses areas of further development.

## Chapter 2

## **Signalling and Clocking**

This work focuses on circuits and architectures for high performance parallel links. In order to provide a framework for understanding the trade-offs and issues behind them, this chapter provides an overview of high speed interface design. The two main issues in extending the bandwidth of interconnections between system components are: (i) signalling - i.e., sending and receiving high speed data in the presence of digital system noise, and (ii) clocking - i.e., synchronizing the system so that the receivers and transmitters send and sample the data at the right time instant. These two issues are the topic of this chapter.

Section 2.1 discusses the structure and functionality of the ubiquitous bus-based systems, along with the signal integrity and timing uncertainty problems that impede the scaling of their transfer rates. Source synchronous systems mitigate the signalling and synchronization problems of conventional busses by constraining both the physical dimensions and the signal flow on the communication medium. The architecture of these systems is discussed in Section 2.2.

The signalling and clocking methods employed by source-synchronous interfaces is the subject of the rest of this chapter. The performance of these methods is often limited by their robustness in the presence of noise. The types and sources of noise present in digital systems are discussed in Section 2.3. The two main methods employed to send and receive signals in a transmission line environment, high and low impedance signalling, are the topic of Section 2.4. Section 2.5 concludes the chapter with an overview of the issues involved in synchronizing high-speed interfaces.

#### 2.1 Limitations of Conventional Busses

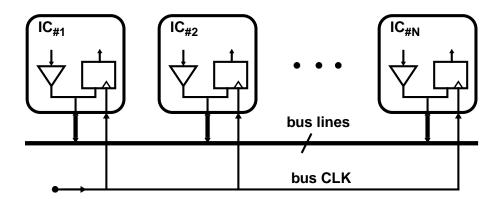

The interconnects in a digital system have traditionally followed the bus paradigm [22]. In a bus system (Figure 2.1) a set of parallel wires is used to interconnect a number of IC's. In order to synchronize the transmission and reception of data, a global bus clock is distributed to all the IC's. The operation of the bus is divided into bus transaction periods each period can be a multiple of the bus clock cycles. Arbitration for the use of the shared bus medium is usually performed by a "bus-master" component. Based on the decision of the master, a given bus cycle is allocated so that a single IC in the system ("bus-slave") transmits data on the bus, while one or more receiver IC's capture the transmitted data. This system provides a shared communication resource, through which each IC can communicate with all the other IC's in the system.

Although this communication paradigm has been adequate in the past, increasing speeds accentuate transmission line effects limiting the performance of conventional bus systems. In the past the electrical length of the bus conductor was short compared to the rise time of the signals. In this case transmission line effects are insignificant - the interconnect can be modeled as an equipotential lumped capacitor or a distributed RC line. However, increasing signal speeds magnifies the effect of the final propagation velocity of the signal energy on the line, creating both signal integrity and timing uncertainty problems. When signal rise times are comparable to the round-trip time of flight of the signal through the line, distributed transmission line characteristics become important and the line cannot be modeled as a single equipotential node [3], [23]. In this case, assuming the

Figure 2.1: Conventional bus block diagram

conductor resistance is very small, the line can be modeled as a ladder network of infinitesimally small inductive and capacitive elements. The signal-wave propagation velocity is then  $u=1/(\sqrt{L\cdot C})$  and the characteristic impedance that the line presents to a fast driver is  $Z_0=\sqrt{L/C}$  where L,C are the line inductance and capacitance per unit length respectively. For example, the propagation velocity of a signal on an 8-mil wide trace of a typical FR-4 PCB is approximately 7-in/ns (i.e.,  $\varepsilon_r=4.7$ , L=14nH/in, C=1.5pF/in). Therefore, any trace longer than approximately 3-in will exhibit transmission line behavior, when driven with sub-nanosecond rise time signals.

From a circuit design perspective, the first problem that a designer has to face is that of matching the transmission line impedance to that of its load. In general, the interface of any transmission line with impedance  $Z_0$  to a load or transmission line with impedance  $Z_L$  will reflect back a portion  $\Gamma$  of the incident wave. The reflection coefficient  $\Gamma$  is given by:

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{2-1}$$

The reflection problem is usually addressed by terminating the bus conductors at both ends with resistors whose nominal value matches the line characteristic impedance  $Z_0$ . Although this increases the power dissipation of busses with TTL or CMOS signal swings, it has helped to extend the speed of conventional busses up to 80-100 MHz.

Increasing the bus signal speeds further can make the signal rise times comparable to the propagation delays through the "stubs" that tie the IC's to shared bus medium (i.e., connecting PCB traces, board connectors and ultimately IC package traces and bondwires). If the electrical length of these stubs is longer than the signal rise times, then the transmission line effects of the stubs become significant as well. This creates impedance discontinuities on the main bus lines and degrades the signal quality through reflections whose magnitude governed by Equation (2-1). The conventional approach for solving this

<sup>1.</sup> The propagation velocity u of a signal in a homogeneous loseless transmission line, is determined by the speed of light  $c_0$  and the relative dielectric constant  $\varepsilon_r$  of the line insulating material  $u = c_0 / \sqrt{\varepsilon_r}$ . In addition to  $\varepsilon_r$  and  $c_0$  propagation velocities in realistic (i.e., non-homogeneous) interconnects are determined by the specific geometry of interconnect [3].

problem has been to limit the maximum signal edge rate, thus imposing an upper bound on the data bandwidth achievable by conventional bus systems.

Timing offset, or skew, creates the second most important limitation on system level interconnections. Skew results both from variation on the electrical characteristics of the bus IC's, and from the finite propagation speed of the signals through the bus conductors. In an ideal situation the bus clock events would occur at exactly the same time on every bus IC, causing data to be driven to or sampled from the bus simultaneously. To satisfy this requirement, bus designers try to equalize the distance from the bus clock source to every component. However, even when the clock distribution scheme is successful in minimizing skew, the bus clock still needs to be buffered internally on every bus IC. The unavoidable variation of the process and operating environment of the IC components introduces variations in the delay between the bus clock and the on-chip clocks. This variation degrades timing margins, and limits the maximum achievable transfer rate. Even when skew is compensated by using clock phase alignment circuits, the more fundamental uncertainty introduced by the propagation delay of the data through the interconnect transmission lines imposes the ultimate limit on the maximum transfer rate achievable by conventional busses. For example, the signal time of flight between IC<sub>#1</sub> and IC<sub>#2</sub> in Figure 2.1 is different from that between  $IC_{#1}$  and  $IC_{#N}$ . This means that the minimum bus clock cycle will be ultimately limited by the maximum distance difference between any two bus components. To evade this problem, several bus designs adopt an asynchronous clocking paradigm where no global clock is used, and the data transfer is based on source-asserted strobe signals. However, asynchronous signalling suffers from the increased overhead of the required request-acknowledge protocol and does not scale well to higher speeds. For this reason high speed system interconnects have increasingly adopted the signalling methods discussed in the next section.

## 2.2 Source Synchronous Interfaces

The signal integrity and skew problems of conventional busses are a result of both the physical dimensions, and the unconstrained data-flow from every IC to every other IC in the system. If these two characteristics are constrained in a manner that does not limit the

system performance, then higher data rates can be achieved. High speed busses achieve this by limiting the flow of data on the bus, and constraining the physical dimensions and electrical characteristics of IC components. High performance parallel links take a more radical approach, by completely eliminating the shared medium and using point-to-point interconnections. These two types of systems are the subject of this section.

#### 2.2.1 High Speed Busses

High speed busses solve signal integrity problems, based on the fact that connections on a shared transmission line create reflections if the connecting "stubs" are long compared to the signal wavelength components. If the stubs are short enough so that their inductance is insignificant, they behave just as capacitive discontinuities. Moreover, if the electrical distance between them is short, the interconnection appears as a uniform distributed transmission line. More specifically, this condition holds if the rise time  $t_r$  of the disturbance caused by the capacitive discontinuity  $C_D$  is larger than the round-trip time of flight  $2t_f$  between two discontinuities, roughly:  $2 \cdot t_f \le 2.2 \cdot Z_0 \cdot C_D$ . Under this constraint, the interconnect transmission line capacitance per unit length increases by the amount introduced by the stub capacitance. Consequently, the propagation velocity of the signals through the line and the line characteristic impedance decrease. Based on these constraints, the signal integrity problems of conventional busses can be solved, if the spacing between the bus components, the component capacitance, and the physical characteristics of the supporting PCB are carefully controlled [24], [25].

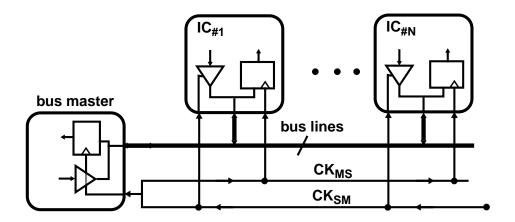

In order to alleviate timing uncertainty problems, high speed busses take advantage of the fact that in many interconnects, such as in memory subsystems, data transfers occur only between a single master and a bus component (or vice-versa). So the solution is to make the data travel the same electrical distance as the bus clock [11]. This idea is illustrated in Figure 2.2. The single bus clock travels in two directions on the bus, corresponding to the two ways of communication: master-to-slave corresponds to CK<sub>MS</sub> and slave-to-master corresponds to CK<sub>SM</sub>. Each of the bus components synchronizes its signal transmission and reception with these two clocks. When, for example, one of the slaves transmits data to the master, its output data pins switch precisely aligned with the edges of

**Figure 2.2:** High speed bus block diagram

clock CK<sub>SM</sub>. The data and clock arrive synchronized at the master which can then use the timing information carried on the clock line to receive the incoming data.

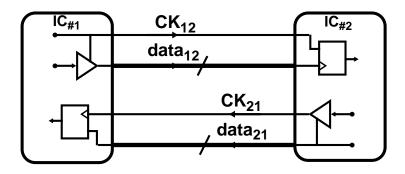

#### 2.2.2 Point to Point Links

The physical constraints of high speed busses make that approach viable only in small scale systems, such as memory or peripheral busses. In larger scale systems, e.g., multiprocessors or communication switches, a more attractive approach is to completely abandon the bus paradigm and use point-to-point links. This approach has advantages both from a circuit design and an architectural point of view. From a circuit design perspective, the use of point-to-point transmission lines offers greater flexibility in the physical construction of the system. Moreover, a point-to-point link has potential for higher communication bandwidth than a bus, due to its reduced signal integrity problems. From an architectural perspective, the bandwidth demands of high speed systems make the shared bus medium the main performance bottleneck. For this reason, distributed interconnection networks and cross-bars have been gradually replacing busses in most large scale multiprocessors [12, 13, 14, 26], while the architecture of most high performance communication switches is inherently based on point-to-point interconnections [16], [27].

A simplified diagram of a high-speed point-to-point interface is illustrated in Figure 2.3. The synchronization scheme used in this system is similar to that used in high speed busses. Each of the two IC's sends data to the other through a dedicated channel of parallel transmission lines. A clock is transmitted along with the data, usually with its

Figure 2.3: Point to point parallel link

edges synchronized with the potential transitions of the data. If the time of flight through the data and clock transmission lines are equal, the data and clock arrive synchronized at the receiving chip. The receiving chip can use the timing information embedded in the clock transitions to sample the incoming data. To maintain signal integrity, the parallel transmission lines need to be terminated to eliminate reflections. The uniformity of the transmission channel minimizes discontinuity related problems. The only inherent discontinuities in such a system are those introduced by the IC packages and the potential connectors.

Variations of this simple architecture which reduce the cost associated with increasing numbers of parallel data lines are possible. For example a source-synchronous point-to-point system might utilize a single set of parallel data lines, which can be used to carry data in both directions. This sort of sharing can be achieved either in a time division multiplexing fashion, or by using the data lines in a full duplex mode [28], [29].

The architecture of both the bus and point-to-point source-synchronous interconnects inherently solves many of the fundamental problems of conventional busses, thus enabling Gbit/sec/pin inter-chip data-rates. Nevertheless, the performance of source synchronous interconnects still depends on the performance of the signalling and clocking circuits employed by particular implementations. The design of these circuits is the subject of the rest of this chapter. First, however, the next section reviews digital system noise, which affects both signalling and clocking circuit performance.

### 2.3 Noise Considerations

The primary goal when selecting a particular signalling or clocking scheme is to transmit data between system components with maximum bandwidth, while keeping the associated costs low. These costs include the power dissipated and the area occupied by the signalling and synchronization circuits, as well as the cost of the required external components. One of the most important obstacles in achieving these objectives is the noise present in all digital systems. Noise alters the amplitude and timing of transmitted signals, thus impeding their correct reception. This additive noise can be either related to, or independent from the originally transmitted signal amplitude. Independent noise can be easily overpowered by increasing the amplitude of the signals. Dealing with a proportional noise source, though, requires minimizing or cancelling it. This is a more difficult goal, since it can only be accomplished through careful design of the signalling circuits and transmission environment. The most important proportional noise sources are reflections, cross-talk and self-induced power supply noise. Independent noise sources include thermal noise and unrelated power supply noise. Both of these types of noise are discussed in this section, along with methods commonly used to deal with them.

Reflection-induced intersymbol interference is the most common type of proportional noise. As was discussed in Section 2.1, to avoid reflections in a transmission line environment, signal lines need to be terminated. This can be accomplished by placing termination circuits on either the transmitter or the receiver end of the line. The termination circuit impedance absorbs the transmitted signal energy, and prevents it from being reflected back into the transmission medium. However, mismatches between termination and line impedances create reflected waves on the transmission line. These reflected waves add to the subsequent signals, thus resulting in a form of intersymbol interference. For example, Equation (2-1) shows that a 20% mismatch between the termination and line impedances gives rise to a reflected wave, whose approximate amplitude is equal to 10% of the original signal. Terminating both at the source and destination ends of the transmission medium can be used to alleviate this problem at the expense of increased power dissipation. Dynamic termination matching techniques can also be used to precisely match the termination impedance to that of the transmission line [30], [31].

Another source of reflections is manifested at higher speeds, when signal transitiontimes become comparable to the propagation delays through the package traces, bondwires, and board connectors. These components can create inductive or capacitive discontinuities which again degrade the signal quality by generating reflections. The magnitude of the reflection  $V_{LD}$ ,  $V_{CD}$  created by an inductive or capacitive discontinuity on a line with nominal impedance  $Z_0$  is:

$$V_{LD} = \frac{L_D}{2 \cdot Z_0 \cdot t_r} \cdot V_I, \quad V_{CD} = -\frac{C_D \cdot Z_0}{2 \cdot t_r} \cdot V_I$$

(2-2)

where  $L_D$ ,  $C_D$  is the discontinuity inductance or capacitance,  $V_I$  the incident voltage magnitude and  $t_r$  the signal rise time. High quality connectors (e.g., Augat-EII, Teradyne-MBC), behave as distributed transmission lines with typical impedances in the range of 45-55  $\Omega$ . On the other hand, the pin inductance of typical ceramic packages varies between 15-30 nH. Better package designs reduce that inductance to 4-10 nH through the use embedded ground planes. Still, however, applying Equation (2-2) reveals why packages are one of the major limitations of high speed signalling today: a 5-nH discontinuity on a 50- $\Omega$  impedance line creates a reflection of approximately 12% with a 500-ps signal rise time.

Another problem created in a transmission line environment is that of cross-talk. The transmission line model used so far assumes that the capacitance and inductance of the line exist only between the forward and the return signal paths. While this is a safe assumption for a coaxial cable or an isolated PCB trace, it is not true for connector pins, package leads, and closely spaced PCB traces. The inter-conductor mutual inductance and capacitance couples noise between adjacent traces, connector pins, package leads, and bondwires. In such an environment, a wave propagating in a transmission line induces capacitive or inductive currents on adjacent and nearby lines. These currents create forward and backward propagating waves. The duration of the backward propagating wave is equal to twice the electrical length of the coupling and is proportional to the amplitude of the inducing wave. The governing proportionality constant  $K_R$  depends on the speed of

propagation u, the line impedance  $Z_0$ , and the mutual inductance  $L_M$  and capacitance  $C_M$ :

$$K_R = \frac{u}{4} \cdot \left( Z_0 C_M + \frac{L_M}{Z_0} \right) \tag{2-3}$$

The forward propagating wave has an amplitude proportional to the length of the coupled portion of the line, the inducing wave rise time, and the proportionality constant  $K_F$  which is given by:

$$K_F = \frac{1}{2} \cdot \left( Z_0 C_M - \frac{L_M}{Z_0} \right) \tag{2-4}$$

Equations (2-3) and (2-4) show that minimizing crosstalk entails minimizing the mutual inductance and capacitance by placing unrelated signal lines far apart and interleaving high speed signal pins with ground pins in connectors and packages. Furthermore, Equation (2-4) shows that forward crosstalk can be completely eliminated if the inductive and capacitive coupling between adjacent lines are matched (i.e.,  $C_M/C=L_M/L$ ), as is the case with embedded PCB traces. The reverse crosstalk reflection problem (i.e., crosstalk noise arriving to the receiver end after being reflected by the transmitter end) can be eliminated by terminating the transmission lines both at their source and destination ends. This way the reverse crosstalk is absorbed at the transmitter end by the corresponding termination resistor. However, the cost of these coupling minimization methods restricts their application in high-end systems, thus often forcing designers to accommodate large crosstalk components in the system noise budget.

Self-induced power supply noise is a result of the finite power supply pin impedance in semiconductor packages. When an output driver switches, the current drawn from the external supply of the chip changes at a rate equal to dI/dt. The inductance L of the chip's supply network will then cause the on-chip power supply voltage to drop by a voltage  $\Delta V = L \, dI/dt$ . For example, a 1-V amplitude signal transmitted in a 50- $\Omega$  line with 500-ps rise time requires a 20mA/500ps dI/dt. If the inductance of the on-chip power supply is 5nH,

driving the signal will result in a 200-mV voltage drop on that supply. This on-chip power supply voltage drop can appear as additive noise both on the switching and the quiescent signals. Since on-chip decoupling capacitance does not have an effect on the noise generated by switching output drivers [3], the two alternatives for minimizing this type of noise are: (i) minimizing the power supply network inductance, and (ii) using a signalling method which draws constant current from the external supply. The decision on which of these two methods is adopted depends mainly on the cost of increased number of power supply pins versus increased power dissipation.

The second class of noise sources is independent of the transmitted signal amplitude: thermal noise, process variation induced offsets, and unrelated power supply noise. Independent noise sources can be overpowered by enlarging the signal amplitude. Since thermal noise typically has very small amplitude, this method can be applied without any significant increase in power dissipation. For example a  $50-\Omega$  termination resistor driving a 1-pF load results in a thermal noise power of approximately 4.15 10<sup>-9</sup> V<sup>2</sup> over a 3.3-GHz bandwidth. This corresponds to a 64-µV RMS value of Gaussian thermal noise. The probability of this noise amplitude exceeding 0.5-mV is less than 10<sup>-26</sup>. Since typical signal amplitudes are well above 100-mV, the Gaussian thermal noise can be safely ignored in a typical signalling system. On the other hand, offsets induced by process variations typically have larger amplitudes, and depend on the design and layout of the driver and receiver circuits. Still, however, their magnitude can be easily bounded to below 50-mV, so they are not a large concern. Unrelated power supply noise is created by digital circuits integrated on the same die as the signalling circuits. This type of noise can be either minimized by using on-chip decoupling capacitors, overpowered by using increased signal swings, or canceled by appropriate signalling. As will be seen in Section 2.4, overcoming proportional and unrelated power supply noise is the main challenge when designing a robust signalling method.

## 2.4 Signalling Methods

A signalling method provides the means by which binary information is reliably sent between IC's over a given transmission medium. A signalling system consists of various components, the design of which comprises several trade-offs affecting the performance and cost of the overall system. The binary information on the transmitter IC is first converted to a signal on the transmission medium by the transmitter output driver. The most important characteristics of this driver are its output impedance and the resulting signal levels on the line. The signal levels are chosen so that the signal can be distinguished from additive noise, according to considerations discussed in Section 2.3. The output impedance of the driver affects the noise rejection and power dissipation properties of the signal-ling system. Tightly coupled with the transmitter design is the topology and placement of the termination circuits which, as discussed in Section 2.3, absorb the transmitted signal energy and prevent it from being reflected on the transmission medium. The termination circuits may be placed on both the transmitter and receiver ends of the line. Moreover, depending on the impedance of the output driver, termination can either be in series or in parallel with the flow of the signal.

The signal sent over the transmission medium needs to be decoded back to binary information at the receiver end. This decoding function is essentially a comparison of the incoming signal to an explicit or implicit "reference" value. In the conventional approach of purely single ended signalling, the reference value is implicitly set relative to the supply by the threshold voltage of the receiver circuit. Despite the minimal design complexity of this method, its main drawbacks, when compared to low-swing differential or pseudo-differential signalling, are increased power dissipation and reduced noise immunity. In fully differential signalling both the true and complementary value of the signal are sent over the transmission medium, creating an implicit "reference" value and improving noise immunity. In pseudo-differential signalling the reference value is explicitly generated by a dedicated circuit and shared by a number of parallel receivers. In this way, pseudo-differential signalling trades-off noise immunity for reducing the system power dissipation and number of required pins and wires.

Signalling methods can be categorized mainly by whether the impedance of the transmitter output-buffer is comparable to, or much higher than the impedance of the transmission medium. Both types of signalling can be implemented either in a differential or a single-ended form. These two main methods of signalling – high and low impedance – are discussed in the following two subsections.

#### 2.4.1 Low Impedance Signalling

In a low impedance signalling environment, the impedance of the output buffer is equal to or less than the impedance of the transmission medium. Thus, the buffer can be best approximated as a switching voltage source in series with a resistor driving the transmission line – also commonly referred to as "voltage-mode" driver. The traditional implementation of low-impedance signalling in bipolar or BiCMOS technologies uses an emitter follower driving a parallel-terminated transmission line. Since the CMOS equivalent of a parallel-terminated emitter follower is both difficult to implement and consumes a lot of power, low-impedance signalling systems in CMOS usually employ a simpler series-termination scheme with different characteristics. This type of signalling is the main topic of rest of this section

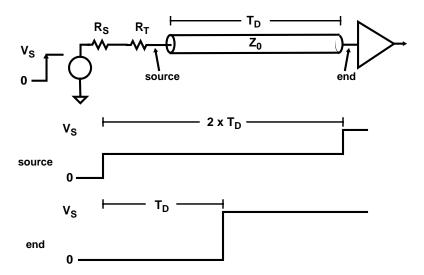

A model for a point-to-point series-terminated low-impedance signalling system is depicted in Figure 2.4. The transmitter buffer behaves as a time varying voltage source

Figure 2.4: Model of a low impedance series-terminated signalling system

with a source impedance  $R_S$ . To avoid standing waves on the transmission line the value of the series termination resistor  $R_T$  plus the output impedance of the voltage source  $R_S$  is equal to the characteristic impedance of the transmission line  $Z_0$ . This way any wave propagating towards the source end of the transmission line is absorbed by the combined series impedance of  $R_S + R_T$ .

In the signalling system of Figure 2.4 the transmitter injects a voltage step in the transmission medium. In the ideal case where  $R_S+R_T=Z_0$ , a source voltage step of amplitude  $V_S$  is initially divided by 2 before it begins propagating in the transmission line. At the open far-end of the line where the reflection coefficient  $\Gamma$  is 1, the propagated wave is doubled, resulting in a receiver incident wave amplitude equal to the initially transmitted step  $V_S$ . In case the load of the far end termination is purely capacitive the incident wave is an exponential with time constant  $Z_0 \times C$ , where C is the capacitive load. The reflected wave has an amplitude  $V_{S}/2$  and propagates back towards the source end of the line. When this reflection arrives at the source end, it is absorbed by the series combination of  $R_S + R_T$ . At this point the voltage throughout the system stabilizes at a value equal to the initially transmitted step  $V_S$  and the source driver current drops to zero. If the round-trip delay through the line  $2 \times T_D$  is larger than the signal bit time  $T_B$ , the transmission of the next symbol starts before the reflection of the previous symbol returns to the source. In this case, assuming the source resistance is linear, the transmission line and transmitter-end voltages are a result of the continuous superposition of the forward and the reverse propagating voltages of the transmitted symbols and their half amplitude reflections. However, the resulting voltage at the receiving end is indistinguishable from the case when  $T_R > 2 \times T_R$  regardless of the magnitude of symbol times.

The power dissipation of a series-terminated low-impedance signalling system depends on the relation of the bit time to the round-trip delay through the line. When the delay through the line is less than the bit time, the system dissipates power only during the initial round-trip of the signal through the transmission line. The resulting worst-case power dissipation is  $T_D/T_B \times V_S^2/Z_0$ . When the bit duration is shorter than the line round-trip delay, the driver is supplying continuous current through the line resulting in a worst case power dissipation of  $V_S^2/(2\times Z_0)$ . However, the power dissipation can be less

than this absolute maximum, when the signal transition density is low enough to allow the line voltage to settle between transitions. This zero static power dissipation is the main advantage of low-impedance series-terminated signalling.

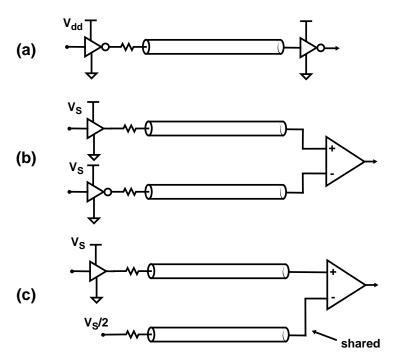

Decoding the signal at the receiving end, requires a way of referencing the incident wave to some predetermined voltage standard. For this purpose a low impedance signal-ling system can implement either purely single-ended, differential, or pseudo-differential signalling. A purely single ended system can be implemented by using conventional CMOS inverters both at the transmitter and receiver end of the line [32]. This straightforward implementation, shown in Figure 2.5-(a), is susceptible to common mode noise. The low impedance of the transmitting buffer causes power supply noise on the transmitter chip to appear unattenuated on the transmitted signals. Additionally, since the threshold voltage of the receiver is implicitly set by the power supply of receiving IC, any noise on either the receiver or transmitter IC directly subtracts from the signal noise margins. Another disadvantage, discussed in more detail in Chapter 3, is that the impedance of the transmitting CMOS inverter changes during the signal transition. Therefore, even in the presence of an external termination resistor this type of system might suffer from multiple

Figure 2.5: Alternative implementations of low impedance, series-terminated signalling

reflections. These disadvantages, along with the increased power dissipation and self induced dI/dt noise resulting from driving a full-swing signal, make this simple realization of low impedance signalling unattractive in high-speed systems.

Many of the problems outlined above can be mitigated if the signalling system uses lower signal amplitudes. Additionally, since, as described in Section 2.3 a large portion of the noise is proportional to the signal swing, reducing the signal swing does not result in a proportional reduction in signal noise margins. In fact, the noise margin as a fraction of the signal swing can remain unchanged as long as the system noise is dominated by proportional noise. An additional advantage of smaller signal swings is that the impedance of the transmitting buffer varies less over the signal swing, making the series termination more effective in absorbing reflections that arrive at the source end while the buffer changes state. A reduced output swing buffer can be implemented using a push-pull buffer with a supply equal to the signal swing [15], [29], [31], [33]. Another alternative is to implement the driver with open-drain MOSFETs operating in the linear region [12]. In the latter case the driver impedance becomes infinite when a high voltage is transmitted on the channel, so the transmission line needs to be also parallel-terminated to a voltage that determines the high end of the signal swing. The active driving impedance in both alternatives can be set to be equal to that of the transmission line, either by using external termination resistors [15], or by a dynamic impedance matching scheme [30], [31].

Reducing the signal swing means that the reference cannot be set implicitly by the IC supply voltages. A fully differential signalling scheme (Fig. 2.5-(b)) can be employed to provide an implicit reference, and simultaneously maximize the noise robustness of the system. In this case the transmitter chip sends both polarities of the signal, and the receiver considers only the difference of the two incident waves. In this way the bit decoding at the receiver is, to the first order, independent of the supply voltages, thus improving the noise tolerance of the system at the expense of power dissipation and increased number of pins and wires. Alternatively, pseudo-differential signalling can be used to reduce system cost. In pseudo-differential systems, such as the one shown in Figure 2.5-(c), a reference voltage in the center of the signal swing is generated on the transmitter side. This voltage is shipped to the receiver, and can be shared among a number of signals in a parallel inter-

face, thus reducing the number of lines and the overall power dissipation of the system. This form of pseudo-differential low impedance signalling is the most common in parallel point-to-point interfaces.

The series-termination method described above, is commonly used in CMOS implementations of point-to-point low-impedance signalling systems. In many applications however, low-impedance drivers are combined with other termination schemes. For example in some implementations, the backwards reflection of the source-terminated openended drivers in Figure 2.5 creates multiple reflections on the transmission medium, especially when combined with the non-linear driver impedance. In these cases, transmitter series termination can be combined with receiver-end parallel termination, in order to eliminate multiple reflections at the expense of increased power dissipation [14]. In bus environments, low impedance drivers are implemented as open-drain FETs operating in the low-impedance linear region, while the bus lines are terminated on both ends to a voltage that sets the high level of the signals [34]. Despite the differences of these alternative implementations, the characteristic they share with the most common series-terminated case is that of relatively low on-chip driver impedance. This reduced driver impedance creates the main disadvantage of low-impedance signalling systems, by not allowing isolation of the signal on the transmission medium from noise on the transmitter chip. High impedance signalling systems, discussed in the next section, eliminate this problem through the use of current source drivers.

#### 2.4.2 High Impedance Signalling

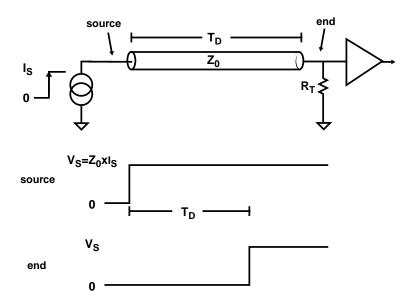

A model of a high impedance signalling system is shown in Figure 2.6. The transmitter buffer behaves as a time varying current source, generating current pulses of magnitude  $I_S$ . The resulting voltage pulses of magnitude  $I_S \times Z_0$  propagate at full intensity through the transmission line. At the receiver end of the line, the termination resistor with a value ideally equal to the characteristic impedance of the line  $Z_0$  absorbs the propagated voltage wave. Similar to the case of low-impedance series-terminated signalling, the incident wave is an exponential waveform with a time constant of  $Z_0 \times C$ . Following the transition at the receiver end, the system stabilizes until the transmission of the next bit through the

**Figure 2.6:** Model of a high impedance parallel-terminated signalling system

line. Similar to the case of low-impedance signalling, the transmission of the next bit can start before the pulse corresponding to the previous bit arrives at the receiver. The power dissipated in a high impedance signalling system depends on the pattern of the transmitted data. The worst case power dissipation of  $I_S^2 \times Z_0$  in the model of Figure 2.6, occurs when the data is a stream of 1's, causing the transmitter current source to continuously supply current to the transmission line.

The main advantage of the signalling system in Figure 2.6 is that the current source driver isolates the line signal from noise on the transmitter IC power supply, thus minimizing a major source of proportional noise. Its main disadvantage however, is that the absence of termination on the transmitter end causes backwards propagating noise, such as reverse crosstalk, to be reflected towards the forward signal direction and add to the noise seen at the receiver end. Eliminating this problem requires terminating both ends of the transmission line at its characteristic impedance, which results in reduced signal swing or increased power dissipation.

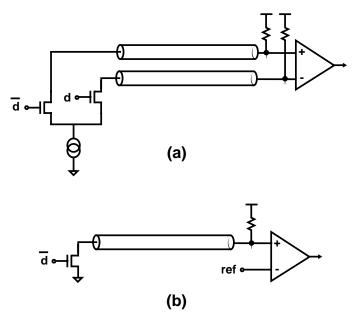

High impedance signalling systems are usually implemented in fully differential or pseudo-differential form. Figure 2.6-(a) shows a typical implementation of low-swing fully-differential signalling [35], [36], [37]. The open-drain differential pair approximates the current source driver of Figure 2.6. The tail current is steered on the branches of the

Figure 2.7: Alternative implementations of low impedance, series-terminated signalling

differential pair, creating a differential voltage on the two equal-length transmission lines. The receiver amplifies the voltage difference across the matched termination resistors, decoding the transmitted bit. The fully differential operation of the transmitter and receiver rejects common mode noise. Additionally, the constant current drawn by the transmitter buffer minimizes the noise induced on the transmitter chip. Although this form of high impedance signalling is the most noise immune, it is also the most expensive in terms of power dissipation and required transmission lines and package pins. As with low impedance signalling, a compromise is to implement the pseudo-differential signalling system shown in Figure 2.7-(b), by using an open drain NMOS driver [11], [13], [38]. In contrast to low-impedance open-drain drivers, in these implementations the driver transistor must remain in the saturation region of operation, where it best approximates a current source. Therefore the signal on the line must not fall more than a threshold voltage below the gate of the driver transistor. Additionally, to maintain a constant driver current and isolate noise on the transmitter chip supply, the gate voltage of the driver transistor must track its source voltage. The reference voltage of the receiver can be generated either externally or internally to the transmitter chip, and can be amortized over a number of parallel signals to reduce the cost of the system. The particular choice depends on the system constraints: point-to-point systems can easily use an internally generated reference voltage, while multi-drop busses use a global reference and adjust the buffer current to maintain correct signal swings around the reference voltage.

Although the design space of low and high impedance drivers seems relatively large, the differences mainly concern trade-offs between power-dissipation and noise rejection, and the final choice depends on the constraints of the particular system. However, a robust signalling method is not the only requirement for achieving high bandwidth interchip communication. In addition to be able to distinguish between the different values of a single data item, the system needs to be synchronized, so that it can distinguish the boundaries of data items in time, and reliably transfer all of them from one IC to another. Methods that address that problem are discussed in the next section.

### 2.5 Clocking Methods

A clocking or timing discipline synchronizes a signalling system, by dictating when a driver circuit places a new data item on the interconnection line, and when the receiver samples that data item at the other end of the line. The main problem that a clocking method has to address is that of timing uncertainty. Timing uncertainty in interchip signalling comes from various sources, and can be distinguished into two main categories. Fixed timing uncertainty, or skew, is caused by unequal line lengths and the delay variation of IC components due to manufacturing. Time-varying uncertainty, or jitter, is caused mainly by signal amplitude and power supply noise. Signal amplitude noise can translate to jitter by altering the time at which the value of a signal changes. Power supply noise introduces timing uncertainty by affecting the delays through the on-chip signal paths. A third source of time varying timing uncertainty is temperature variations which also affect the delays through on chip signal paths.

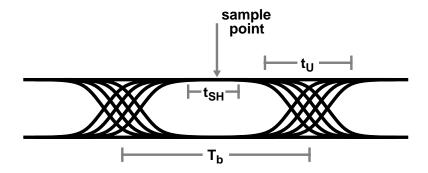

In point-to-point signalling systems, synchronization is a problem that can be mainly addressed at the receiver end: every transmitted symbol needs to be sampled off the line at the time instant during which is most unlikely to change. This requirement usually dictates implementing data pin receivers which sample the data at the center of its "eye", as illus-

Figure 2.8: Optimal sampling point and timing margins

trated in Figure 2.8. This way the maximum data transfer rate is determined by the following two parameters:

- $t_U$ : the incoming signal timing uncertainty. This is the sum of the rise/fall time of the signal plus the uncertainty in the total signal delay.

- $t_{SH}$ : the receiver "setup-and-hold" uncertainty window i.e., the time-zone around the sampling time during which a changing input signal can result in an undefined receiver output. Both the sampling time uncertainty and the receiver apperture contribute to  $t_{SH}$ .

The timing margin of the clocking scheme  $t_M$ , which can be viewed as the tolerance to additional delay uncertainty, is given by:  $t_M = T_b - t_{SH} - t_U$ , where  $T_b$  is the bit time.

Positioning the sampling event at the center of the data eye requires knowledge about the potential data transition points. This requirement, along with the fact that data is generally aperiodic, suggests that either encoding of the data, or providing an explicit timing reference signal is necessary. The first option can be implemented either through a completely asynchronous protocol [39], or by encoding the data to guarantee some level of transition density and recovering the transmitter clock [5]-[10]. Due to the increased overhead associated with both of these methods, intra-system interconnect designers usually rely on supplying an explicit reference clock signal, thus realizing a mesochronous timing environment [4]. The fixed timing uncertainty, introduced by the variation of the delay from the system clock source to the interface components, is minimized by using a source

Figure 2.9: Receiver clocking alternatives

synchronous signalling architecture such as those described in Section 2.1.

Having minimized the major component of fixed timing uncertainty through architectural changes, the remaining problem of source-synchronous interfaces is to position the on chip sampling event in the center of the data eye. Figure 2.9 illustrates three alternative ways of accomplishing this goal. The simplest method is depicted in Figure 2.9-(a). The reference clock transitions at twice the rate of the data. Both the reference clock and the parallel data items are amplified and buffered on the receiver chip through matched delay buffers. The negative edge of the on chip clock is then used to sample the on chip data. The simplicity of this method is its main advantage. However, setting the data rate equal to the clock frequency utilizes poorly the available interconnect bandwidth. In an alternative

method, depicted in Figure 2.9-(b), data bits are sent during both of the half-periods of the clock [12]. Although the reference clock is again sent in phase with the data, it is also delayed by 90° through an external transmission line whose electrical length is half a bit time longer than the electrical length of the parallel data lines. The on-chip data and clock buffers have matched delays, resulting in a 90° phase displacement between the on-chip sampling clock and data. Therefore, both clock edges are positioned in the center of the data eye, and both of them can be used to sample the on chip buffered data. While this simple method can potentially double the data rate, its main disadvantage is that the receiver's timing margin is fixed by an external component, and does not improve at slower clock frequencies. Moreover, the external 90° delay, usually created by a longer PCB trace, occupies board space and is not always accurate. For these reasons, the most reliable solution is to use an on-chip phase adjustment circuit to phase shift the on-chip sampling clock by 90° relative to the external reference clock, and simultaneously cancel the potential amplification and buffering delay of the data as illustrated in Figure 2.9-(c). This phase adjustment circuit can be implemented either as a phase locked loop, or a delay locked loop, the design of which is the topic of Chapter 5.

The timing margin of the methods described above is mainly determined by the jitter of the sampling clock relative to the transmitted data. Since external coupling to the data signals and the reference clock can be minimized by careful system design, the main component of this jitter is introduced by on-chip power supply noise. At higher transmission speeds three additional factors of timing uncertainty need to be compensated. First, the potential offset in the timing uncertainty window of the input pin receiver results in the optimal placement of the sampling clock being slightly offset from the ideal 90° point. Moreover, variations in the duty cycle of the sampling clock result in timing margin degradations, since the data is sampled on both clock edges. Finally, the skew introduced between the data signals and the reference clock by variations in the delay of nominally identical transmission lines might need to be compensated. Techniques for dealing with these sources of timing uncertainty will be discussed in the following chapters.

## 2.6 Summary

Increasing the interchip communication bandwidth in digital systems requires improving signal integrity and minimizing timing uncertainty. Both of these requirements lead system designers to abandon the traditional multi-drop bus architectures, and use source synchronous busses or point-to-point parallel links. Further bandwidth improvements require dealing effectively with digital system noise, which affects both the amplitude and the timing of interchip signals.

The designer can either overpower amplitude noise with large signals, or minimize its impact by using a noise insensitive signalling method. Since a large fraction of the noise is proportional to the signal amplitude, minimizing or canceling amplitude noise is the main goal of a signalling scheme. The driver circuit design largely determines the characteristics of signalling schemes. Low impedance signalling utilizes voltage mode drivers, and has the potential for zero static power dissipation. High impedance signalling uses current mode drivers, and has the advantage that it isolates the transmitter's power supply noise from the signal. While both methods can be implemented in a fully-differential fashion, cost considerations usually dictate pseudo-differential implementations, in which a shared reference voltage or current is used by the receiver to decode the signal levels. Similarly, cost and latency considerations dictate the use of a shared reference clock signal to designate the symbol/bit boundaries of the transmitted signals. The receiver uses the timing information embedded in the reference clock transitions, to sample the data on the interconnect lines. To position the sampling event at the optimal point in time, and cancel the timing uncertainty introduced by potential amplification and/or buffering, a phase alignment circuit is necessary, although less robust clocking schemes relying on external delay components are also used.

## Chapter 3

# **Source Synchronous Interface Design**

As discussed in Chapter 2, the inherent timing uncertainty problems of conventional multi-drop busses lead designers to adopt source synchronous signalling systems in order to increase interchip communication bandwidth. Increasing that bandwidth further requires careful consideration of the signalling and clocking issues of source synchronous systems. To elaborate on these issues, this chapter discusses the architecture and circuit design of a 500 Mbits/sec/pin point-to-point link parallel interface [15], intended for use in multiprocessor interconnection networks. This design shares the same basic approach with others described in recent literature [12], [13], [14]. The limitations of this baseline approach form the main motivation for the development of the signalling and synchronization circuits discussed in Chapters 4 and 5.

A high-level block diagram of the interface is shown in Figure 3.1-(a). To minimize system cost and power consumption this interface uses a low impedance pseudo-differential signalling scheme. To achieve synchronization, a reference clock is transmitted in phase with the parallel data signals, as was outline in Section 2.5. Given that the electrical lengths of the data and clock lines are equal, the signals arrive in-phase at the receiver end. The receiver can then use the timing information embedded in the transitions of the reference clock to position its on-chip sampling clock CLK in the center of the valid bit time, and sample the incoming data twice per clock period as depicted in Figure 3.1-(b).

This chapter will begin by discussing in Section 3.1 the design of the signalling circuits of the interface. In particular, the trade-offs considered in the design of the line driver

Figure 3.1: Interface block diagram (a), and timing (b)

circuits will be discussed along with the design of the input pin receiver. Section 3.2 will then address the design of the key clocking circuits: the DLL used to offset the on-chip sampling clock by 90° relative to the transmitted data, and the duty cycle adjuster circuit used to restore the duty cycle of the sampling clock to its nominal 50% value. The experimental results measured on a fabricated prototype will be discussed in Section 3.3. Having reviewed the details of this baseline design, the chapter will conclude with a discussion of its main limitations.

## 3.1 Signalling Circuits

The configuration of the interface signalling circuits is depicted in Figure 3.2. This interface uses push-pull, series-terminated drivers, with low-swing 1-V output signals. To implement pseudo-differential signalling, a 0.5-V reference voltage is generated on the transmitter board using a resistive voltage divider. This reference voltage is sent to the

**Figure 3.2:** Interface signalling scheme.

receiver which uses a self-biased differential amplifier to decode the line signals. The following two sections will discuss in detail the design trade-offs considered in the design of the line driver and input receiver circuits.

### 3.1.1 Line Driver Design

As shown Figure 3.2 this interface uses a reduced-swing, low impedance driver with external series termination. This signalling scheme offers the advantage of zero static power dissipation for low signal transition rates. Moreover, in practical CMOS implementations, the push-pull series terminated driver used in this design will always result in a lower power dissipation compared to the alternative of an NMOS open-drain high impedance driver. Assuming a worst case transition density of 1, this signalling scheme dissipates a total (i.e. on-chip and off-chip) power of  $P_{LI} = V_S^2/(2 \cdot Z_0)$ , where  $V_S$  is the 1-V signal swing, and  $Z_0$  the 50- $\Omega$  line impedance. In contrast, a signalling system using a high-impedance parallel terminated driver operating under the same conditions would dissipate a total power of  $P_{HI} = (VDS + V_S) \cdot V_S/(2 \cdot Z_0)$ , where  $V_{DS}$  is the voltage across the open-drain NMOS transistor. While  $V_{DS}$  can be made theoretically very small, practical considerations, such as the pre-driver voltage swing and the driver output capacitance, dictate the voltage across the NMOS open drain transistors to be at least equal to the voltage swing  $V_S$ . Thus, in point-to-point link environments, a series-terminated voltage-mode driver is more attractive than current mode drivers, in terms of power dissipation.

Figure 3.3: Large signal impedance of full-swing driver