# HARDWARE/SOFTWARE CO-DESIGN OF RUN-TIME SYSTEMS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Vincent John Mooney III June, 1998 © Copyright 1998

by

Vincent John Mooney III

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Giovanni De Micheli(Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Oyekunle A. Olukotun(Associate Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Robert W. Dutton

Approved for the University Committee on Graduate Studies:

## Abstract

Trends in system-level design show a clear move towards core-based design, where processors, controllers and other proprietary cores are reused and constitute essential building blocks. Thus, areas such as embedded system design and system-on-a-chip design are changing dramatically, requiring new design methodologies and Computer-Aided Design (CAD) tools.

This thesis presents a novel system-level scheduling methodology and CAD environment, the Serra Run-Time Scheduler Synthesis and Analysis Tool. Unlike previous approaches to run-time scheduling, we split our run-time scheduler between hardware and software, as opposed to placing the scheduler all in one or the other. Thus, given an already partitioned input system specification in an HDL and a software language, Serra automatically generates a run-time scheduler partly in hardware and partly in software, for a target architecture of a microprocessor core together with multiple hardware cores or modules.

A heuristic scheduling algorithm solves for priorities of software tasks executing on a single microprocessor with a custom priority scheduler, interrupt service routine, and context switch code. Real-time analysis takes into account the split hardware/software implementation both of the scheduler and of the tasks. The scheduler supports standard requirements of both domains, such as relative timing constraints in hardware and semaphores in software.

A designer who uses the Serra CAD tool gains the advantage of efficient satisfaction of timing constraints for hardware/software systems within a framework that enables different hardware/software partitions to be quickly evaluated. Thus, a hardware/software partitioning tool could easily sit on top of Serra, which would generate run-time systems for different hardware/software partitions chosen for evaluation. In addition, Serra's more efficient design space exploration can improve time-to-market for a product.

Finally, we present two case studies. First, we show a full analysis, synthesis, and simulation of a hardware/software implementation of a robotics control system for a PUMA arm [AKB86, Uni84]. Second, we describe a sample prototype of the split runtime scheduler in an actual design, a force-feedback real-time Haptic robot. For this application, the hardware part of the scheduler was implemented on programmable logic communicating with software using a standard communication protocol.

## Dedication

To my parents, Vincent John Mooney Jr. and Eulalia Maria Mooney, without whose love and encouragement throughout the years this thesis would not have been possible.

## Acknowledgments

I have many people to thank for this dissertation. First and foremost, I would like to thank my advisor, Professor Giovanni De Micheli, for his keen insight in helping me choose an important Ph.D. topic and for his guidance throughout the Ph.D. There was more than one occasion where I arrived at a technical result, only to look back and marvel at his guidance in setting me upon the path that led to the solution, while avoiding many pitfalls which were crystal clear to me only in hindsight.

I would also like to thank Professor Oyekunle Olukotun for serving as my associate advisor and as a reader of this thesis. The interaction with Professor Olukotun and his research group – including Rachid Helaihel, Jeremy Levitt, Basem Nayfeh and Mike Chen – provided excellent opportunities for enriching and challenging the research ideas I followed. Similarly, Professor David Dill and his students – including Han Yang, Jeffrey X. Su and Clark Barrett – provided superb interaction without which my research would have been significantly compromised. Additional thanks go to Professors Olukotun and Dill for serving on my Ph.D. Orals Committee.

Special thanks go to Professor Robert Dutton for serving both as the Chair of my Ph.D. Orals Committee and as a reader of this thesis. I am very grateful to have such careful input from someone outside of my circle of immediate research colleagues.

As for the development of the Serra Synthesis System, I would like to acknowledge the contributions of Toshiyuki Sakamoto, who wrote the hardware-tasks in Verilog HDL and implemented interrupts in the MIPS R4000 model, Sera Linardi, who

ported CINDERELLA to MIPS, Firdaus Abdullah, who implemented the full Verilog simulations of the hardware-software run-time scheduler for the Robot Arm Controller, and Yau-Tsun Steven Li, who provided guidance and support for CINDERELLAM and associated analysis. I also would like to thank Meredith J. Goldsmith and Giuseppe A. Paleologo for extended discussions about the relation of the scheduling problem considered here to the work in operations research, as well as the help provided in formulating the problem in AMPL.

I also would like to thank Thoi Nguyen, Charles Orgish and Babak Moghadam for their network help, without which none of this would have been possible.

Many industry contacts have enriched this thesis tremendously: James Rowson, Shields Neely, Bill Mark, Mark Shand and Jim Ready, to name a few.

Finally, I would like to thank the members of the CAD group, the Robotics group, and my many friends I made while at Stanford. Claudionor Coelho, Luca Benini, Rajesh Gupta, Polly Siegel, Jerry Yang, David Filo, David Ku, James Smith, Luc Semeria, Tajana Simunic, Matija Siljak, Valeria Bertacco, Alessandro Bogliolo, Marco Platzner and Aneesh Koorapaty are current or former members of the CAD group who all helped me in some way, thanks. Diego Ruspini, Kyong-Sok Chang, and Oscar Madrigal of Professor Oussama Khatib's robotics group helped tremendously, as did Professor Khatib himself. Also, Bruce Romney of Jean-Claude Latombe's group helped in many ways, but I will only mention two: the PUMA robotics control software code and the TAship for EE271 Intro to VLSI. In addition, Scott Devine, Ben Werther, and Robert Bosch of Professor Mendel Rosenblum's Operating Systems group provided generous help at key moments. Finally, Oskar Mencer was an important ally in the Pamette/Synopsys/Xilinx struggles. As for my close friends, many of the names have already mentioned; I will say a few, but not all, of the names not mentioned: Derek Gerlach, Ajay Kapur, Rafael Betancourt, Sonja Schuemann, Lakita Garth, Florencia Cortina, Ekua Blankson, Afua Ntiwa, Manolo Clavel, Dr. Jose Meseguer, Peter Olveczky, Noel Vitug, Mike Vroman, Anthony McCarthy, Mike Pinto and Pedro Gutierrez. Dr. Rick Reis provided mentorship for which I am extremely grateful. Last but not least, my family is to be thanked: Martha Bowers Mooney, Vincent John Mooney Jr., Eulalia Maria Mooney, Alexander Xavier Mooney, Patrick Joseph Mooney, Laurie Jean Mooney, Emily Marie Mooney, Justin Patrick Mooney, and Margaret Ann Mooney.

This research was sponsored by ARPA, under grant No. DABT 63-95-C-0049, by a fellowship from National Semiconductor, and by a software donation from Synopsys.

# Contents

| D            |      |         |                                                | iii |

|--------------|------|---------|------------------------------------------------|-----|

| $\mathbf{A}$ |      |         |                                                | iv  |

| 1            | Inti | oductio | on                                             | 1   |

|              | 1.1  | Hardwa  | are/Software Co-Design                         | 2   |

|              | 1.2  | Require | ements for Designing Hardware-Software Systems | 5   |

|              |      | 1.2.1   | Scheduling at Different Levels                 | 6   |

|              | 1.3  | Object  | ives and Contributions                         | 7   |

|              | 1.4  | Thesis  | Outline                                        | 8   |

| 2            | Bac  | kgroun  | $\mathbf{d}$                                   | 9   |

|              | 2.1  | Previou | us Hardware/Software Co-Design Systems         | 9   |

|              |      | 2.1.1   | COSYMA                                         | 10  |

|              |      | 2.1.2   | VULCAN                                         | 11  |

|              |      | 2.1.3   | POLIS                                          | 13  |

|              |      | 2.1.4   | COWARE                                         | 14  |

|              |      | 2.1.5   | CHINOOK                                        | 18  |

|              | 2.2  | Hardwa  | are Scheduling                                 | 19  |

|              |      | 221     | Integer Linear Programming                     | 19  |

|   |     | 2.2.2              | List Scheduling                          | 20 |

|---|-----|--------------------|------------------------------------------|----|

|   |     | 2.2.3              | Relative Scheduling                      | 20 |

|   |     | 2.2.4              | Conditional Process Graphs               | 21 |

|   | 2.3 | Softwa             | are Scheduling                           | 21 |

|   |     | 2.3.1              | Round-Robin Scheduling                   | 22 |

|   |     | 2.3.2              | Shortest Job First                       | 22 |

|   |     | 2.3.3              | Rate-Monotonic Analysis                  | 22 |

|   |     | 2.3.4              | Least Common Multiple                    | 24 |

|   |     | 2.3.5              | Real-Time Kernel in Hardware             | 25 |

|   | 2.4 | Contro             | ol-Flow Expressions                      | 25 |

|   |     | 2.4.1              | Formalism                                | 26 |

|   |     | 2.4.2              | Synthesis with CFEs                      | 28 |

|   |     | 2.4.3              | Thalia                                   | 29 |

|   | 2.5 | Bound              | ls on Execution Time                     | 29 |

|   | 2.6 | Summ               | ary                                      | 30 |

| 3 | Tar | ${ m get}~{ m Ar}$ | chitecture, Kernel, and System Model     | 32 |

|   | 3.1 | CAD                | Requirements                             | 33 |

|   | 3.2 | Target             | t Architecture and Kernel                | 37 |

|   |     | 3.2.1              | Task Execution                           | 37 |

|   |     | 3.2.2              | Run-Time Scheduler Implementation        | 38 |

|   |     | 3.2.3              | Control of Software                      | 39 |

|   |     | 3.2.4              | Software Generation                      | 40 |

|   |     | 3.2.5              | Priority Scheduler Template for Software | 41 |

|   | 3.3 | Syster             | n Modeling                               | 42 |

|   | 3.4 | Summ               | arv                                      | 45 |

| 4 | Rea | d Time | e Analysis                                                      | 46  |

|---|-----|--------|-----------------------------------------------------------------|-----|

|   | 4.1 | Assun  | nptions and Complexity                                          | 47  |

|   |     | 4.1.1  | The Complexity of NSDS                                          | 50  |

|   | 4.2 | Const  | ructive Heuristic Scheduling                                    | 53  |

|   |     | 4.2.1  | Constructive Heuristic Scheduling Formulation                   | 53  |

|   |     | 4.2.2  | Constructive Heuristic Scheduling Solution                      | 58  |

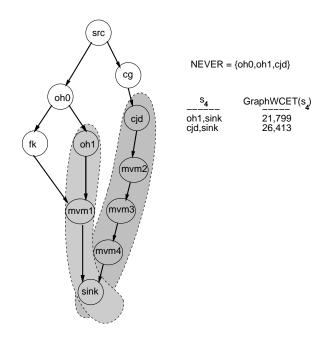

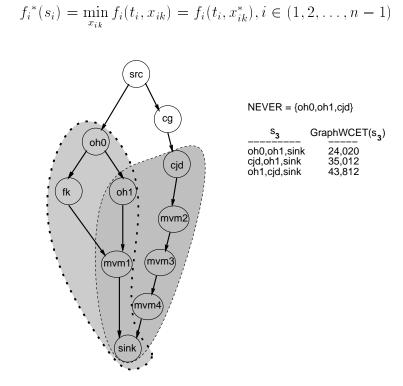

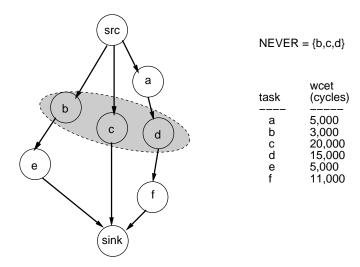

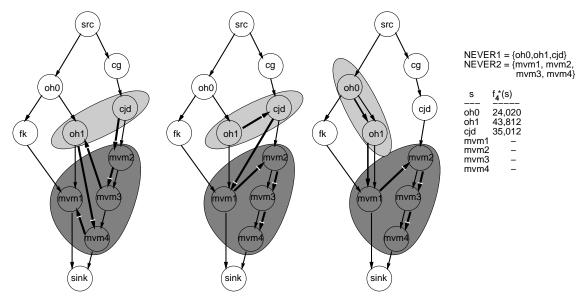

|   |     | 4.2.3  | Multiple $NEVER$ Sets of Hardware-Tasks                         | 65  |

|   |     | 4.2.4  | Complexity Analysis                                             | 69  |

|   |     | 4.2.5  | Practical Considerations for the Calculation of $\mathit{WCET}$ | 70  |

|   | 4.3 | Conte  | xt Switch Cost and Out-of-order Execution                       | 72  |

|   |     | 4.3.1  | Upper bound on extra calls to the Priority Scheduler and Con-   |     |

|   |     |        | text Switch                                                     | 73  |

|   |     | 4.3.2  | Instruction Cache Analysis                                      | 83  |

|   |     | 4.3.3  | Total Upper Bound on WCET                                       | 86  |

|   |     | 4.3.4  | Constructive Heuristic Scheduling with Out-of-order Execution   | 87  |

|   | 4.4 | Task S | Splitting                                                       | 93  |

|   | 4.5 | Critic | al Regions                                                      | 96  |

|   | 4.6 | Sumn   | nary                                                            | 98  |

| 5 | Imp | olemen | tation and Experimental Results                                 | 99  |

|   | 5.1 | Design | n System Implementation                                         | 99  |

|   |     | 5.1.1  | SERRA Run-Time Scheduler Analysis and Synthesis                 | 101 |

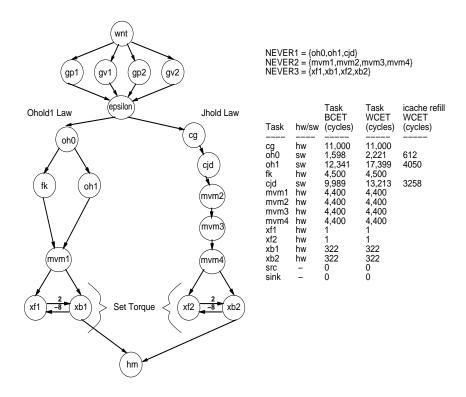

|   | 5.2 | Design | n Case Study: PUMA Robot Arm                                    | 103 |

|   |     | 5.2.1  | Two PUMA Arms                                                   | 104 |

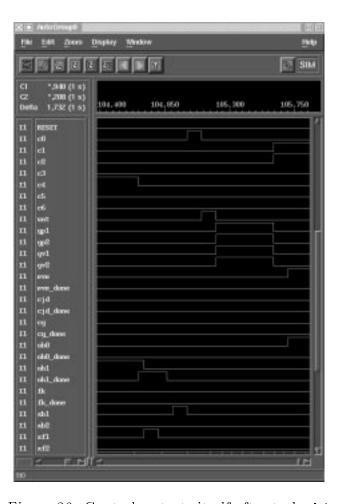

|   |     | 5.2.2  | Verilog Simulation                                              | 109 |

|   |     | 5.2.3  | Run-Time Scheduler Software                                     | 111 |

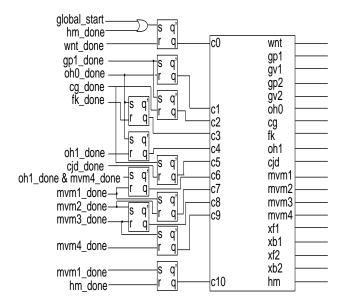

|   |     | 5.2.4  | Run-Time Scheduler Hardware                                     | 113 |

|              |                 | 5.2.5   | Running the Simulation                                   | 117 |

|--------------|-----------------|---------|----------------------------------------------------------|-----|

|              |                 | 5.2.6   | Design Gains                                             | 121 |

|              | 5.3             | Design  | n Case Study: Haptic Robot                               | 122 |

|              |                 | 5.3.1   | Original Design                                          | 123 |

|              |                 | 5.3.2   | Haptic Control Implemented with Split Run-Time System $$ | 126 |

|              |                 | 5.3.3   | System Architecture                                      | 129 |

|              |                 | 5.3.4   | Software Generation                                      | 131 |

|              |                 | 5.3.5   | Future Directions                                        | 133 |

|              | 5.4             | Summ    | nary                                                     | 135 |

| 6            | Con             | clusio  | ns and Future Work                                       | 137 |

|              | 6.1             | Summ    | nary                                                     | 137 |

|              | 6.2             | Future  | e Work                                                   | 140 |

| $\mathbf{A}$ | bbre            | viation | as and Symbols                                           | 142 |

| Bi           | Bibliography 14 |         |                                                          | 145 |

| $\mathbf{A}$ | ΑN              | /Iathen | natical Program Formulation                              | 155 |

# List of Tables

| 1  | Link between Verilog HDL Constructs and Control-Flow Expressions    | 26  |

|----|---------------------------------------------------------------------|-----|

| 2  | Entry Table for Software-Tasks                                      | 40  |

| 3  | Constructive Heuristic Scheduling Example Stage $n-1=4$             | 63  |

| 4  | Constructive Heuristic Scheduling Example Stage 3                   | 63  |

| 5  | Constructive Heuristic Scheduling Example Stage 2                   | 64  |

| 6  | Constructive Heuristic Scheduling Example Stage 1                   | 65  |

| 7  | WCET Calculation Example                                            | 72  |

| 8  | WCET Calculation Example                                            | 92  |

| 9  | Code space, $BCET$ and $WCET$ for sw-tasks                          | 107 |

| 10 | Results for the synthesis of hw-tasks                               | 108 |

| 11 | Code space for software tasks                                       | 132 |

| 12 | Code space for hardware tasks                                       | 133 |

| 13 | Statistics for Xilinx 4020E Mapping                                 | 134 |

| 14 | WCET found and run times for Constructive Heuristic Scheduling ver- |     |

|    | sus AMPL.                                                           | 157 |

# List of Figures

| 1  | Vulcan Synthesis Tool in context                                     | 12 |

|----|----------------------------------------------------------------------|----|

| 2  | CoWare simulation paradigm and sample implementation                 | 17 |

| 3  | THALIA2 Synthesis from CFEs                                          | 28 |

| 4  | PUMA Arms (Courtesy of the Computer Science Robotics Lab at Stan-    |    |

|    | $\mathrm{ford}) \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 33 |

| 5  | Robotics Example: Concurrent Control Algorithms                      | 34 |

| 6  | Tool Flow and Target Architecture                                    | 35 |

| 7  | Target Architecture                                                  | 38 |

| 8  | Robotics Example: Main Task                                          | 42 |

| 9  | Flattened CDFG of Robot Arm Controller                               | 43 |

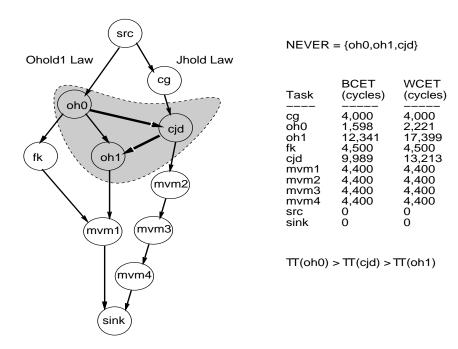

| 10 | DAG, $BCET$ and $WCET$ : The leftmost column shows the task names,   |    |

|    | the middle column shows the Best-Case Execution Time, and the right- |    |

|    | most column shows the Worst-Case Execution Time                      | 49 |

| 11 | Example transformation of an SRTD problem to an NSDS problem         | 52 |

| 12 | GraphWCET Example                                                    | 55 |

| 13 | Constructive Heuristic Scheduling Example Stage 3                    | 57 |

| 14 | Calculate $WCET$ Algorithm                                           | 60 |

| 15 | Constructive Heuristic Scheduling Algorithm                          | 61 |

| 16 | Sample DAG With Optimal Schedule Not Found By Heuristic: The                                       |     |

|----|----------------------------------------------------------------------------------------------------|-----|

|    | constructive heuristic scheduling algorithm finds order $(\mathtt{d},\mathtt{b},\mathtt{c})$ which |     |

|    | yields a $WCET$ of 43,000; however, the optimal order is $(b,d,c)$ , which                         |     |

|    | yields a $WCET$ of $40,000$                                                                        | 66  |

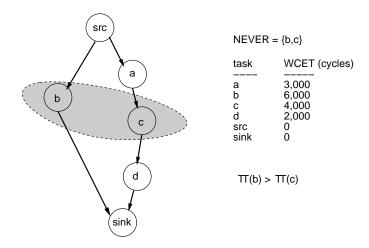

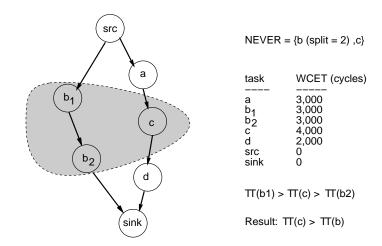

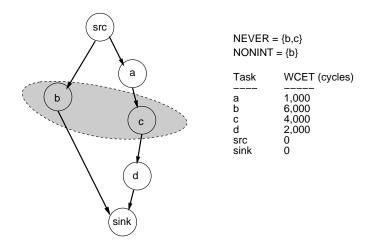

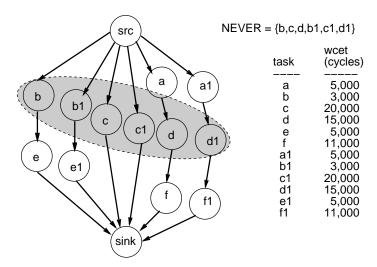

| 17 | Multiple $NEVER$ Set Example                                                                       | 67  |

| 18 | Constructive Heuristic Scheduling Algorithm with Multiple $NEVER$                                  |     |

|    | Sets                                                                                               | 68  |

| 19 | DAG, $WCET$ and $\Pi$ Example                                                                      | 75  |

| 20 | DAG With Out-of-order Execution Example                                                            | 76  |

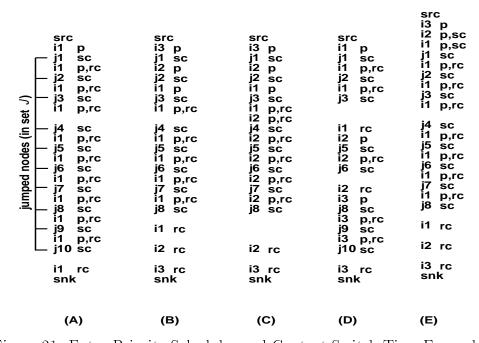

| 21 | Extra Priority Scheduler and Context Switch Time Examples                                          | 77  |

| 22 | Execute Out-of-order Algorithm                                                                     | 88  |

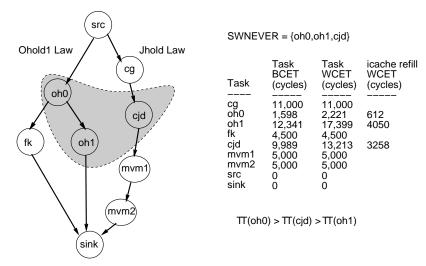

| 23 | Example With $\mathit{WCET}$ Calculation of Instruction Cache Refill Time .                        | 90  |

| 24 | Constructive Heuristic Scheduling Example of Suboptimal Result                                     | 94  |

| 25 | Example of Scheduling with Task Splitting                                                          | 95  |

| 26 | Example Specification of Noninterruptible Task                                                     | 96  |

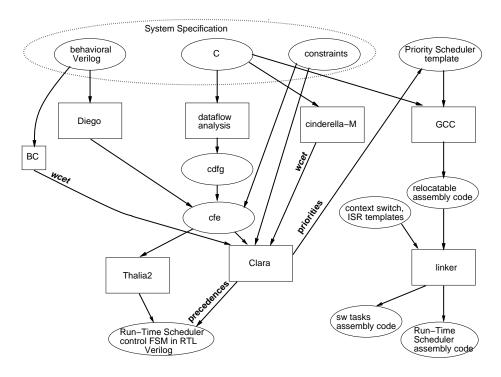

| 27 | Tool Flow and Target Architecture                                                                  | 100 |

| 28 | Block diagram of Serra: the boxes indicate tools and the ovals indi-                               |     |

|    | cate data.                                                                                         | 101 |

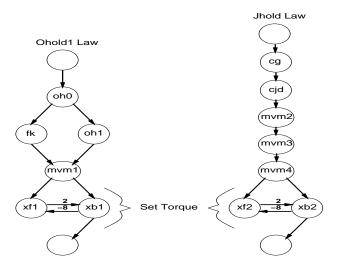

| 29 | Directed Acyclic Graphs of Ohold1 Law, Set Torque, and Jhold Law                                   |     |

|    | with Relative Timing Constraints                                                                   | 104 |

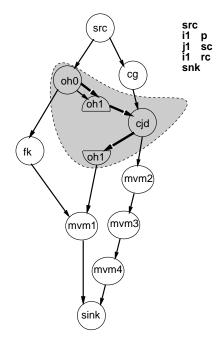

| 30 | DAG of Robot Arm Controller with Relative Timing Constraints                                       | 105 |

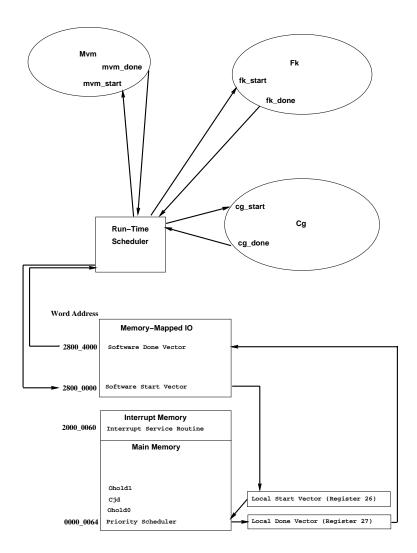

| 31 | Final Hardware Portion of Run-Time Scheduler                                                       | 106 |

| 32 | Simplified Block Diagram of the Simulation                                                         | 110 |

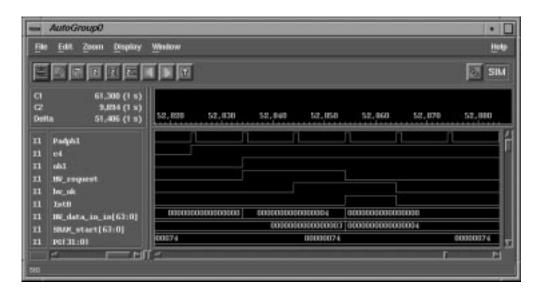

| 33 | Interrupt Asserted                                                                                 | 117 |

| 34 | PC Jumps to Start Address for Interrupt Service Routine                                            | 118 |

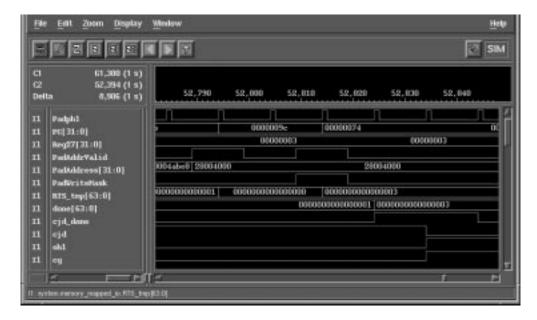

| 35 | Software task cjd completes                                                                        | 119 |

| 36 | Control restarts itself after task xb1                                                             | 120 |

| 37 | Haptic Robot With Graphics                                         | 122 |

|----|--------------------------------------------------------------------|-----|

| 38 | System Architecture                                                | 123 |

| 39 | Sphere Characterization                                            | 124 |

| 40 | Synopsys-Xilinx Tool Flow                                          | 127 |

| 41 | Run-Time Scheduler Control Communication                           | 128 |

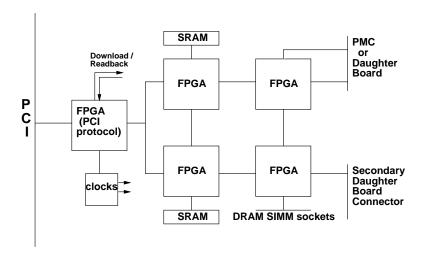

| 42 | PCI Pamette Version 1 – Architecture                               | 130 |

| 43 | Teapot Graphical Object With Proxy                                 | 131 |

| 44 | AMPL data for dagopt problem                                       | 155 |

| 45 | AMPL model for dagopt problem                                      | 156 |

| 46 | The dagopt2 problem, generated from the dagopt problem (Figure 16) |     |

|    | by doubling the number of tasks                                    | 158 |

## Chapter 1

## Introduction

The use of Computer-Aided Design (CAD) and synthesis tools in system-level design of digital systems has gained large acceptance in industry and academia. Synthesis/CAD tools automate portions of the design process, allowing designers to spend more time at higher levels of abstraction. Thus, synthesis tools support (i) more efficient exploration of the available design space, (ii) the production of correct and optimal (in some sense) circuits, and (iii) a reduction in time-to-market. These three characteristics drive the increasing use of synthesis tools in design today.

Additionally, several important trends in system-level design affect the use of synthesis. First of all, there is a significant movement towards core-based design, where pre-designed cores – such as processor and microcontroller cores – are used in system designs. Such core usage adds value through design reuse and the selling of Intellectual Property (IP). Why reinvent a component which another design team has already spent six months or more optimizing? Instead, both time and effort is saved by purchasing the component as IP.

A second trend in system-level design is the move to System-on-a-Chip (SoC) designs. For example, instead of making a board with eight separate chips, why not place all eight designs on the same chip? With ever decreasing transistor sizes, this is

a real possibility for more and more systems. However, placing a system on a single Integrated Circuit (IC) requires the integration of many heterogeneous components, such as digital, analog and memory.

A third trend to help deal with the enormous complexity is the move towards standards. This is evident in several initiatives, including the Virtual Sockets Interface Alliance (VSIA)[DF98], the European CAD Standards Initiative (ECSI)[AM98], and Reusable Application-Specific Intellectual Property Developers (RAPID)[RK98]. All three seek the establishment of open standards for the easy and reliable interfacing of cores designed by separate design teams.

The direction indicated by these trends is clear. New system-level design methodologies and CAD tools are needed.

## 1.1 Hardware/Software Co-Design

We consider the design of mixed hardware/software systems, such as embedded systems and robots. Most of today's hardware/software systems are designed by deciding up front what functionality will be implemented in hardware and what functionality will be implemented in software, with relatively few changes as the system design progresses. The research of hardware/software co-design targets altering this design strategy.

We aim at providing CAD tools that help bring hardware and software design flows closer together in order to allow designers to make tradeoffs between software and hardware and thus more quickly evaluate design alternatives.

Approaches to hardware/software co-design of embedded systems [MS96, Mic97] can be differentiated in several ways. One way is to consider the system-level specification, which is either homogeneous (i.e. in a single specification language) or heterogeneous (i.e. involving multiple modeling paradigms). Another way to differentiate

approaches is to distinguish how the CAD tool partitions the system specification: approaches consider either fine-grained partitions, i.e. at the operation or basic block level, or coarse-grained partitions, i.e. at the process or task level ([HE96] defines granularity in a slightly different way). For example, the Cosyma system (Section 2.1.1 [OBE+97]), the VULCAN system (Section 2.1.2 [Gup95]) and the POLIS system (Section 2.1.3 [BCG+97]) can be classified as homogeneous and fine-grained approaches, while the Coware system (Section 2.1.4 [MBL+96]) and the approach of Adams and Thomas [AT95] are heterogeneous and coarse-grained. The method using the Speccharts language [NVG92] supports homogeneous specification in VHDL with both fine- and coarse-grained partitioning. We take the heterogeneous and coarse-grained approach in this thesis.

There has been much previous work in hardware-software partitioning [Gup95, MBL<sup>+</sup>96, MS96]. However, system designs modeled by heterogeneous specifications are often already partitioned by designers into modules or tasks. Whereas some optimality is lost in using a coarse granularity in partitioning, the resulting implementation is often closer to what designers expect, and interfacing hardware to software blocks is easier. We assume the availability of automated interface generation similar to [COB95, MBL<sup>+</sup>96].

Designers of real-time embedded systems often have timing constraints that they must meet for the design to be successful. To support soft and hard real-time constraints, system designers need tight bounds on execution delays. In hardware/software co-design, scheduling resources to meet these tight bounds is a critical problem because there may be parallel threads of execution in the application with the same resource required by different threads.

In hardware/software co-design an important problem is the management of software routines and their coordination with hardware. An indispensable component to a system of cooperating hardware and software is a run-time scheduler. One approach to scheduling is to come up with a static schedule for hardware and software operations. However, the sequence of hardware and software tasks can change dynamically in complex real-time systems, since such systems often have to operate under many different conditions. For example, a robotics system which comes into contact with a hard surface may have to change its force control algorithm, along with its attendant sensor set, estimators, and trajectory control routines. Furthermore, there may be data-dependent and memory-dependent delays in execution, especially if the software runs on a processor core with caches. Thus, in many hardware/software systems, dynamic scheduling is a necessity.

One clear and easy solution is to put the run-time system in software and suitably design the hardware such that it can be controlled from the software. Unfortunately, software schedulers may not be predictable as far as being able to satisfy real-time constraints. Therefore, this thesis proposes implementing the time-constrained portion of the scheduler in hardware, where delays are accurately known. Thus, we present a strategy for a mixed implementation of a dynamic real-time scheduler in hardware and software, and a CAD tool, called Serra, to synthesize the necessary hardware and software for the run-time scheduler as well as analyze the performance of the system.

This dissertation focuses on analysis and synthesis of a custom dynamic runtime scheduler in hardware and software for embedded applications such as robotics control. In particular:

- We present a design approach for scheduling hardware/software tasks defined at a coarse level of granularity.

- We present analysis and synthesis techniques for scheduling mutually exclusive tasks to minimize Worst-Case Execution Time (WCET).

• We present a Verilog simulation of a robotics system using our scheduling approach as well as a small prototype of the split run-time scheduler working in an actual robotics prototype.

# 1.2 Requirements for Designing Hardware-Software Systems

One common requirement for system-level design targeted for mixed hardware-software implementation is the ability to carry out complex calculations. For example, in robotics control design, state space representation of the kinematics and dynamics of the arm can involve large matrices and require significant computational power [Lat91]. This complex functionality is often coupled with real-time constraints, such as the requirement to update robot arm torque inputs to its motors one thousand times a second. If missing the deadline may result in catastrophic results, such as damage to the robot or to the user, then we have a hard real-time constraint; if the deadline can be missed occasionally without significant negative effects, then we have a soft real-time constraint.

Timing constraints can be classified into two types: *rate* constraints, specifying the rate of execution of a particular set of operations or tasks, and *relative timing* constraints, specifying the minimum and maximum time separation between two operations or tasks. Both types of constraints are typical requirements in embedded systems.

In order to design a hardware-software system at a coarse level of granularity, several steps must be completed, not necessarily in this order:

- The system must be partitioned into tasks.

- Each task needs to be allocated to hardware or to software.

- The interface between tasks needs to be synthesized.

- The tasks need to be scheduled and synchronized.

The first three steps, while extremely important, have been addressed in other research and are not dealt with in this thesis. Instead, we focus on the last step, scheduling and synchronization.

Yet another requirement is the satisfaction of resource constraints. For example, there may be limited hardware, or all software-tasks might execute on the same CPU. Thus, tasks executed on the same hardware or on the same CPU cannot be scheduled at the same time, but must be mutually exclusive: one task must stop executing before the other begins to execute on the same resource. Notice that satisfying this scheduling requirement can pose a difficult optimization problem since the same task may be needed in concurrent control flows.

### 1.2.1 Scheduling at Different Levels

We emphasize here the differences between scheduling in high-level synthesis and scheduling in system-level synthesis. In high-level synthesis, the main emphasis is the scheduling of operations within a basic block. Optimality of a design in high-level synthesis is usually given in terms of the optimality of the execution time in basic blocks or the cost of resources in basic blocks, such as the number of multipliers, adders or multiplexors. In system-level synthesis, on the other hand, we have to consider the interactions that cross basic block boundaries as well. When the system is partitioned in basic blocks some of the interactions of the system are converted into environmental constraints, such as relative timing constraints and precedence constraints, which should guide the scheduling tool in finding a feasible and optimal implementation. Whenever these environmental constraints cross implementation paradigms – namely, hardware and software – appropriate synchronization must be

added as well.

### 1.3 Objectives and Contributions

In this thesis, we present a system-level scheduling methodology and CAD tool. We look at a system as a collection of tasks, where a task is a hardware module or software thread. We automate the synchronization and scheduling of tasks in hardware and in software. In order to achieve this automation, we need both analysis of the system and synthesis for the run-time scheduler implemented in hardware and in software.

Specifically, we present the following contributions to the field of scheduling for hardware-software systems:

- Design Style for Scheduling. We will present a simple design style for representing tasks that is independent of the tasks' implementation in hardware or in software. The representation will allow for dynamic scheduling of the tasks, where by dynamic we mean that the exact time when each task starts and finishes is not statically determined but instead is decided at run-time.

- Co-Synthesis of a Hardware-Software Run-Time Scheduler. We will show how, given the control-flow of the tasks in the system, we can synthesize a run-time scheduler partly implemented in hardware and partly implemented in software. Such a mixed implementation can leverage the advantages of both domains.

- Rate-Constraint Satisfaction Analysis. We will present techniques for analysis of the satisfaction of a single hard real-time rate constraint on the system, as is typical in robotics applications. The analysis will go hand-in-hand with the scheduling of the tasks and the generation of the run-time scheduler.

- Resource Constraints. We will show how our scheduler synthesis procedure

satisfies resource constraints, in hardware and software, while predictably satisfying timing constraints.

• Application to Robotics. We will present a full analysis, synthesis, and simulation of a hardware/software implementation of a robotics control system. We will also describe a small prototype of a split hardware/software scheduler to control a force-feedback Haptic robot using a Pentium<sup>TM</sup> for the software and Xilinx FPGAs for the hardware.

#### 1.4 Thesis Outline

This chapter gives an introduction and motivation for the thesis. Chapter 2 describes some of the previous work in hardware/software co-design as well as some related work from other areas. We next give an overview of our target architecture and system-level scheduling design style in Chapter 3. The chapter also briefly describes the very small kernel running on the microprocessor core.

Chapter 4 presents the real-time analysis used to analyze whether the final system will meet its timing and resource constraints. A heuristic scheduling algorithm is described in detail, together with extensions to provide support for preemptible tasks and semaphores in software.

Chapter 5 presents two design examples and how they were solved using the scheduling approach presented in this thesis. Finally, in Chapter 6, we will present some concluding remarks and some ideas for future research.

## Chapter 2

## Background

From the wide array of previous research in hardware/software co-design, hardware scheduling, and scheduling algorithms for real-time systems, we examine a few representative samples which most directly impact the research of this dissertation.

# 2.1 Previous Hardware/Software Co-Design Systems

We will first examine two systems which focus on hardware/software partitioning, after which we will examine two other systems which provide particular environments for hardware/software co-design. The next two sections exemplify two opposite approaches to hardware/software partitioning: (1) start with a software solution and migrate parts of the specification to hardware, and (2) start with a hardware solution and migrate parts of the specification to software.

#### 2.1.1 **COSYMA**

The Cosyma (Cosymthesis for eMbedded micro Architectures) system aims at speeding up software execution to meet timing constraints [EHB<sup>+</sup>96, OBE<sup>+</sup>97]. The speedup is achieved by using dedicated hardware to implement some of the functionality originally calculated by software. The original specification is in  $C^x$ , a minimum extension of the C programming language to allow parallel processes. Rate constraints are specified at the process level, while input/output timing constraints can only be handled in a few specialized cases.

The original  $C^x$  specification is compiled into an **Extended Syntax Graph** of the code, annotated with local and global data flow information. Timing information is calculated using several approaches, including profiling and symbolic analysis [EY97]. With this timing analysis, COSYMA can identify which constraints are met and which are not met with the all-software solution. Next comes partitioning.

Hardware/software partitioning occurs at the basic block level, which is seen as a manageable compromise between fine-grained (at the level of individual instructions) and coarse-grained (at the level of processes or threads) partitioning. For basic blocks implemented with software, a mixed profiling/static analysis technique is used to estimate the worst case execution time (WCET) of the software code [EY97].

Basic blocks that are implemented in hardware are assumed to not have any pointers. High-level synthesis is performed by the **Braunschweig Synthesis System** which produces Register-Transfer-Level (RTL) output for the *Synopsys Design Compiler*<sup>TM</sup> (DC<sup>TM</sup>). DC<sup>TM</sup> then produces a final netlist. Several techniques are used to estimate execution time of hardware, including **list scheduling** [Mic94] and **path-based scheduling** [HE95].

Communication time is estimated based on the number of variables that need to be passed between hardware and software for a given partition. Burst-mode communication is not supported. Cosyma uses **simulated annealing** in the partitioning process. Tens of thousands of possible hardware/software partitions are considered very quickly (less than a minute) in a typical run.

Cosyma was originally targeted to single processor with one coprocessor with shared memory communication but has recently been expanded to target multiple heterogeneous processors and coprocessors running in parallel communicating over shared memory or point to point communication. Software processes mapped to the same processor are statically scheduled.

The final output of Cosyma are the hardware blocks, statically scheduled software processes, and appropriate communication primitives in hardware and in software. If a solution is generated, it is guaranteed to meet the specified rate constraints while choosing the smallest hardware cost from among the partitions considered.

#### 2.1.2 VULCAN

The VULCAN tool aims at reducing ASIC hardware cost [Gup95]. The reduction in hardware cost is achieved by partitioning part of the design to software. The original specification is in Hardware-C [KD90], a Hardware Description Language (HDL) which can be synthesized down to netlists with the Olympus Synthesis System [DKMT90].

The Hardware-C description, with rate and relative timing constraints, is mapped to a fine-grained Control-Data Flow Graph (CDFG) intermediate representation. By fine-grained we mean that nodes in the CDFG correspond to individual computations such as arithmetic operations. This is the level at which VULCAN carries out hardware/software partitioning. At locations in the CDFG where a split between hardware and software occurs, appropriate Inter-Block Communication (IBC) vertices are added. IBC vertices for communication can be blocking, nonblocking, or buffered. In addition, software has to be generated for portions of the CDFG mapped

to software.

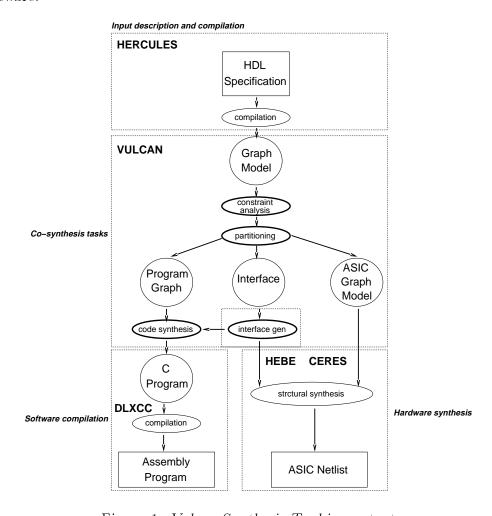

Figure 1: Vulcan Synthesis Tool in context

In order to map to software, all operations in the specified computation have to be serialized. Since the partial order of the CDFG specification is naturally parallel, this serialization problem is quite significant. A heuristic algorithm iterates over possible serial orders which also implement the partial order in the original specification without violating any rate constraints. The end result is a set of software program threads that can run with a custom software run-time scheduler. The runtime scheduling of software routines in VULCAN uses a non-preemptive scheme, for

example as provided by a prioritized FIFO scheduler [Gup95].

Hardware/software partitioning is carried out by means of a heuristic graph partitioning algorithm which runs in polynomial time [Gup95]. The partitioning algorithm considers different partitions of the CDFG specification between hardware and software, with the goal of minimizing hardware cost while still meeting timing constraints. A graphical representation of VULCAN is shown in Figure 1.

So far we have considered, from the large amount of research, two representative systems for hardware/software partitioning. Next we will review a system for control dominated hardware/software co-design and then a system for signal processing hardware/software co-design.

#### 2.1.3 POLIS

The POLIS system aims at providing a synthesis system targeted to design and analysis of embedded controller applications with a mixed implementation split between software and Application Specific Integrated Circuits (ASICs) [BCG<sup>+</sup>97]. The design is originally specified in a high level language such as Esterel [BG, BS91, Ber96], graphical FSMs, or Verilog/VHDL subsets.

The fundamental model of computation in POLIS is the Co-design Finite State Machine (CFSM), which supports a globally asynchronous, locally synchronous formal model of the design. Each transition of a CFSM takes non-zero time, is atomic, and can take on any value from a set of finite values. The assumption of non-zero transition time is made to avoid the composition problem of Mealy machines, due to undelayed feedback loops. Communication between CFSMs is by means of events which may be dropped (response to individual events is not guaranteed by POLIS).

In POLIS, the original design specification is compiled to a network of CFSMs. Sub-networks of CFSMs are targeted to hardware or to software; automatic synthesis supports either choice. Hardware synthesis is achieved by generating a synthesizable

HDL description and passing it on to a logic synthesis tool. Interfaces between hard-ware, software, and the external world are automatically synthesized in the form of cooperating circuits and software I/O drivers. For software executing on the same processor, a custom scheduler (round-robin, static cyclic, or static priority) can be compiled together with the CFSM-generated C-code, or a commercial Real-Time Operating System (RTOS) can be added by hand. Co-simulation is provided using the Ptolemy environment [BHLM94].

Thus, POLIS provides an environment where a designer can quickly evaluate choices of hardware/software partitioning, architecture selection, and scheduler selection. The output of POLIS is the C-code for the selected processor and the optimized hardware. This can be used, for example, in a board level prototype where the hardware is implemented with Field-Programmable Gate Arrays (FPGAs). The POLIS system is publicly available and has been used on several sample designs, such as a dashboard controller.

#### 2.1.4 **COWARE**

The goal of the CoWare system is to provide a design environment for heterogeneous hardware/software Digital Signal Processing (DSP) systems [MBL+96, VRBM96]. CoWare was developed at IMEC Belgium, and is the basis for a commercial product CoWare N2C [Cow98]. We describe here the original CoWare, based on published research papers and presentations at international workshops and conferences [MBL+96, VRBM96, VLM96a, VLM96b, RVBM96, MBL+97]. The CoWare hardware software co-design environment allows the cospecification of hardware and software components using existing languages such as VHDL, Data Flow Language (DFL)[WDC+94], Silage and C. CoWare provides unambiguous specification of interfaces between hardware and software, and correct synthesis of these interfaces in hardware and software by generating both hardware interfaces and device drivers.

COWARE is based on a data model of communicating processes and supports the gradual refinement of a high level description into an interconnection of programmable processors and dedicated, synthesizable hardware. The model supports the re-use and encapsulation of hardware and software by a clear separation between the functional behavior and the communication behavior of a system component.

The current version of CoWare supports the use of the ARM processor and various software tools such as a simulator and compiler for ARM and commercial VHDL simulators, logic synthesis and DSP synthesis tools.

The basis for this specification method is a data model for communicating processes. The model supports a strict separation between functional and communication behavior. Designs are made reusable by describing their functional behavior while maintaining an abstract model of their communication behavior. When a design is actually (re-)used in a system, the specification method allows one to refine the abstract communication model into a detailed behavior that is more appropriate in the system context. The same specification method is used to model off-the-shelf programmable processors, and these models are used in a processor independent hardware/software co-design methodology.

Synthesis tools and compilers are able to implement all processor, accelerator, and memory components once the global system architecture has been defined. The COWARE design environment provides for integration of existing design technology by automatically generating the interfaces that link these design environments and by interfacing the generated and off-the-shelf processors in a way that is consistent with the system specification.

Designing a system with the CoWare environment involves four steps: functional specification, architecture definition, communication selection, and component implementation [VRBM96].

Functional specification. A system is specified by means of communicating

processes that exchange data via channels. The behavior of a process can be entered using a host language such as C, DFL or VHDL.

**Architecture definition**. Optimally allocate processors, accelerators and memories, binding them to the functional specification. This interactive allocation and binding step includes the hardware/software partitioning.

Communication selection. Automatically generate the necessary software and hardware to make processors, accelerators and the different environments communicate. This step is performed via the SYMPHONY interface synthesis toolbox. Communication Blocks (CBs) provide pipelining and synchronization between accelerators. The communication between the hardware and the software for the ARM processor is more complex. The ARM interface includes address decoders, DMA channels, interrupts and I/O ports. Within the ARM, software drivers must be synthesized and linked to the processes running on the ARM.

Component implementation. All components in the system such as accelerator processors, interface hardware and software, memories, software running on a processor core, and debugging blocks are implemented using existing design environments. CoWare embeds different component compilers into the design environment, such as the ARM C-compiler and commercial VHDL/DSP synthesis environments.

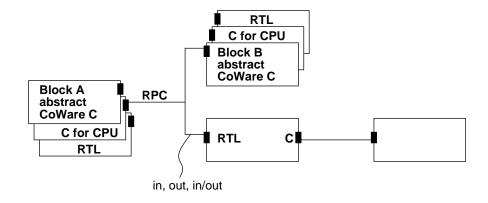

The basic model of communication in CoWare is the Remote Procedure Call (RPC). An example can be seen in Figure 2. The RPC connections can be seen between blocks. The cascaded blocks show different abstraction levels of the same functionality. The "abstract CoWare C" is C code written for CoWare and not targeted to any particular processor. "C for CPU" is C code targeted to a particular processor, e.g. an ARM. Finally, RTL is a Register-Transfer Level description in some HDL, typically Verilog HDL or VHDL. Notice that any RPC connection can communicate with an RPC connection at any other level of abstraction – abstract CoWare C, C for CPU, or RTL.

Figure 2: CoWare simulation paradigm and sample implementation

The bottom half of Figure 2 shows a hardware implementation of the RPC communication paradigm. CoWare synthesizes the software device driver as well as the logic in hardware to read data from the interface (I/F) bus.

Thus, a mixed system level specification in which part of the system is already implemented while another part is still specified at the behavioral level can be cosimulated. For this purpose, existing simulators can be integrated into the environment. Currently, Synopsys' VSS simulator for VHDL and the ARM instruction set simulators (both instruction accurate and cycle accurate) have been linked [MBL+97].

Coware operates very much like a linker, providing an executable that can be linked to instruction set simulators as well as other modules. The Coware methodology imposes increased demands on the generation of library elements. Often, abstract and detailed models of IP blocks do not exist. Existing IP blocks, for which

Verilog HDL code currently exists, require additional work to generate validated abstract CoWare C models.

#### 2.1.5 CHINOOK

The Chinook system aims at providing automated interface synthesis within a hard-ware/software co-design framework for embedded systems [BCO96, COB95, CB94, CWB94, COB92]. A single specification language, e.g. Verilog HDL, contains both behavioral and structural descriptions of the application, including information about the processors, peripheral devices, and communication interfaces that will be used. Parts of the behavioral specification are tagged for preferred implementation in a particular processor or dedicated hardware, with any untagged specification assumed to be implemented in software. All interactions with the devices and interfaces are specified using a procedural abstraction layer.

Process scheduling in Chinook is achieved by assigning different modes of operation to the overall system. A different schedule is associated with each mode. Timing watchdogs can disable modes and cause mode transitions. Upon changing to a new mode, the system starts running the corresponding schedule. Timing constraints may be intermodal or intramodal. Each mode has a periodic set of tasks, which is unrolled and scheduled under timing constraints, using an extension of the relative scheduling formulation [KM92]. With this scheduling technique, Chinook supports the mapping of an embedded system model to one (or more) processor and peripherals while ensuring the satisfaction of timing constraints.

Chinook synthesizes device drivers, interface logic, and bus logic necessary for communication among hardware and software. For processors with general purpose I/O ports, a heuristic allocates the ports to minimize interface logic; otherwise, memory-mapped I/O is used, which includes allocating address spaces. Knowledge about the interfaces of processors and devices, which Chinook needs to carry out

the synthesis, is captured in libraries.

New efforts in the Chinook system emphasize distributed architectures [HB97, OB97].

## 2.2 Hardware Scheduling

In this section we will briefly discuss some of the scheduling approaches used in high-level synthesis of hardware. In this case we have a model containing a set of operations and dependencies. The hardware implementation is assumed to be synchronous, with a given cycle-time. Operations are assumed to take a known integer number of cycles to execute. (We will later consider removing this assumption.) The result of scheduling, i.e., the set of start times of the operations, is just a set of integers. The usual goal is to minimize the overall execution *latency*, i.e. the time required to execute all operations.

### 2.2.1 Integer Linear Programming

The scheduling problem can be cast as an integer linear program (ILP) [Mic94], where binary-valued variables determine the assignment of a start time to each operation. Linear constraints require each operation to start once and to satisfy the precedence and resource constraints. Latency can also be expressed as a linear combination of the decision variables. The scheduling problem has a dual formulation, where latency is bounded from above and the objective function relates to minimizing the resource usage, which can also be expressed as a linear function. Timing and other constraints can be easily incorporated in the ILP model.

The appeal of using the ILP model is due both to the uniform formulation, even in presence of different constraints, and to the possibility of using standard solution packages. Its limitation is due to the prohibitive computational cost for medium-large cases. This relegates the ILP formulation to specific cases, where an exact solution is required and where the problem size makes the ILP solution viable.

#### 2.2.2 List Scheduling

Most practical implementations of hardware schedulers rely on *list scheduling*, which is a heuristic approach that yields good (but not necessarily optimal) schedules in linear (or overlinear) time. A list scheduler considers the timeslots one at a time, and schedules to each slot those operations whose predecessors have been scheduled, if enough resources are available. Otherwise the operation execution is deferred. Ties are broken using a priority list, hence the name.

## 2.2.3 Relative Scheduling

The synchronization of two or more operations or processes, often with exact cycle minimum and maximum separation timing constraints, is an important issue in hardware scheduling. Synchronization is needed when some delay is unknown in the model – the assumption that all operations take a known integer number of cycles to execute is removed. Relative scheduling is an extended scheduling method to cope with operations with unbounded delays [KM92] called anchors. The presence of an anchor means that a static schedule cannot be determined. Nevertheless, in relative scheduling the operations are scheduled with respect to their anchor ancestors. A FSM can be derived that executes operations in an appropriate sequence, on the basis of the relative schedules and the anchor completion signals. Relative scheduling support the analysis of timing constraints; when these constraints are consistent with the model, any resulting schedule generated is guaranteed to satisfy the constraints for any anchor delay.

#### 2.2.4 Conditional Process Graphs

A recently published paper considers the case where a Directed Acyclic Graph (DAG) specifies a set of processes with precedence constraints [EKP<sup>+</sup>98]. Each edge in the DAG may have a conditional associated with it.

The goal is to generate a static schedule which will minimize the execution time of the DAG for any allowable value of the conditionals. Since this may require activations of different tasks in different orders, they keep track of the possible paths using a schedule table. Alternative paths through the DAG are captured with BDDs. There may be a conflict, where, for example, the optimal schedule of one path requires that process  $P_3$  be scheduled at time  $t_k$ , while the optimal schedule of another path requires that  $P_3$  be scheduled at time  $t_l$ ,  $t_k \neq t_l$ . Conflicts are handled by adjusting one of the path schedules.

This technique is applicable to hardware/software systems. The end result is a distributed run-time scheduler composed of non-preemptive schedulers. Conditionals are broadcast so that individual schedulers can dynamically choose the appropriate schedule for the processes under their control. For the case where each process can be allocated either to hardware or to a programmable processor, then this scheduling technique applies to hardware/software co-design.

# 2.3 Software Scheduling

We will next examine some representative examples of previous approaches to scheduling for real-time software systems. The goal is software scheduling to meet real-time constraints. In the following, the assumption is that a large scale software system, with hundreds or thousands of individual tasks with many different periods and dead-lines, is being designed.

#### 2.3.1 Round-Robin Scheduling

The round-robin scheduling algorithm takes a small slice of time and allocates each process on a circular queue the time slice. If the process takes less than the time slice to execute, then the scheduler immediately goes to the next process in the circular queue. Otherwise it preempts the currently executing process at the end of the time slice and runs the next process in the queue. As the size of the time slice approaches infinity, the round-robin policy becomes the same as the First-Come-First-Served (FCFS) policy. While this algorithm is very predictable and by design avoids starvation and deadlock, unfortunately it can result in large average waiting time and many extra context switches.

#### 2.3.2 Shortest Job First

The shortest-job-first scheduling algorithm requires that each process have associated with it the length of uninterrupted CPU execution it needs next. This length can either be the entire length of the process or the length of the next CPU burst where it will heavily use the CPU (as opposed to waiting on I/O or for synchronization with other processes). Then, shortest-job-first assigns the CPU to whichever available process has the smallest length of uninterrupted CPU execution associated with it. When that process finishes, the CPU is assigned again to the process with the shortest length. While the shortest-job-first algorithm is optimal in terms of minimizing the average waiting time, it may result in missing timing constraints where another schedule would have met the timing constraints.

# 2.3.3 Rate-Monotonic Analysis

Rate Monotonic Analysis (RMA) [LL73] and Generalized Rate Monotonic Analysis (GRMA) [SRS94] both assume that tasks are independent and that each task has its

own period and deadline which are the same and never change. Furthermore, each task is assumed to have a constant run-time which does not change over time. In RMA, the *rate-monotonic priority assignment* assigns higher priorities to tasks with higher priorities. Such a priority assignment has been proven optimal in the sense that no other fixed priority assignment can schedule a set of tasks which cannot be scheduled (without missing deadlines) by the rate-monotonic priority assignment [LL73]. Liu and Layland were able to prove the following theorem:

**Theorem 2.1** A set of n independent periodic tasks scheduled by the rate-monotonic algorithm will always meet their deadlines for all task start times, if

$$\frac{C_1}{T_1} + \frac{C_2}{T_2} + \ldots + \frac{C_n}{T_n} \le n(2^{\frac{1}{n}} - 1)$$

where  $C_i$  is the execution time and  $T_i$  is the period of task  $\tau_i$ .

Theorem 2.1 ignores all overheads (assumed to be zero). The bound on the utilization  $n(2^{\frac{1}{n}}-1)$  rapidly converges to  $\ln 2=0.69$  as n becomes large.

GRMA adapts the RMA framework to deal with problems typically faced in real-time software systems. For example, a typical problem is *priority inversion*. This occurs when a lower priority process holds a critical resource, thereby preventing a higher priority process from executing when it interrupts and tries to access the critical resource: the priorities of the two process have been inverted because the lower priority process has, in effect, made itself higher in priority. Thus, GRMA supports the *priority ceiling protocol*, which avoids mutual deadlock arising from the priority inversion problem [SRL90, Raj91]. The deadlock is avoided by having any lower priority process holding a critical resource inherit the priority of any higher priority processes which try to access the resource, until the lower priority process

releases the resource (at which point the lower priority process resumes its original priority).

RMA has also been extended to account for release jitter and some cases of resource contention [ABD<sup>+</sup>95, ABR<sup>+</sup>93].

However RMA and GRMA both fail when the tasks have *precedence* constraints. We assume the presence of precedence constraints in the system in this dissertation.

## 2.3.4 Least Common Multiple

RMA has also been extended to allow precedence among tasks by formulating the problem as a big task with the length of the Least Common Multiple (LCM) of all the periods [Ram95, Ram90, PS89]. Unfortunately, this approach is usually impractical for hardware/software co-design for several reasons:

- First of all, it is difficult to handle a situation where the period and computation times are nondeterministic but bounded, since a period of a LCM does not represent all possible situations [YW96, YW95].

- Secondly, the task periods can be large and co-prime, resulting in a LCM too large to be practical.

- Thirdly, it discourages static allocation and scheduling because it treats different instances of the same task as different nodes in the LCM.

One approach to deal with the third problem mentioned above is to use the concept of an association array which keeps track of the priority level, allocation to hardware or CPU, deadline, and best/worst-case execution time for each copy of each task [DLJ97, DJ98].

#### 2.3.5 Real-Time Kernel in Hardware

A common approach is to encapsulate software scheduling algorithms into a fast but general purpose operating system, called a *Real-Time Operating System (RTOS)*. The basic idea is to provide the functionality needed by real-time software systems without the large overhead associated with traditional operating systems. A good overview of RTOS research in scheduling algorithms is contained in [SSNB95].

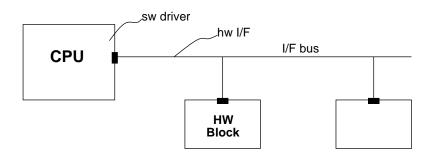

One interesting RTOS research direction implements a small real-time kernel in hardware to run in parallel with multiple processors [AFLS96, LSF95, Lin92, LS91]. The real-time kernel contains a scheduler with a priority scheduling algorithm, a dispatcher which controls the task switch mechanism, a wait queue for inactive tasks, a wait queue for tasks waiting for a time event, and a ready queue. A prototype of the system contains a VME bus connecting the real-time kernel in hardware, a bus arbiter in hardware, a large RAM, and three processors. To schedule a software task on a particular processor, the kernel triggers an interrupt on the processor, which results in placing the task id of the new task in a register on the processor. The new task id is read from that register, performing a task switch. The real-time kernel can handle a maximum of 64 tasks at 8 priority levels [AFLS96].

# 2.4 Control-Flow Expressions

Control-flow expressions (CFEs) [CM96, Coe96, CM97] support system-level specifications in an algebraic formalism that considers most of the language constructs used to model systems reacting to their environment, i.e. sequential, alternative, concurrent, iterative, and exception handling behaviors. Such constructs are found in languages such as C, Verilog HDL, VHDL, Esterel and StateCharts. CFEs can specify control flow that satisfies relative timing constraints (minimum and maximum

| Composition | HL Representation                                                                | CF Expression            |

|-------------|----------------------------------------------------------------------------------|--------------------------|

| Sequential  | begin $P$ ; $Q$ end                                                              | $p \cdot q$              |

| Parallel    | fork P; Q join                                                                   | p  q                     |

| Alternative | $\begin{array}{c} \mathbf{if}(C) \\ P \ ; \\ \mathbf{else} \\ Q \ ; \end{array}$ | $c: p + \overline{c}: q$ |

| Loop        | $\begin{array}{c} \mathbf{while} \ (C) \\ P \ ; \end{array}$                     | $(c:p)^*$                |

|             | $\begin{array}{c} \mathbf{wait} \ (!C) \\ P \ ; \end{array}$                     | $(c:0)^* \cdot p$        |

| In finite   | always P;                                                                        | $p^{\omega}$             |

Table 1: Link between Verilog HDL Constructs and Control-Flow Expressions

separation)[KM92] in hardware while also controlling dynamically the flow of execution.

#### 2.4.1 Formalism

Input events of a control-flow are specified by *conditionals*, which enable different blocks of the specification to execute based on the input. Output control signals are specified by *actions* which control execution according to the control-flow; for example, an action becoming asserted may indicate that a multiplier should begin execution. Table 1 shows the correspondence between CFEs and standard Verilog HDL control-flow constructs.

**Example 1** Suppose we have an alternative choice where based on conditional c, we execute either an adder, represented by CFE action a, or a multiplier, represented by CFE action m. The CFE description of this conditional choice, assuming that the adder and the multiplier are single-cycle actions, is as follows:  $c: a + \overline{c}: m \square$

Any CFE expression can be compounded sequentially or in parallel with any other CFE expression. Furthermore, with CFEs one can represent the control flow of most digital systems.

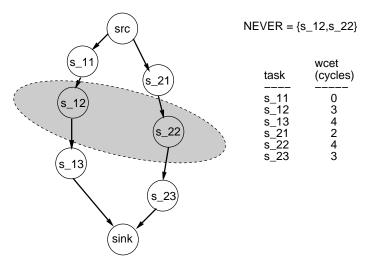

Synchronization constraints are specified through the use of NEVER and ALWAYS sets. NEVER sets model mutual exclusion; for example,  $NEVER = \{a, b, c\}$  indicates that actions a, b, and c can never be active at that same time. In a similar vein, tasks that must begin execution concurrently are specified through the use of ALWAYS sets; e.g.  $ALWAYS = \{a, b, c\}$  indicates that tasks a, b, and c must each begin execution at the same time. Thus, with conditionals, NEVER sets, and ALWAYS sets, CFEs can specify and consider constraints crossing concurrent blocks of the design, which are generally ignored in other synthesis tools.

Using conditional execution within a loop models an action with unbounded delay, e.g. as shown by the CFE construct  $(c:p)^*$ . Using a composition of these unbounded conditional executions can model a sequence of hardware and software tasks with unknown delay. Thus, with CFEs one can dynamically control the execution task, beginning a subsequent task after, and exactly after, all of its preceding tasks have finished execution.

Example 2 Suppose we want to execute the following tasks infinitely often: a followed by b, in parallel with d followed by e. Tasks a and d have nondeterministic delay. Tasks b and e take one cycle each. There are no constraints, i.e. no relative timing constraints, NEVER sets, or ALWAYS sets. Associating a CFE control signal and a CFE action with each task, we end up with the following expression (recall that in CFE semantics, \* indicates zero or more cycles, || indicates parallel execution,  $\cdot$  indicates serial execution, and  $\omega$  indicates an infinite loop):

$$(((c1:a)^* \cdot b)||((c2:d)^* \cdot e))^{\omega} \square$$

### 2.4.2 Synthesis with CFEs

The synthesis procedure begins by converting the control-flow expressions into an automaton where design constraints such as timing, resource and synchronization are incorporated. The synthesis is conservative in the sense that a solution is produced only if the specified constraints, such as relative timing constraints, are satisfied. In order to generate the control-units for the design, two scheduling procedures are used. The first procedure, called static scheduling, attempts to find fixed schedules for operations satisfying system-level constraints. The second procedure, called dynamic scheduling, attempts to synchronize concurrent parts of a circuit description by dynamically selecting schedules according to conditionals from the rest of the system. The solution of both scheduling problems are cast as Integer Linear Programming instances and solved using Binary Decision Diagrams.

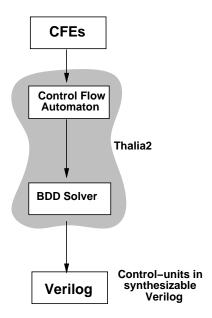

Figure 3: Thalia2 Synthesis from CFEs

#### **2.4.3** Thalia

The algorithms to synthesize a controller from a CFE specification have been implemented in a tool called Thalia [CM96, Coe96] which outputs a logic description. This logic description can be synthesized by commercial (e.g. Synopsys) or research (e.g. Olympus[DKMT90] or SIS[SSM+92]) synthesis systems. We have modified Thalia slightly in order to output synthesizable Verilog HDL; we call the new tool Thalia2, as shown in Figure 3.

### 2.5 Bounds on Execution Time

Real-time systems design requires bounds on execution time of the various components. The lower bound is often referred to as the Best-Case Execution Time (BCET), while the upper bound is referred to as the Worst-Case Execution Time (WCET). Recent previous approaches to such real time analysis have focused on software, since the performance analysis of ASICs is considered a well studied problem already. One such approach is that of the CINDERELLA tool [MWWL96, LM95], which this section discusses since we will use CINDERELLA in the timing analysis presented in this thesis.

CINDERELLA addresses the problem of determining *BCET* and *WCET* bounds for a given program executed on a given processor, assuming uninterrupted execution. Two important issues in solving this problem are (i) program path analysis, which determines which sequence of instructions will be executed in the worst case, and (ii) microarchitecture analysis, which requires modelling the hardware system to determines the *BCET* and *WCET* execution bounds for a given sequence of assembly instructions. CINDERELLA divides the assembly code into its basic blocks and extracts the control-flow among the blocks. Thus, explicit path enumeration is not required by CINDERELLA. Software is assumed to not have dynamic memory allocation nor recursive function calls. However, loops are allowed as long as the user

can provide upper bounds for each loop specified. Then, using an ILP formulation, CINDERELLA finds a *BCET* and a *WCET* for the program in clock cycles of the microprocessor clock. Target microarchitectures include the Intel i960KB processor and the Motorola 68000 processor [MWWL96, LM95]. We have ported CINDERELLA to the MIPS R4000 processor.

# 2.6 Summary

We have shown some representative samples of previous work in hardware/software co-design and algorithms for real-time scheduling of software. In hardware/software co-design, we have seen several systems for hardware/software partitioning and evaluation of different hardware/software tradeoffs. Only a few of the systems considered have as a primary goal the support of heterogeneous input in both a software language and an HDL, which will be the approach we take in this thesis. Finally, some of the previous work in scheduling for hardware and for finding bounds on the execution time of software was discussed.

None of the previous hardware/software co-design systems focus on run-time scheduling, and all place the run-time scheduler on the CPU (hardware is assumed to have a static schedule implied by the input description of the application). This thesis extends previous work to support dynamic interleaving of hardware-software execution, where by dynamic we mean that exact start times are not statically determined but instead are decided at run-time based on actual execution times. To achieve this, we present the first implementation of a run-time scheduler split partly in hardware and partly in software. Furthermore, real-time analysis will be provided to determine a WCET for the system.

In the next chapter, we will explain the target architecture for our system, the small kernel to control software running on a microprocessor, run-time scheduler implementation details, and the approach to modelling of the system.

# Chapter 3

# Target Architecture, Kernel, and System Model

We aim at supporting system-level design with hardware/software tasks custom designed for a target architecture. We refer to the tasks in hardware as hardware-tasks and to the tasks in software as software-tasks. We assume the existence of mature high-level synthesis tools and software compilers, as well as intellectual property in the form of processor and controller cores. We assume that the system requires both static scheduling, especially in the coordination of hardware-tasks, and dynamic scheduling, given the inexact delay of software and the randomness of the stimuli coming from the environment. A run-time scheduler must meet both of these scheduling requirements. We will present the Serra tool, which automates the generation of the run-time scheduler, thus providing for the synchronization and scheduling of system-level components in hardware and software.

Our approach assumes a *coarse-grained* partition of the system into tasks. We assume tasks model system components of significant sizes, and that the system consists of around ten to a hundred tasks. The tasks are assumed to model either hardware or software and to be written either in Verilog HDL or in C. This approach matches

design practice, where designers often describe their systems in a heterogeneous way, using description languages appropriate to the subsystem being implemented.

# 3.1 CAD Requirements

Figure 4: PUMA Arms (Courtesy of the Computer Science Robotics Lab at Stanford)

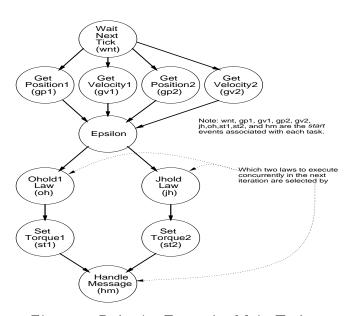

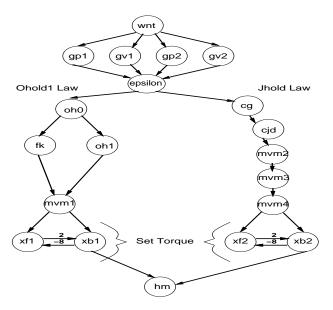

**Example 3** As a motivational example, consider the set of control algorithms of Figure 5. These algorithms calculate torques for the PUMA[AKB86, Uni84] robot arms shown in Figure 4.

We assume that the controller manages two arms at the same time, and thus any two of the algorithms may be selected in each execution. An execution of the arm controller must complete calculation of new torques for the arms once every millisecond. Since each arm has six degrees of freedom, only six new torque values need to be communicated for each update; thus, the amount of data flow in the system is small. However, the algorithms ("laws" in robotics terminology) need to maintain floating point matrices representing the kinematics and dynamics of the arms, so that the computation would be difficult to represent concisely in, for example, finite-state machines. This control approach is also drastically different than the fuzzy logic adaptive control in [ACJ96].

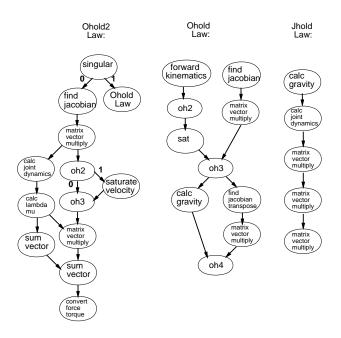

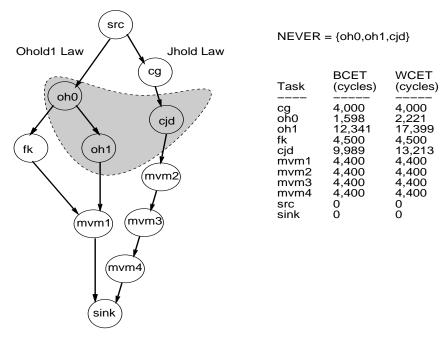

Figure 5: Robotics Example: Concurrent Control Algorithms

Figure 5 shows three of the ten different algorithms (laws) used with a PUMA arm; Ohold2 Law, Ohold Law, and Jhold Law are top-level tasks which call subtasks in a particular sequence. The *coarse-grained* partitions of Ohold2 Law, Ohold Law, and Jhold Law contains calls to many common subtasks. Some of the subtasks involve hardware components with timing constraints specified on a cycle basis.  $\square$

The CAD requirements for co-design of a system such as Example 3 are as follows. First, we need to satisfy hard real-time constraints imposed by some of the hardware components in the system as well as by external hardware. Second, we need to optimize the run-time system over calls to multiple tasks in hardware and software. This involves allocation of tasks to hardware and software as well as interface generation for communication. Third, we need to guarantee a hard real-time rate constraint across tasks in hardware and in software. The handling of multiple-rate constraints is beyond the scope of this thesis.

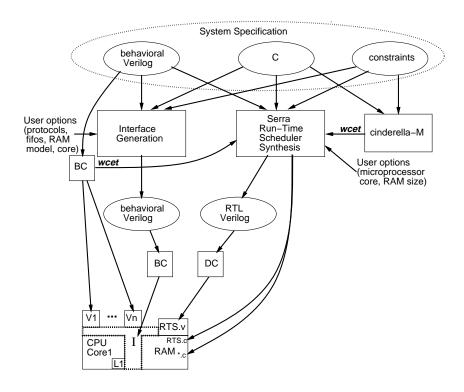

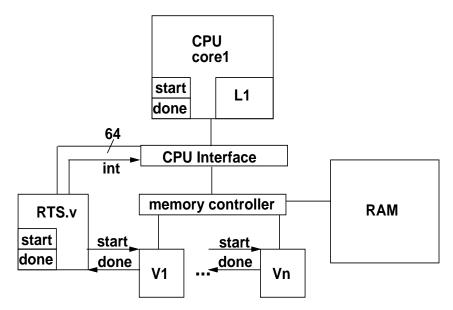

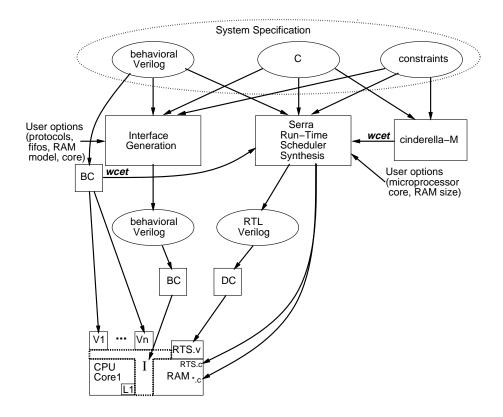

We design our run-time scheduler CAD tool, which we call Serra, to work with

Figure 6: Tool Flow and Target Architecture

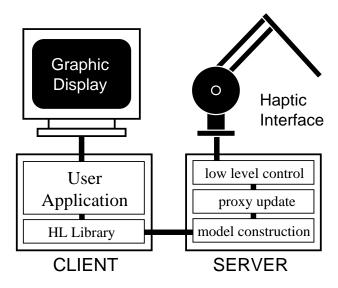

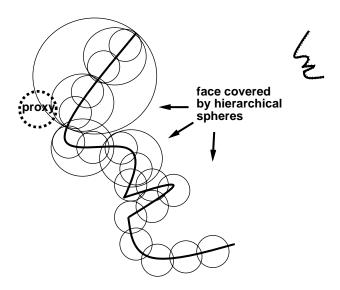

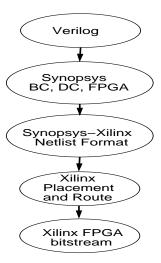

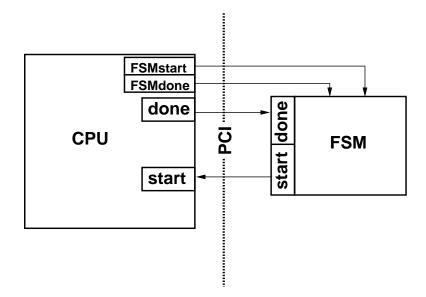

existing hardware synthesis and software compilation tools. Figure 6 shows the tool flow in which SERRA is embedded. Hardware-tasks are specified in Verilog HDL that can be synthesized by the Synopsys Behavioral Compiler<sup>TM</sup>[Kna96] (labeled BC in Figure 6; DC labels the Design Compiler<sup>TM</sup>). Software-tasks are written in C. Microprocessor cores, memories (DRAM, SRAM), FIFO models, and other custom blocks are assumed as available inputs to the system.