# **Checkpointing Apparatus and Algorithms for Fault-Tolerant Tightly-Coupled Multiprocessors**

**Dwight Sunada**

**Technical Report: CSL-TR-99-785**

**July 1999**

The initial phase of this research was supported by a financial grant from Hewlett-Packard Company.

## Checkpointing Apparatus and Algorithms for Fault-Tolerant Tightly-Coupled Multiprocessors

## **Dwight Sunada**

**Technical Report: CSL-TR-99-785**

**July 1999**

Computer Systems Laboratory

Departments of Electrical Engineering and Computer Science

Stanford University

William Gates Building, 4A-408

Stanford, California 94305-9040

<e-mail: pubs@shasta.stanford.edu>

## **Abstract**

The apparatus and algorithms for establishing checkpoints on a tightly-coupled multiprocessor (TCMP) fall naturally into three broad classes: tightly synchronized method, loosely synchronized method, and unsynchronized method. The algorithms in the class of the tightly synchronized method force the immediate establishment of a checkpoint whenever a dependency between two processors arises. The algorithms in the class of the loosely synchronized method record this dependency and, hence, do not require the immediate establishment of a checkpoint if a dependency does arise; when a processor chooses to establish a checkpoint, the processor will query the dependency records to determine other processors that must also establish a checkpoint. The algorithms in the class of the unsynchronized method allow a processor to establish a checkpoint without regard to any other processor. Within this framework, we develop four apparatus and algorithms: distributed recoverable shared memory (DRSM), DRSM for communication checkpoints (DRSM-C), DRSM with half of the memory (DRSM-H), and DRSM with logs (DRSM-L). DRSM-C is an algorithm in the class of the tightly synchronized method, and DRSM and DRSM-H are algorithms in the class of the loosely synchronized method. DRSM-L is an algorithm in the class of the unsynchronized method and is the first of its kind for a TCMP. DRSM-L has the best performance in terms of minimizing the impact of establishing checkpoints (or logs) on the running applications and has the least expensive hardware.

**Key Words and Phrases:** audit trail, checkpoint, fault tolerance, roll-back recovery, tightly-coupled multiprocessor

© Copyright by Dwight Sunada 1999 All Rights Reserved

| adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br>Michael J. Flynn                                                                                                                                                      |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

| David B. Glasco                                                                                                                                                           |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy. |

| Bernard Widrow                                                                                                                                                            |

| Approved for the University Committee on Graduate Studies:                                                                                                                |

|                                                                                                                                                                           |

## Acknowledgments

Starting from the 7th grade of intermediate school, I have hoped to obtain a Doctor-of-Philosophy degree in either (1) computer science or (2) a field related to computer science. More than 20 years later, I shall earn a Doctor of Philosophy (Ph. D.) in electrical engineering; my Ph. D. research is focused on the architecture of computer systems. Although I encountered many obstacles along the way to earning a Ph. D., I have finally fulfilled one of my childhood dreams.

Several people contributed to my accomplishment. At Stanford University, I thank both Professor Michael J. Flynn and Professor David B. Glasco for serving as my advisors. I thank Professor Bernard Widrow for being the 3rd member of my reading committee. I thank Professor John M. Cioffi for serving as the chairman of my orals committee and Professor Abbas El-Gamal for being the 4th member of my orals committee. In addition, I thank the colleagues in my research group and the students in the "EE 385B" seminar for listening to my numerous practice presentations (for the Ph. D. oral defense) and for offering helpful suggestions.

At the University of Houston (in Texas), I thank Professor Pauline Markenscoff for believing that I can do research. The University of Houston (UH) has a tiny fraction of the resources and the intellectual environment that Stanford University has. Research positions in computer architecture at UH were rare – if they even existed. Nonetheless, after I graduated with a Bachelor-of-Science degree in electrical engineering from UH in 1988 May, I looked for a summer job doing research in computer architecture. By sheer coincidence, Professor Markenscoff had an opening for such a job and hired me to do research on the subject of multiprocessors. In this research, I used computer simulation to develop algorithms for assigning subtasks (of a whole task) to the processors in a multiprocessor. This work and a strong letter of recommendation from Professor Markenscoff significantly helped me to successfully obtain a 3-year graduate fellowship (for graduate study at Stanford University) from the National Science Foundation in 1989. Also, this research culminated in my first significant paper: "Computation of Tasks Modeled By Directed Acyclic Graphs on Distributed Computer Systems: Allocation without Subtask Replication" on pages 2400 - 2404 in volume 3 of the 1990 IEEE International Symposium on Circuits and Systems. I am very grateful to Professor Markenscoff.

To complete my academic acknowledgments, I thank 3 teachers from secondary school for having taught me well. They are Ms. Dillion from my American-history class in the 10th grade (at Klein High School in Klein, Texas), Ms. Little from my science class in the 7th grade (at Strack Intermediate School in Klein, Texas), and Ms. Lacy in the 3rd grade (at Hidden Valley Elementary School in Houston, Texas). All 3 teachers asked me to remember them if I ever became famous. Since obtaining the Ph. D. is a type of fame, I now honor their request. I thank all 3 teachers for having taught me well.

In my personal life, I thank my grandfather, Chew Doo Wong, for his kindness towards me. I have suffered very many, painful experiences in my life; during almost all of these painful experiences, no person genuinely cared about me. In particular, I suffered one of these painful experiences when I was approximately 13 years old. At that time, my grandfather was in a position to help me, and he conscientiously helped me in a substantial way. Shortly thereafter, he passed away – into the kind and gentle place. Although more than 20 years have elapsed since his death, I still occasionally remember him and his kindness. I thank my grandfather very much for his kindness on that occasion long ago.

Finally, I dedicate this dissertation (and any benefit derived from it) to the hope that both (1) the adult survivors of child abuse and (2) abused children will someday find inner peace and joy. As for the victims who did not survive child abuse, I dedicate this dissertation (and any benefit derived from it) to the hope that they will find inner peace and joy in the kind and gentle place beyond this cruel world.

# **Table of Contents**

| Chapter 1. Introduction                                     | 1  |

|-------------------------------------------------------------|----|

| 1.1. Tightly-Coupled Multiprocessor (TCMP)                  | 1  |

| 1.2. Fault-tolerant TCMP                                    | 2  |

| 1.3. Research on Roll-back Recovery                         | 3  |

| Chapter 2. Background                                       | 5  |

| 2.1. Dependencies                                           | 5  |

| 2.2. Classes of Algorithms                                  | 10 |

| Chapter 3. Assumptions                                      | 12 |

| 3.1. Fault-tolerant Components                              | 12 |

| 3.2. Distinction between Processor and Directory Controller | 13 |

| Chapter 4. Distributed Recoverable Shared Memory (DRSM)     | 15 |

| 4.1. Introduction                                           | 15 |

| 4.2. Prior Work                                             | 15 |

| 4.3. Background: Recoverable Shared Memory (RSM)            |    |

| 4.3.1. Dependency Matrix                                    | 16 |

| 4.3.2. Last-Writer Indicator                                | 16 |

| 4.3.3. Checkpoint Counters                                  | 17 |

| 4.3.4. Memory for Tentative Checkpoint                      | 17 |

| 4.3.5. Memory for Permanent Checkpoint                      | 17 |

| 4.3.6. Establishing Checkpoints                             | 17 |

| 4.3.7. New Requests after Initiating Checkpoint             |    |

| 4.4. Apparatus of DRSM                                      | 19 |

| 4.5. Triggers of Checkpoint Establishment                   | 22 |

| 4.6. Establishing Tentative Checkpoints                     | 22 |

| 4.6.1. General Overview                                     | 22 |

| 4.6.2. Details                                              | 24 |

| 4.6.3. Dependent Processors and Dependent DRSM Modules      | 25 |

| 4.7. Establishing Permanent Checkpoints                     | 26 |

| 4.7.1. General Overview                                     | 26 |

| 4.7.2. Details                                              | 26 |

| 4.8 Additional Features                                     | 27 |

| 4.8.1. Artificially Dependent Processors                                            | 27   |

|-------------------------------------------------------------------------------------|------|

| 4.8.2. Arbiter                                                                      | 28   |

| 4.9. Recovery from a Fault                                                          | 28   |

| Chapter 5. Distributed Recoverable Shared Memory for Communication Checkpoints (DRS | M-C) |

|                                                                                     | 31   |

| 5.1. Introduction                                                                   | 31   |

| 5.2. Prior Work                                                                     | 31   |

| 5.3. Apparatus                                                                      | 32   |

| 5.4. Triggers of Checkpoint Establishment                                           | 33   |

| 5.5. Establishing Checkpoints                                                       | 33   |

| 5.5.1. General Overview                                                             | 33   |

| 5.5.2. Details                                                                      | 34   |

| 5.6. Recovery from a Fault                                                          | 35   |

| Chapter 6. Distributed Recoverable Shared Memory with Half of the Memory (DRSM-H)   |      |

| 6.1. Introduction                                                                   | 37   |

| 6.2. Apparatus                                                                      | 37   |

| 6.3. Memory Cache                                                                   | 39   |

| 6.4. Triggers of Checkpoint Establishment                                           |      |

| 6.5. Establishing Tentative Checkpoints                                             | 40   |

| 6.6. Establishing Permanent Checkpoints                                             | 41   |

| 6.6.1. General Overview                                                             | 41   |

| 6.6.2. Details                                                                      | 42   |

| 6.7. Recovery from a Fault                                                          | 43   |

| Chapter 7. Distributed Recoverable Shared Memory with Logs (DRSM-L)                 | 44   |

| 7.1. Introduction                                                                   | 44   |

| 7.2. Apparatus                                                                      | 44   |

| 7.3. Audit Trail                                                                    | 46   |

| 7.4. Optimizations                                                                  | 48   |

| 7.5. Triggers of Checkpoint Establishment                                           | 49   |

| 7.5.1. List of Triggers                                                             | 49   |

| 7.5.2. Context Switch                                                               | 49   |

| 7.6. Establishing Checkpoints                                                       | 50   |

| 7.7. Recovery from a Fault                                                          | 51   |

| 7.8. Pedagogical Example                                                            | 54   |

| 7.9. Optimal Size of Line Buffer and Counter Buffer                                 |      |

| 7.10. Detailed Description                                                          | 60   |

| Chapter 8 Simulation Environment and Benchmarks                                     | 61   |

| 8.1. Multiprocessor Simulator                                 | 61  |

|---------------------------------------------------------------|-----|

| 8.2. Benchmarks                                               | 62  |

| Chapter 9. Results and Analysis                               | 64  |

| 9.1. Overall Performance of Benchmarks                        | 64  |

| 9.2. Performance Impact of Establishing Checkpoints           | 71  |

| 9.2.1. Checkpoints                                            | 72  |

| 9.2.2. Negative Acknowledgments and Upgrade Misses            | 77  |

| 9.3. Checkpoint Data                                          | 80  |

| 9.4. Audit-Trail Data                                         | 83  |

| 9.5. Extent of Checkpoint Dependencies                        | 85  |

| 9.6. Memory Cache and Dirty-Shared Data                       | 85  |

| 9.7. DRSM Versus DRSM-L                                       | 87  |

| 9.8. Additional Observations                                  | 89  |

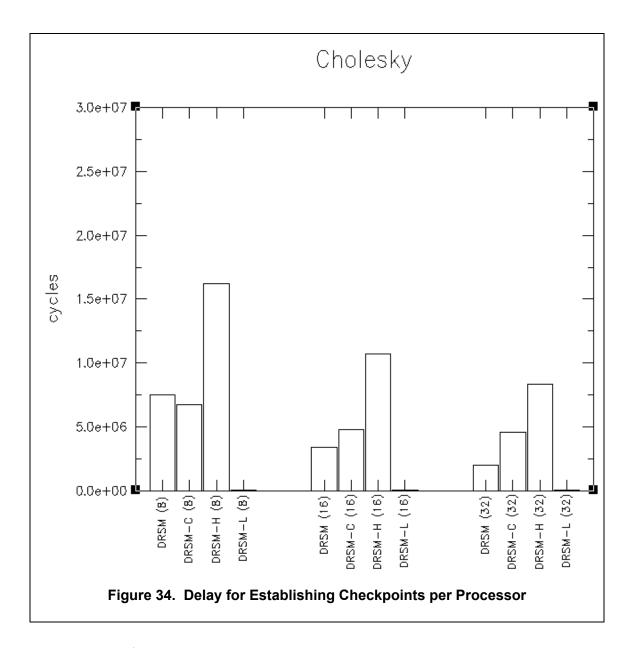

| 9.8.1. Delay for Establishing Checkpoints                     | 89  |

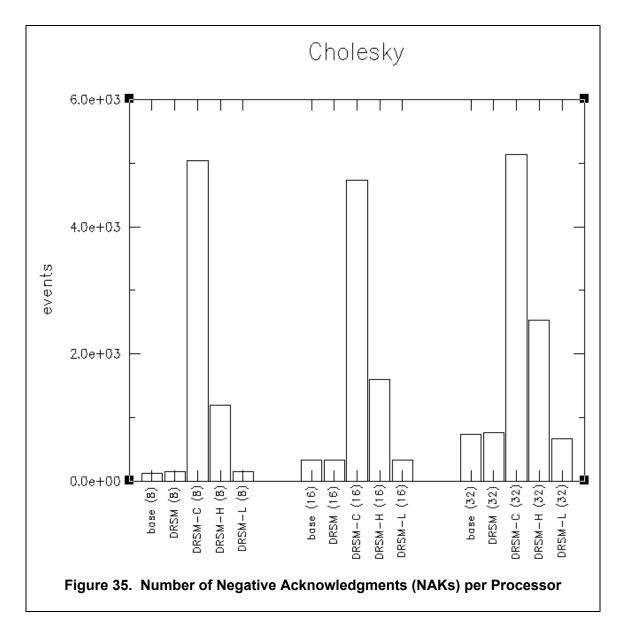

| 9.8.2. Number of Negative Acknowledgments (NAKs)              | 90  |

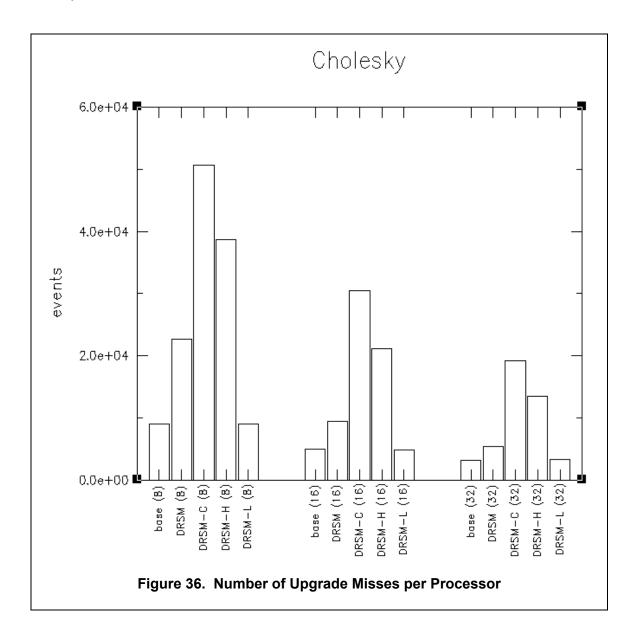

| 9.8.3. Number of Upgrade Misses                               | 93  |

| 9.9. High Rate of Checkpoints for All Processors              | 93  |

| Chapter 10. Conclusions                                       | 94  |

| 10.1. DRSM-C                                                  | 94  |

| 10.2. DRSM and DRSM-H                                         | 94  |

| 10.3. DRSM-L                                                  | 94  |

| 10.4. Future Work                                             | 95  |

| 10.4.1. Simulation                                            | 95  |

| 10.4.2. Proof of Concept                                      | 96  |

| Appendix A. Precise Description of DRSM-L                     | 97  |

| Appendix B. Results for Timer Expiration per 2,000,000 Cycles | 112 |

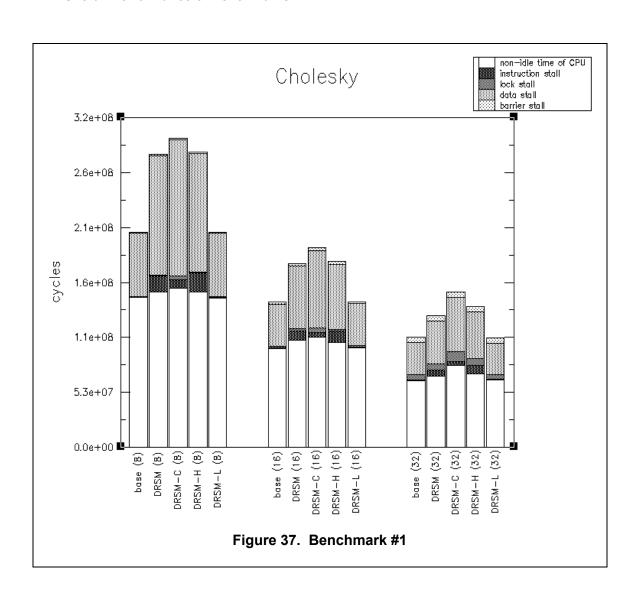

| B.1. Overall Performance of Benchmarks                        | 112 |

| B.2. Performance Impact of Establishing Checkpoints           | 118 |

| B.2.1. Checkpoints                                            | 118 |

| B.2.2. Negative Acknowledgments and Upgrade Misses            | 121 |

| B.3. Checkpoint Data                                          | 123 |

| B.4. Audit-Trail Data                                         | 126 |

| B.5. Extent of Checkpoint Dependencies                        | 126 |

| B.6. Memory Cache and Dirty-Shared Data                       | 127 |

| B.7. Additional Observations                                  | 129 |

| List of References                                            | 132 |

# **List of Tables**

| Table 1.   | Checkpoints for DRSM                                                                 | 73   |

|------------|--------------------------------------------------------------------------------------|------|

| Table 2.   | Checkpoints for DRSM-C                                                               | 74   |

| Table 3.   | Checkpoints for DRSM-H                                                               | 75   |

| Table 4.   | Checkpoints for DRSM-L                                                               | 76   |

| Table 5.   | Negative Acknowledgments and Upgrade Misses for DRSM                                 | 78   |

| Table 6.   | Negative Acknowledgments and Upgrade Misses for DRSM-C                               | 78   |

| Table 7.   | Negative Acknowledgments and Upgrade Misses for DRSM-H                               | 79   |

| Table 8.   | Negative Acknowledgments and Upgrade Misses for DRSM-L                               | 79   |

| Table 9. I | Data Saved per Processor per Checkpoint for DRSM                                     | 80   |

| Table 10.  | Data Saved per Processor for DRSM                                                    | . 80 |

| Table 11.  | Data Saved per Processor per Checkpoint for DRSM-C                                   | 81   |

| Table 12.  | Data Saved per Processor for DRSM-C                                                  | 82   |

| Table 13.  | Data Saved per Processor per Checkpoint for DRSM-H                                   | 82   |

| Table 14.  | Data Saved per Processor for DRSM-H                                                  | 83   |

| Table 15.  | Audit-Trail Data (entries in line buffer; entries in counter buffer; ratio)          | 84   |

| Table 16.  | Extent of Checkpoint Dependencies for DRSM                                           | 85   |

| Table 17.  | Extent of Checkpoint Dependencies for DRSM-H                                         | 85   |

| Table 18.  | Statistics about Dirty-Shared Data                                                   | 87   |

| Table 19.  | Timer-triggered Checkpoints: (number for processor #3; average for other processors) | )    |

|            |                                                                                      | 89   |

| Table 20.  | Checkpoints for DRSM                                                                 | 18   |

| Table 21.  | Checkpoints for DRSM-C                                                               | 19   |

| Table 22.  | Checkpoints for DRSM-H                                                               | 20   |

| Table 23.  | Checkpoints for DRSM-L                                                               | 21   |

| Table 24.  | Negative Acknowledgments and Upgrade Misses for DRSM 1                               | 21   |

| Table 25.  | Negative Acknowledgments and Upgrade Misses for DRSM-C                               | 122  |

| Table 26.  | Negative Acknowledgments and Upgrade Misses for DRSM-H                               | 122  |

| Table 27.  | Negative Acknowledgments and Upgrade Misses for DRSM-L                               | 123  |

| Table 28.  | Data Saved per Processor per Checkpoint for DRSM                                     | 23   |

| Table 29.  | Data Saved per Processor for DRSM                                                    | 124  |

| Table 30.  | Data Saved per Processor per Checkpoint for DRSM-C                                   | 124  |

| Table 31. | Data Saved per Processor for DRSM-C                                         | 125 |

|-----------|-----------------------------------------------------------------------------|-----|

| Table 32. | Data Saved per Processor per Checkpoint for DRSM-H                          | 125 |

| Table 33. | Data Saved per Processor for DRSM-H                                         | 126 |

| Table 34. | Audit-Trail Data (entries in line buffer; entries in counter buffer; ratio) | 126 |

| Table 35. | Extent of Checkpoint Dependencies for DRSM                                  | 126 |

| Table 36. | Extent of Checkpoint Dependencies for DRSM-H                                | 127 |

| Table 37. | Statistics about Dirty-Shared Data                                          | 128 |

## **List of Illustrations**

| Figure 1.  | Basic Architecture of Tightly-Coupled Multiprocessor (TCMP)                          | . 2 |

|------------|--------------------------------------------------------------------------------------|-----|

| Figure 2.  | Roll-back Dependency for Write-Read Interaction                                      | 6   |

| Figure 3.  | Checkpoint Dependency for Write-Read Interaction                                     | 7   |

| Figure 4.  | Roll-back/Checkpoint Dependency for Write-Write Interaction with Writes to Different |     |

| Words      |                                                                                      | . 8 |

| Figure 5.  | Roll-back Dependency for Write-Write Interaction with Writes to the Same Word        | 8   |

| Figure 6.  | Checkpoint Dependency for Write-Write Interaction with Writes to the Same Word       | . 9 |

| Figure 7.  | Dependencies to Classes of Checkpointing Algorithms                                  | 10  |

| Figure 8.  | Tightly-Coupled Multiprocessor (TCMP)                                                | 13  |

| Figure 9.  | Recoverable Shared Memory (RSM)                                                      | 16  |

| Figure 10. | Flow of Checkpoint                                                                   | 18  |

| Figure 11. | Distributed Recoverable Shared Memory (DRSM)                                         | 20  |

| Figure 12. | Transition of State for 2-Bit State Register                                         | 21  |

| Figure 13. | Flow of Tentative Checkpoint                                                         | 23  |

| Figure 14. | Flow of Permanent Checkpoint                                                         | 27  |

| Figure 15. | Distributed Recoverable Shared Memory for Communication Checkpoints (DRSM-C)         |     |

|            |                                                                                      | 32  |

| Figure 16. | Flow of Checkpoint                                                                   | 34  |

| Figure 17. | Distributed Recoverable Shared Memory with Half of the Memory (DRSM-H)               | 38  |

| Figure 18. | Flow of Permanent Checkpoint                                                         | 41  |

| Figure 19. | Distributed Recoverable Shared Memory with Logs (DRSM-L)                             | 45  |

| Figure 20. | Transition of State of Both Processor and 2nd-Level Cache                            | 46  |

| Figure 21. | Normal Execution of Processor                                                        | 55  |

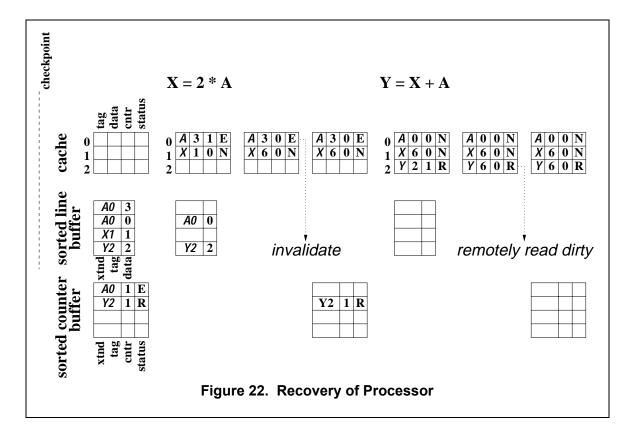

| Figure 22. | Recovery of Processor                                                                | 56  |

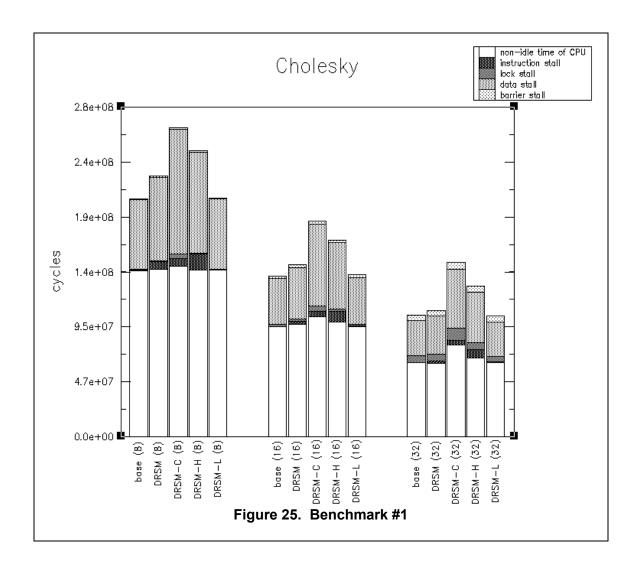

| Figure 23. | Completion of Recovery of Processor                                                  | 58  |

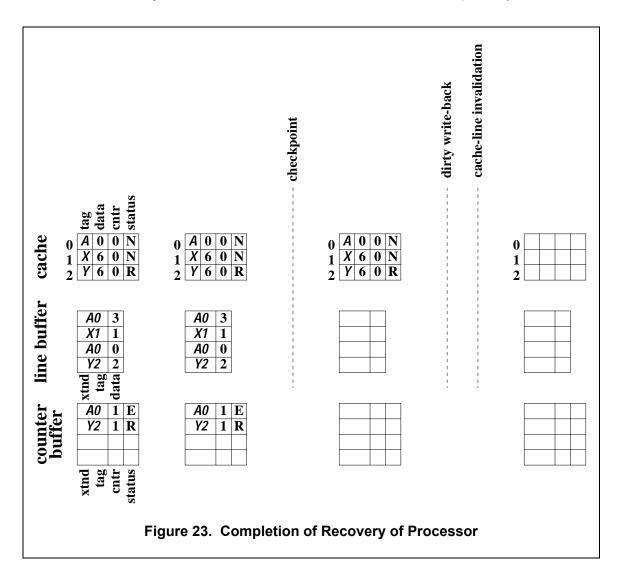

| Figure 24. | Base Multiprocessor                                                                  | 61  |

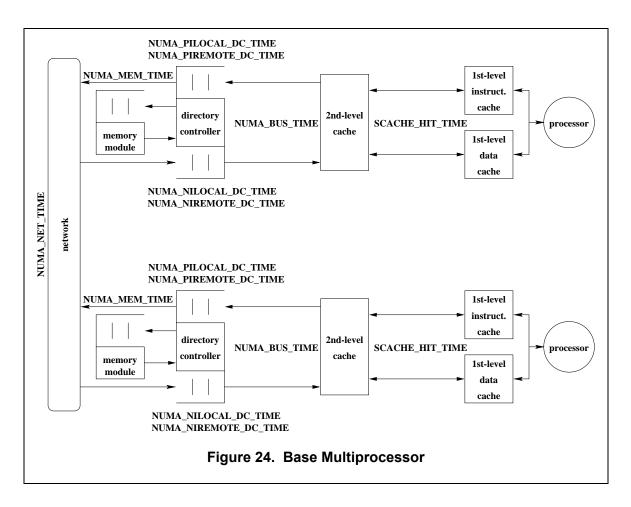

| Figure 25. | Benchmark #1                                                                         | 65  |

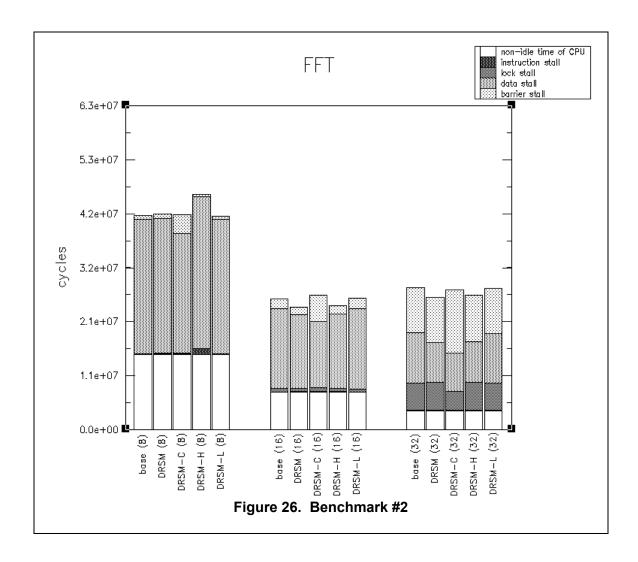

| Figure 26. | Benchmark #2                                                                         | 66  |

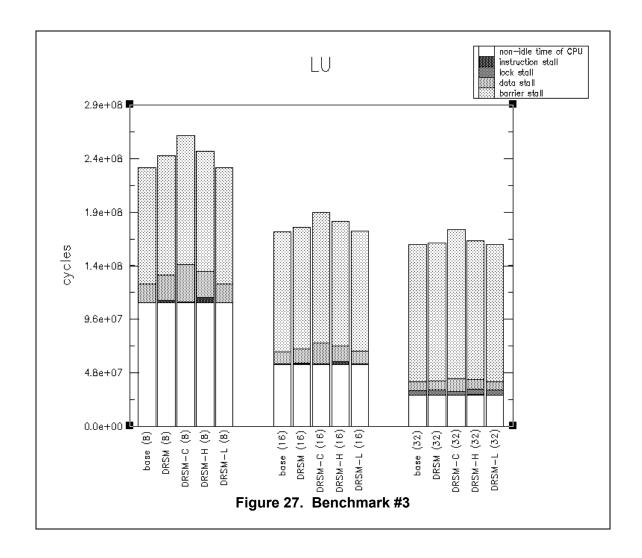

| Figure 27. | Benchmark #3                                                                         | 67  |

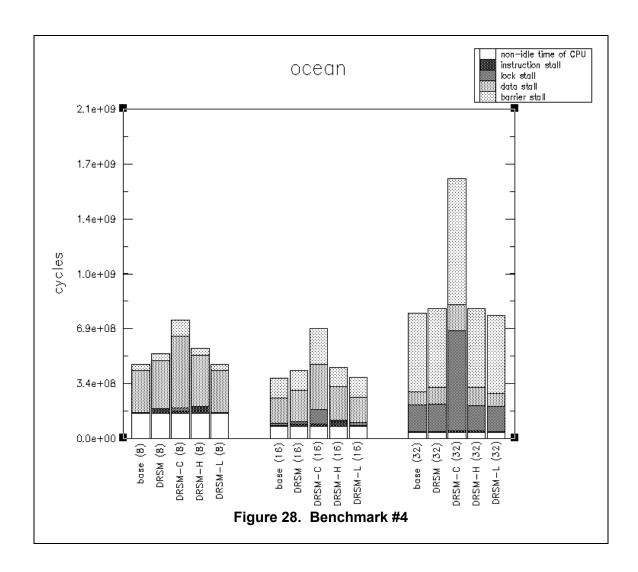

| Figure 28. | Benchmark #4                                                                         | 68  |

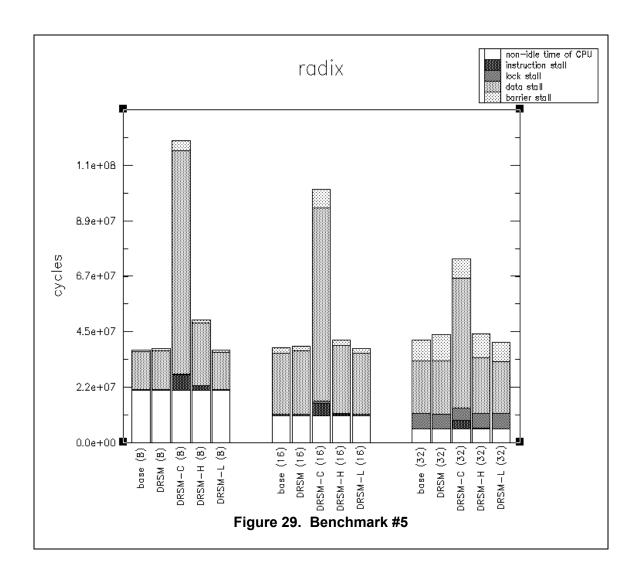

| Figure 29. | Benchmark #5                                                                         | 69  |

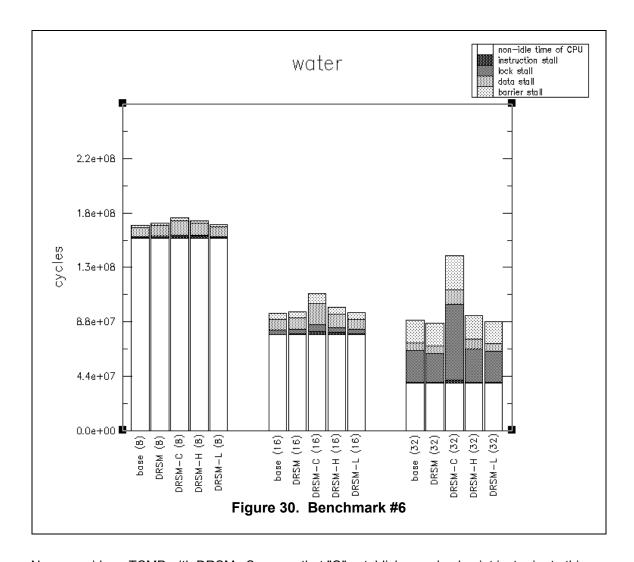

| Figure 30. | Benchmark #6                                                                | 70  |

|------------|-----------------------------------------------------------------------------|-----|

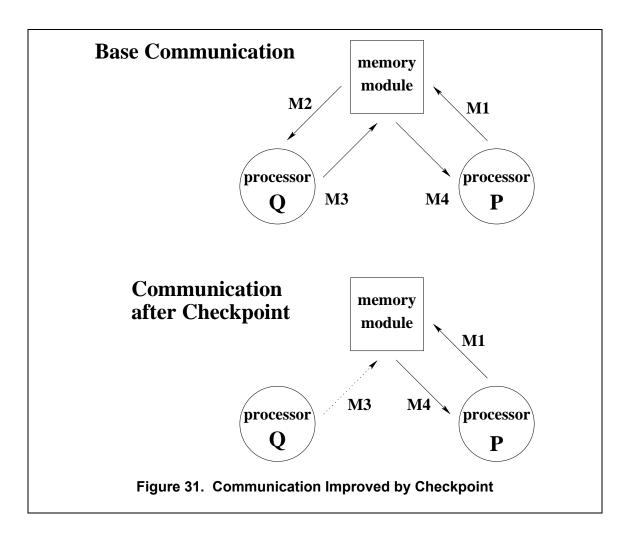

| Figure 31. | Communication Improved by Checkpoint                                        | 71  |

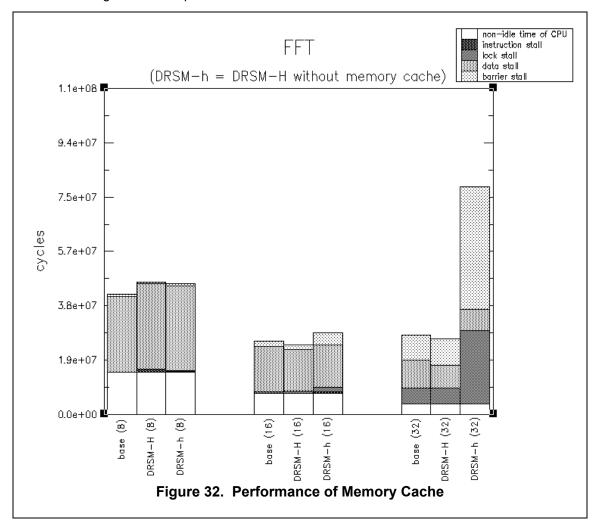

| Figure 32. | Performance of Memory Cache                                                 | 86  |

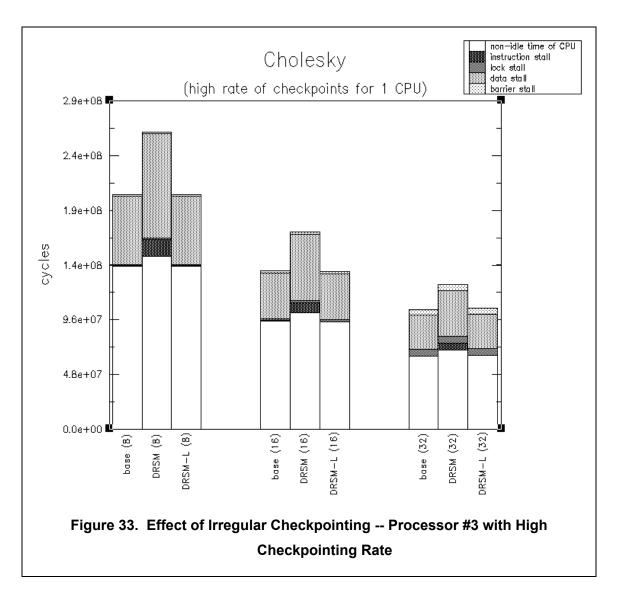

| Figure 33. | Effect of Irregular Checkpointing Processor #3 with High Checkpointing Rate | 88  |

| Figure 34. | Delay for Establishing Checkpoints per Processor                            | 90  |

| Figure 35. | Number of Negative Acknowledgments (NAKs) per Processor                     | 91  |

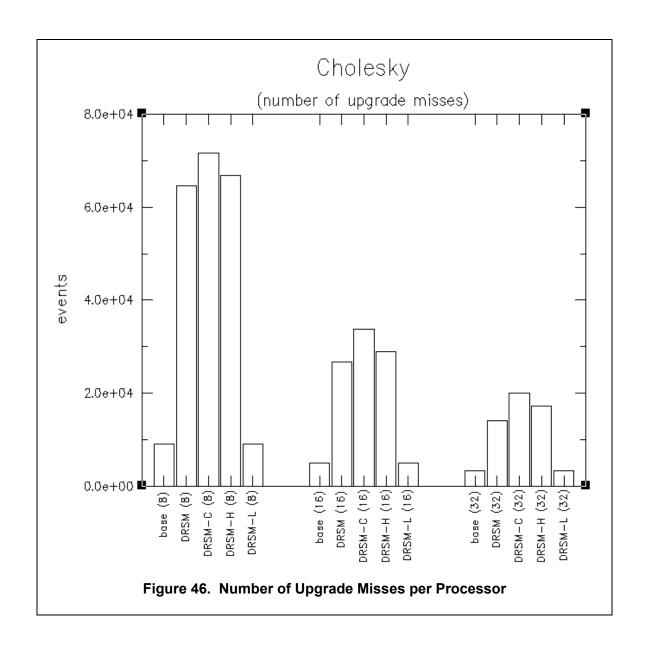

| Figure 36. | Number of Upgrade Misses per Processor                                      | 92  |

| Figure 37. | Benchmark #1                                                                | 112 |

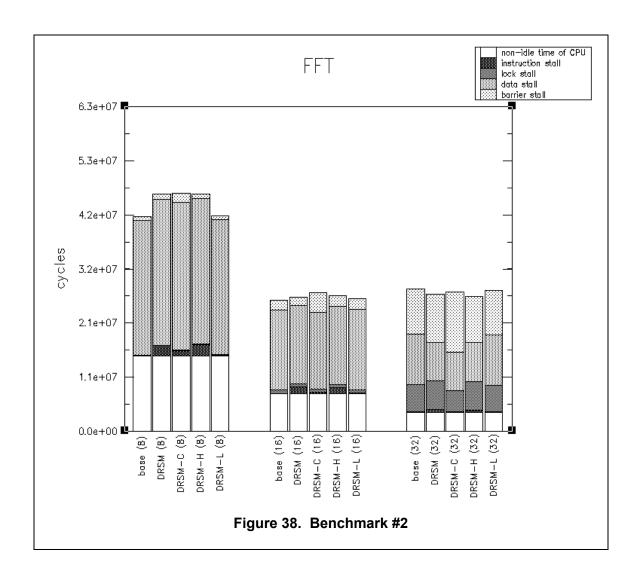

| Figure 38. | Benchmark #2                                                                | 113 |

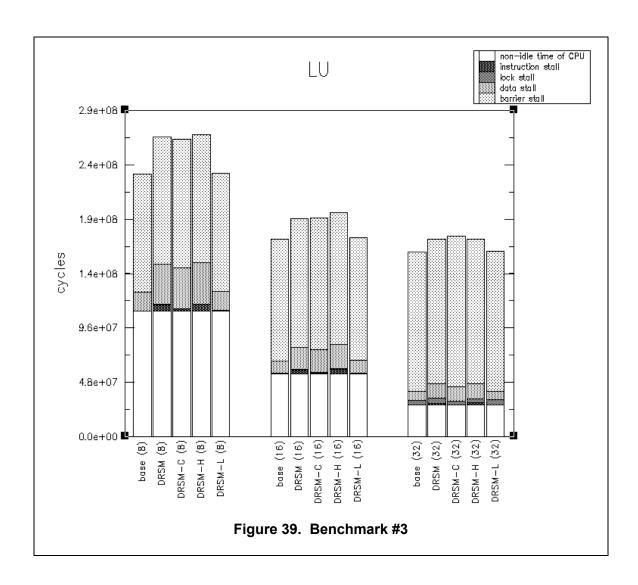

| Figure 39. | Benchmark #3                                                                | 114 |

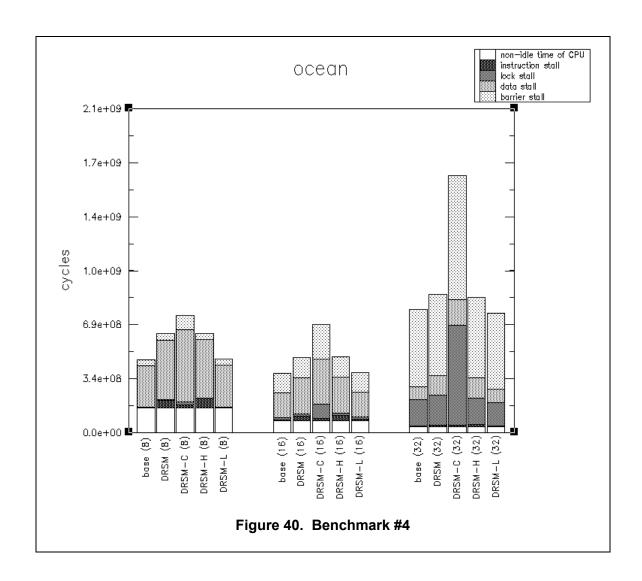

| Figure 40. | Benchmark #4                                                                | 115 |

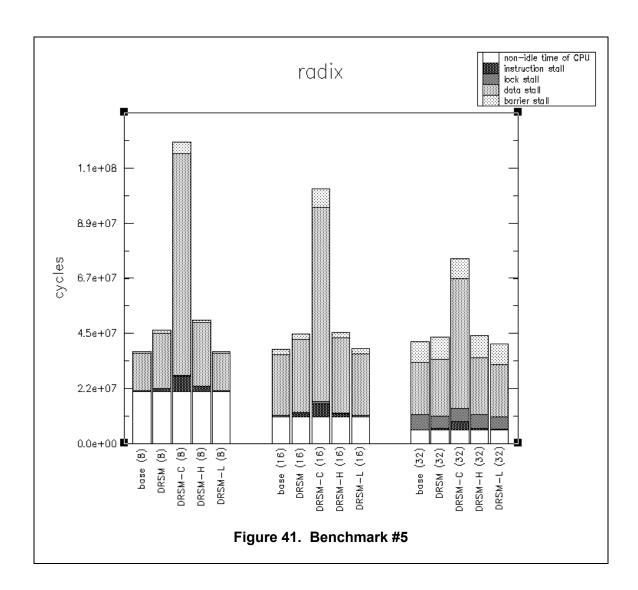

| Figure 41. | Benchmark #5                                                                | 116 |

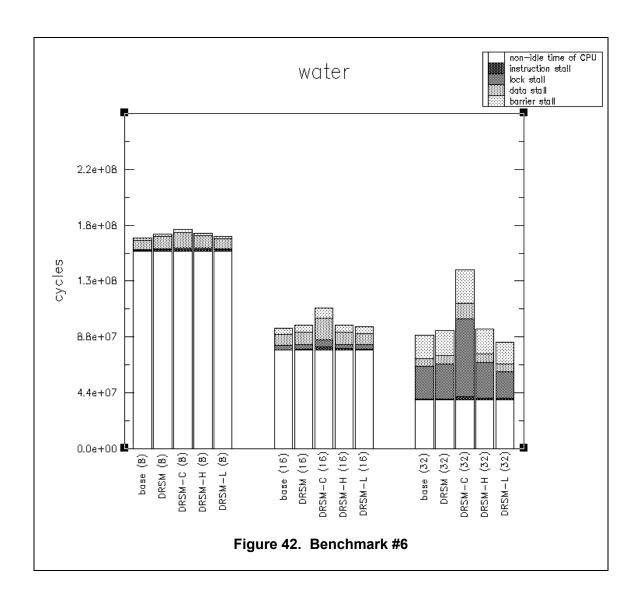

| Figure 42. | Benchmark #6                                                                | 117 |

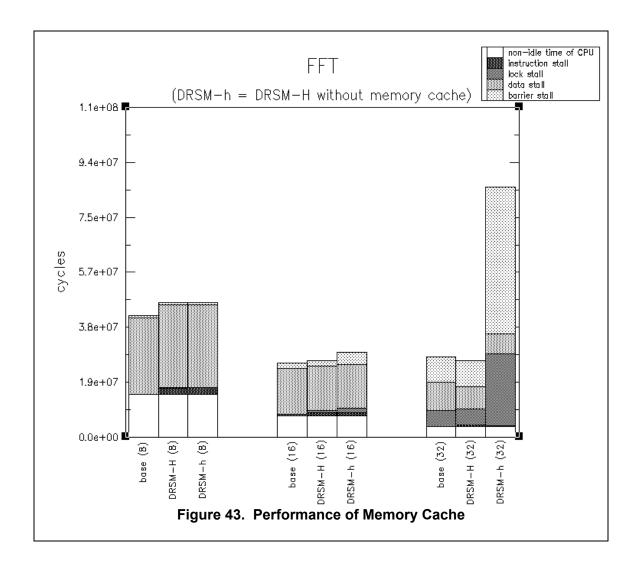

| Figure 43. | Performance of Memory Cache                                                 | 127 |

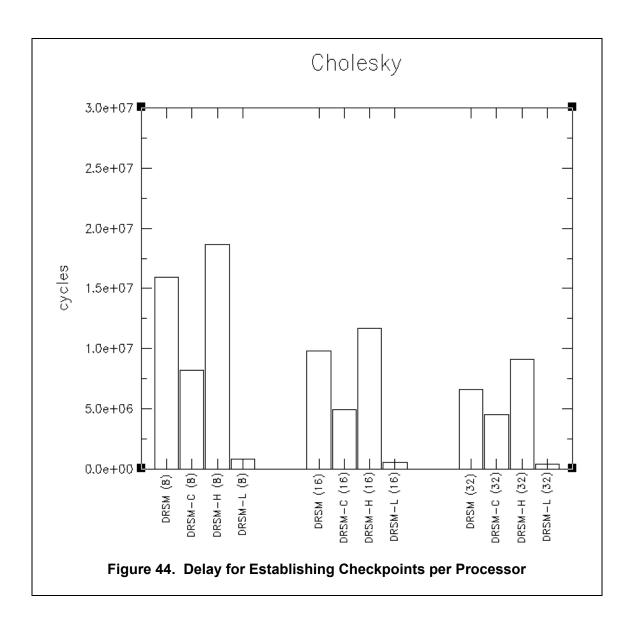

| Figure 44. | Delay for Establishing Checkpoints per Processor                            | 129 |

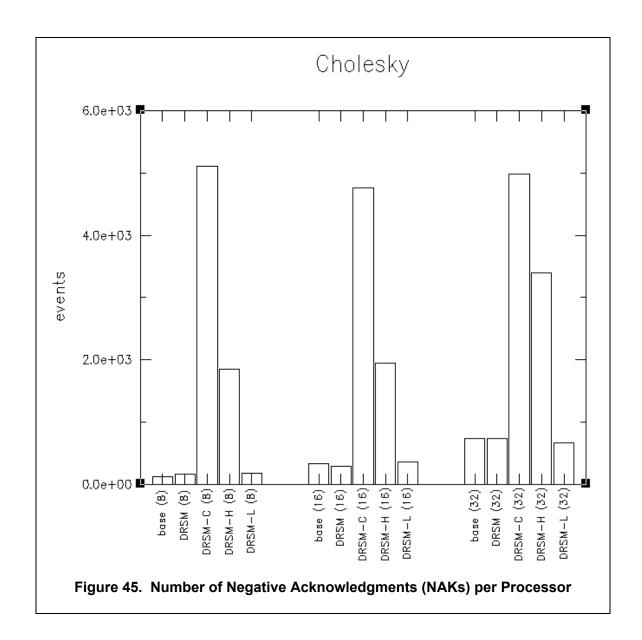

| Figure 45. | Number of Negative Acknowledgments (NAKs) per Processor                     | 130 |

| Figure 46. | Number of Upgrade Misses per Processor                                      | 131 |

## **Chapter 1. Introduction**

## 1.1. Tightly-Coupled Multiprocessor (TCMP)

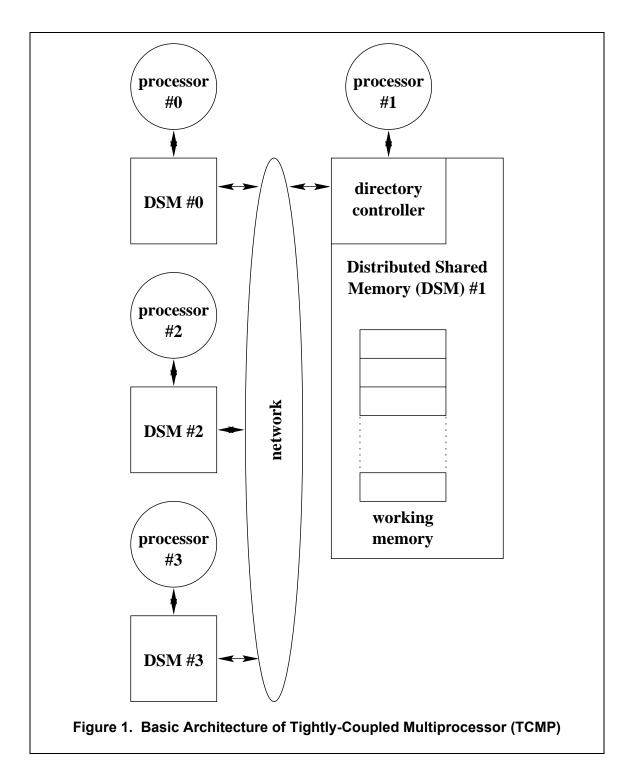

The tightly-coupled multiprocessor (TCMP), where specialized hardware maintains the image of a single shared memory, has the highest performance among the various types of computer systems. The architecture of a TCMP can vary greatly. In this dissertation, we focus on a TCMP with an architecture like that shown in figure 1.

In figure 1, the TCMP has 4 nodes connected by a high-speed internal network. Each node of the TCMP consists of the processor module and its associated memory module, and both these modules are usually combined into a single processor board. Each processor module has a processor, a 1st-level cache, and a 2nd-level cache. In figure 1, the processor modules are the objects labeled "processor #0", "processor #1", "processor #2", and "processor #3". The caches do not appear explicitly in figure 1.

Each memory module has both a directory controller and 1 bank of memory. In figure 1, the memory modules are the objects labeled "DSM #0", "DSM #1", "DSM #2", and "DSM #3". The bank of memory is labeled "working memory". The memory is organized into consecutive blocks of many bytes. The size of a memory block is identical to the size of a 2nd-level-cache line. (The directory controller is a component that intercepts and processes cache-coherence messages destined for either the local processor or the local memory. For each block of memory, the directory controller records all the processors holding the block in their caches.)

Some examples of a TCMP are the AViiON AV 25000 by Data General, the NUMA-Q 2000 by Sequent, and the S/390 by International Business Machines (IBM). The most well-known TCMP is probably the IBM S/390 [9]. It differs somewhat from the block diagram in figure 1. The processor modules of the IBM S/390 are connected directly into the internal network. Also, the IBM S/390 has exactly one memory module, which is connected directly into the internal network.

## 1.2. Fault-tolerant TCMP

In order to facilitate the use of such TCMPs in the commercial environment, we must build fault tolerance into them. One approach is triple modular redundancy. Three TCMPs receive identical

copies of inputs from the environment outside of the TCMP and perform identical computations. A voter, a separate device, compares the outputs of the 3 TCMPs. If no fault occurs, all 3 outputs are identical, and the voter delivers the common output to the environment. If one TCMP fails due to a transient fault, then 1 of the 3 outputs will differ from the other 2 outputs, and the voter delivers one of the 2 common outputs to the environment. The TCMP that failed then resets itself and loads its state from that in the other 2 TCMPs. In this way, triple module redundancy tolerates the failure of 1 entire TCMP. Triple module redundancy performs well since it does not hinder the execution of the TCMP; the time for recovering from a fault is effectively 0 second. On the other hand, triple module redundancy is extremely expensive since it requires multiple TCMPs.

Instead of using modular redundancy, which requires excessive replication of hardware, we can use roll-back recovery, which minimizes replication of hardware but increases the recovery time. The newest IBM S/390 uses this approach [11]. The error-correcting-code circuits protect the main memory and 2nd-level cache from any transient fault. The error-checking-code circuits detect any transient fault in the 1st-level cache. The G5 microprocessor in the IBM S/390 consists of 2 identical processors tied together by a comparator, which verifies that their outputs are identical. The R-unit, a separate fault-tolerant buffer within the G5 microprocessor, stores a duplicate copy of the current state of the G5 and is essentially its checkpoint; the G5 updates the R-unit per cycle. If a transient fault arises either in 1 of the 2 identical processors (according to the comparator) or in the 1st-level cache (according to the error-checking-code circuit), the G5 resets the 2 identical processors, loads their state from the R-unit, and invalidates the contents of the 1st-level cache. The G5 then resumes normal execution. Roll-back recovery does not require multiple TCMPs but does hinder the execution of the TCMP if a fault occurs (since the IBM S/390 must waste time in halting the 2 identical processors of the G5 microprocessor and in loading their state from the R-unit, for example). Hence, roll-back recovery is cheaper than but slower than triple modular redundancy.

### 1.3. Research on Roll-back Recovery

Because roll-back recovery is relatively inexpensive, it has become the dominant method of fault tolerance. In general, roll-back recovery has 2 principal aspects. First, a processor establishes occasional checkpoints; a checkpoint is a consistent state of the system. Second, if the processor encounters a fault, the processor rolls back to the last checkpoint and commences execution from the state saved in that checkpoint. The first aspect, the establishment of checkpoints, is the more important one as it is a cost that the TCMP regularly experiences even if no fault arises. The second aspect, the actual rolling-back, is less important as faults occur

infrequently. Hence, much of the research in roll-back recovery for TCMPs has focused on developing efficient algorithms for establishing checkpoints.

Our research also focuses on efficient methods of establishing checkpoints for roll-back recovery. We assume that re-designing a processor specifically to be fault-tolerant is prohibitively expensive. In other words, we assume that only commodity processors are available. By contrast, the engineers of the G5 microprocessor completely re-designed the architecture so that the time for establishing checkpoints (i. e. updating the state in the R-unit) is hidden in the pipeline and is effectively 0 second.

In this dissertation, we present 4 apparatus and algorithms for establishing checkpoints and rolling back from a fault but focus on the performance of establishing checkpoints. We contribute the following to the field of fault tolerance.

- 1. We extend recoverable shared memory (RSM) [2] to create distributed recoverable shared memory (DRSM). RSM operates in a TCMP with multiple processor modules but with only a single memory module; this memory module contains the entire global physical memory. By contrast, DRSM operates in a TCMP where each processor has its own local memory module; each local memory module contains a portion of the global physical memory. (Also, each memory module of a TCMP with the DRSM has 2 banks of memory. One bank is the working memory, and another bank is the permanent-checkpoint memory.)

- 2. We extend DRSM by eliminating 1 of its 2 banks of memory to create DRSM with half of the memory (DRSM-H).

- 3. We implement a communication-based checkpointing apparatus and algorithm, DRSM for communication checkpoints (DRSM-C), by eliminating the dependency matrix of DRSM.

- 4. We implement the first audit-trail-based apparatus and algorithm, DRSM with logs (DRSM-L), on a TCMP.

- 5. We use a uniform set of assumptions to evaluate DRSM, DRSM-C, DRSM-H, and DRSM-L in order to provide a fair comparison.

- 6. We present the first performance-based analysis of checkpointing apparatus and algorithms on a TCMP with a general interconnection network assisted by directories. The only other performance-based analysis [7] of checkpointing focuses on a bus-based TCMP.

## Chapter 2. Background

## 2.1. Dependencies

The basic idea of roll-back recovery is the following. In a uni-processor computer, the processor periodically establishes a checkpoint. If the computer encounters a fault, the processor rolls the system back to the state in the last checkpoint. A checkpoint is a snapshot of the data stored in the system and can represent any set of values that are generated by the fault-free execution of the system. In other words, the checkpoint is a consistent state of the system

The simple scheme for roll-back recovery becomes complicated in a TCMP. Processors access shared memory blocks, and this interaction causes dependencies to arise. There are 4 possible types of interactions on the same shared memory block.

```

1.

read - read:

A read by processor P precedes a read (of the same

memory block) by processor Q.

dependency: none

read - write: A read by processor P precedes a write (of the

same memory block) by processor Q.

dependency: none

write — read:

A write by processor P precedes a read (of the

same memory block) by processor Q.

roll-back dependency: P -> Q

checkpoint dependency: Q -> P

write - write: A write by processor P precedes a write (of the

same memory block) by processor Q.

roll-back dependency: P <-> Q

checkpoint dependency: P <-> Q

```

Only the last 2 interactions cause dependencies to arise. We shall examine how they arise. In our presentation, we assume that a memory block and the highest-level-cache line are identical in

size and that the TCMP uses a write-back cache policy. To minimize the cost of the system, we assume that it can hold only 1 level of checkpoint.

We use the notation of "->" or "<->" to indicate, respectively, that 1 processor is dependent on another processor or that 2 processors are dependent on each other. For example, consider the roll-back dependency of "P -> Q". This symbolic notation indicates that if processor "P" rolls back to its last checkpoint, then processor "Q" must also roll back to its last checkpoint.

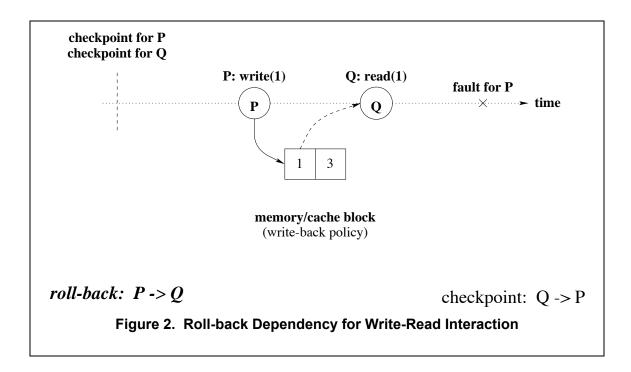

Figure 2 illustrates the roll-back dependency that arises for the write-read interaction. After processor "P" writes the value of 1 into a word of the memory block, processor "Q" reads that value of 1. Then, processor "P" experiences a fault and rolls back to the last checkpoint. "Q" must also roll back to the last checkpoint because "Q" read a value, 1 in this case, that "P" produced. When "P" resumes execution from the last checkpoint, "P" may not necessarily reproduce the value of 1. ("P" may not necessarily reproduce the value of 1 since "P" may not necessarily read the same values that "P" read prior to the fault. Some other processor, say "R", may have already modified those values.) Thus, we have the roll-back dependency of "P -> Q".

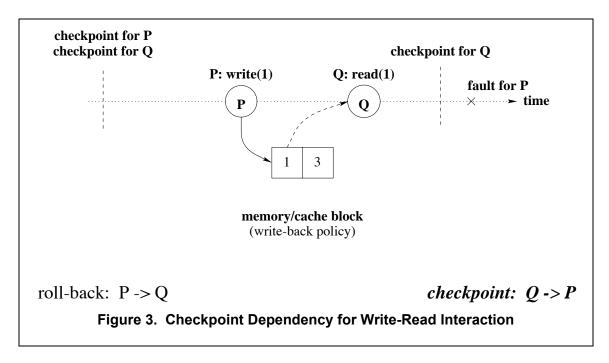

Figure 3 illustrates the checkpoint dependency that arises for the write-read interaction. After processor "P" writes the value of 1 into a word of the memory block, processor "Q" reads that value of 1. Then, processor "Q" establishes a checkpoint. In figure 3, "Q" establishes 2 checkpoints: the 1st checkpoint occurring before "Q" reads the value of 1 and the 2nd checkpoint

occurring after "Q" reads the value of 1. Subsequently, processor "P" experiences a fault and rolls back to the last checkpoint. The roll-back dependency dictates that "Q" must roll back to the 1st checkpoint, but by the time that "P" experiences a fault, "Q" has already established the 2nd checkpoint and can only roll back to it. The state saved in the 2nd checkpoint depends on the value of 1 produced by "P". Since "P" may not necessarily reproduce the value of 1 after resuming execution from the last checkpoint, the state saved in the 2nd checkpoint can be invalid. Therefore, if "Q" establishes a checkpoint after the write-read interaction, then "P" must also establish a checkpoint. In this way, we ensure that "P" does not "un-do" the value of 1 that was read by "Q". Thus, we have the checkpoint dependency of "Q -> P".

The write-write interaction has 2 cases: one where the processors write into different words of the same memory block and one where the processors write into the same word of the same memory block. Each case results in a different direction of the dependency (i. e. a different direction of the dependency arrow in the above list). The combined effect of both cases is a 2-way dependency for both the roll-back dependency ("P < P > Q") and the checkpoint dependency ("P < P > Q").

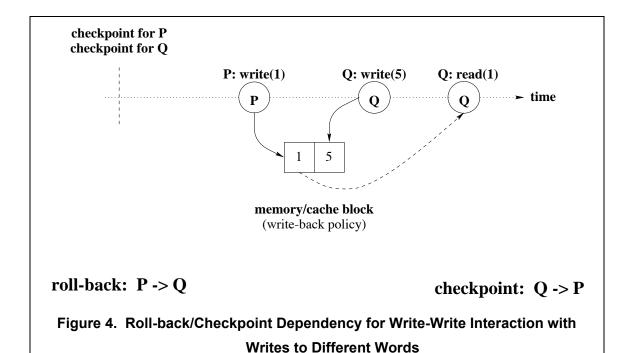

Figure 4 illustrates the roll-back dependency and the checkpoint dependency for the write-write interaction where the processors write into different words of the same memory block. Since the cache policy is write-back, after "Q" writes the value of 5 into the block, "Q" holds it in the cache. "Q" can potentially read the value of 1 written by "P". Hence, a write-read interaction arises. We have already analyzed this interaction in figures 2 and 3. Thus, we have a roll-back dependency of " $P \rightarrow Q$ " and a checkpoint dependency of " $P \rightarrow Q$ ".

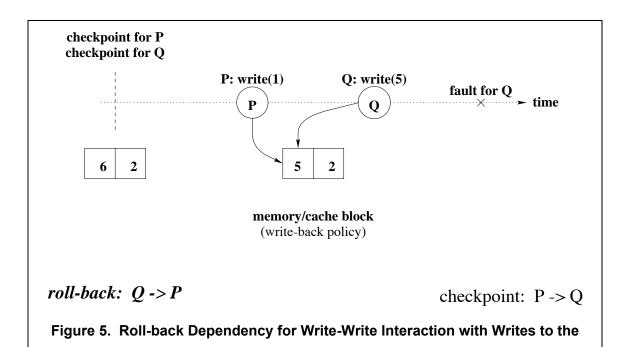

Figure 5 illustrates the roll-back dependency for the write-write interaction where the processors write into the same word of the same memory block. Processor "P" writes the value of 1 into the

Same Word

memory block, overwriting the original value of "6". Then, processor "Q" writes the value of 5 into the same word, overwriting the value of 1. Subsequently, "Q" experiences a fault and rolls back to the last checkpoint. "Q" un-does the value of 5 and must replace it with the value of 1, but there is no convenient way to retrieve the value of 1 since it was destroyed by "Q" writing the value of 5. The only value that the TCMP can use to replace 5 is the original value of 6. In order to ensure that the state of the TCMP is valid, "P" must roll-back to the last checkpoint as well in order to un-do the value of 1. Hence, we have a roll-back dependency of "Q -> P".

Figure 6. Checkpoint Dependency for Write-Write Interaction with Writes to the Same Word

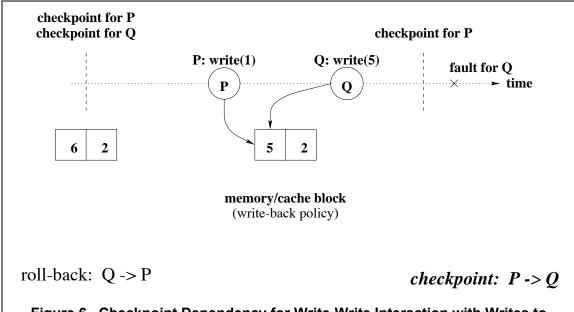

Figure 6 illustrates the checkpoint dependency for the write-write interaction where the processors write into the same word of the same memory block. Processor "P" writes the value of 1 into the memory block, overwriting the original value of 6. Then, processor "Q" writes the value of 5 into the same word, overwriting the value of 1. Next, "P" establishes a checkpoint. In figure 6, "P" establishes 2 checkpoints: the 1st checkpoint occurring before "P" writes the value of 1 and the 2nd checkpoint occurring after "P" writes the value of 1. Subsequently, "Q" experiences a fault and rolls back to the last checkpoint. The roll-back dependency dictates that "P" must roll back to the 1st checkpoint, but by the time that "Q" experiences a fault, "P" has already established the 2nd checkpoint and can only roll back to it. The state of the TCMP can become invalid since (1) it assumes that the value of 1 is stored in the pertinent word of the memory block but (2) "Q" can un-do the value of 5 by only replacing it with 6. There is no convenient way to retrieve the value of 1 and to use 1 to replace 5. Hence, to solve this problem, if "P" establishes the 2nd checkpoint, "Q" must also establish a checkpoint. Then, "Q" will not roll

back past the 2nd checkpoint and will not need to un-do the value of 5. Thus, we have a checkpoint dependency of " $P \rightarrow Q$ ".

Therefore, the write-write interaction causes bi-directional dependencies to arise. The roll-back dependency is "P <-> Q". The checkpoint dependency is "P <-> Q" as well.

### 2.2. Classes of Algorithms

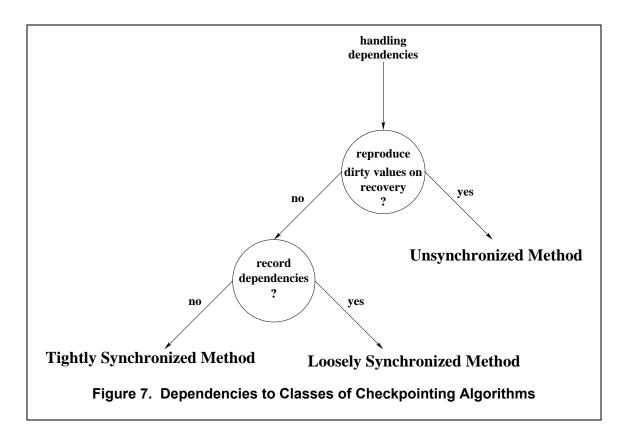

Checkpointing algorithms must deal with these dependencies. How the algorithms deal with them results in a natural partition of the types of algorithms that exist. We shall present this natural partition. In presenting this natural partition, we implicitly assume that our processor is a commodity processor, which does not have any special hardware for establishing a checkpoint; hence, we specifically exclude the G5 microprocessor (produced by IBM) from our consideration.

Anyhow, figure 7 illustrates the approaches for dealing with the dependencies. Dependencies arise because a dirty value written by a processor "P" (and possibly read by another processor "Q") is not necessarily reproduced if "P" rolls back to its last checkpoint and resumes execution from it. (A dirty value is merely data modified by a processor.) If an algorithm can ensure that dirty values written by a processor "P" after roll-back are identical to those dirty values written by

"P" before encountering the fault (that resulted in the roll-back), then the algorithm is a member of the class called the unsynchronized method. In an algorithm in the class of the unsynchronized method, a processor can establish a checkpoint (or perform a roll-back) that is completely independent of any other processor.

If an algorithm cannot guarantee that dirty values produced by "P" after roll-back are identical to those dirty values produced by "P" before encountering the fault, then the algorithm can simply record the dependencies. Such an algorithm is a member of the class called the loosely synchronized method. In an algorithm in the class of the loosely synchronized method, if any checkpoint dependency (or roll-back dependency) arises, the TCMP simply records the dependency. At some point in the future, if a processor establishes a checkpoint (or performs a roll-back), then that processor queries the records of dependencies to determine all other processors that must establish a checkpoint (or perform a roll-back) as well.

Finally, if the checkpointing algorithm cannot guarantee reproduction of dirty values after roll-back and if the algorithm does not record dependencies, then the algorithm must do following. A processor "P" must establish a checkpoint whenever "P" delivers dirty data to another processor or to the memory system (via the eviction of a dirty cache line). Such an algorithm is a member of the class called the tightly synchronized method.

For a TCMP, researchers have developed algorithms in the class of the tightly synchronized method and in the class of the loosely synchronized method. An example of an algorithm in the class of the tightly synchronized method is the algorithm proposed by Wu [17]. An example of an algorithm in the class of the loosely synchronized method is the algorithm proposed by Banatre [2].

As for our algorithms in this dissertation, DRSM-C is an algorithm in the class of the tightly synchronized method. Both DRSM and DRSM-H are algorithms in the class of the loosely synchronized method. DRSM-L is an algorithm in the class of the unsynchronized method and is the first algorithm in the class of the unsynchronized method for a TCMP. Before DRSM-L, no such algorithm for a TCMP existed although Richard [10] and Suri [15] have proposed algorithms in the class of the unsynchronized method for a loosely-coupled multiprocessor like a network of workstations. The DRSM-L described here is an improved version of DRSM-L originally contrived by Sunada [13].

## Chapter 3. Assumptions

## 3.1. Fault-tolerant Components

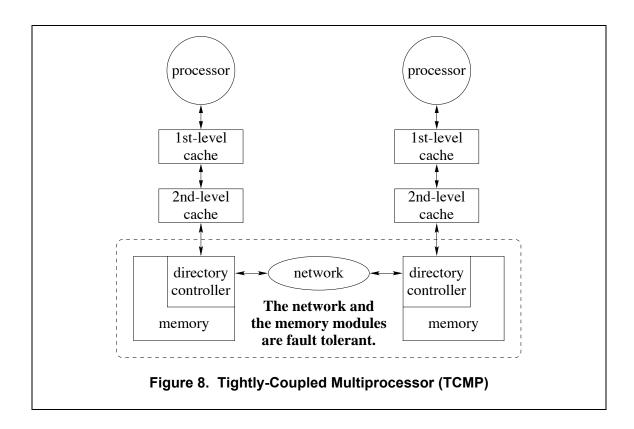

The TCMP into which we shall incorporate our checkpointing apparatus and algorithms is a multinode multiprocessor like that shown in Figure 8. Each node has a processor module and a memory module. The nodes are connected by a high-speed internal network. We make the following specific assumptions about our TCMP.

- 1. Each component in our TCMP is fail safe. If the component fails, it simply stops and does not emit spurious data.

- 2. The TCMP suffers at most a single point of failure. The TCMP has exactly 1 spare processor module (including the processor and associated caches).

- 3. Each memory module is fault tolerant.

- 4. The network connecting the nodes in our TCMP is fault tolerant. Specifically, between any 2 nodes are 2 independent paths, and each memory module is dual-ported.

- 5. The virtual-machine monitor is fault-tolerance aware. Specifically, if communication occurs between a processor and the environment outside of the TCMP, then the virtual-machine monitor will invoke the processor to establish a checkpoint.

The first 4 assumptions are commonly found in research papers proposing checkpointing algorithms for a TCMP. The last assumption can be re-phrased by replacing "virtual-machine monitor" with "operating system" for those systems without a virtual-machine monitor. (A virtual-machine monitor is a layer of software running on top of the raw computer and presents a separate virtual image of the underlying hardware, including the processor and external network, to each operating system [3].) We believe that building fault tolerance into the virtual-machine monitor is superior to building fault tolerance into the operating system since a fault-tolerant virtual-machine monitor enables us to run any non-fault-tolerant operating system while the entire TCMP remains fault-tolerant. The TCMP views the operating system as simply another user application running on top of the virtual-machine monitor [3].

Also, our assumption that the TCMP suffers at most a single point of failure is overly restrictive for both DRSM-C and DRSM-L. The recovery algorithms that we describe for DRSM-C and DRSM-L actually allow them to recover from multiple transient faults (but only a single permanent fault since we assume only 1 spare processor module).

The essence of our assumptions is that the memory module and the network are fault tolerant but that the processor module (including the processor and associated caches) is not fault tolerant. The apparatus and algorithms that we describe enable the TCMP to recover from a failure of the processor module.

## 3.2. Distinction between Processor and Directory Controller

When we describe the procedure by which DRSM, DRSM-C, or DRSM-H establishes a checkpoint, we describe the procedure by specifying many actions that a processor performs in order to establish a checkpoint, but the processor does not actually perform most of those actions that we specify. Rather, the directory controller actually performs most of those actions. Once a processor attempts to establish a checkpoint, the local directory controller takes control of establishing the checkpoint and coordinates the associated activities on behalf of the processor. Nevertheless, we use the processor-centered approach, assigning actions (that are really done

by the directory controller) to the processor, to describe the checkpointing procedure because this approach simplifies the description.

## Chapter 4. Distributed Recoverable Shared Memory (DRSM)

#### 4.1. Introduction

The distributed recoverable shared memory (DRSM) is our 1st apparatus and algorithm for establishing checkpoints and is a type of loosely synchronized method. We construct DRSM by extending recoverable shared memory (RSM) to multiple memory modules. The DRSM (and RSM) basically records dependencies that arise among processors as they access the same memory locations. Recording the dependencies generally enables the DRSM to delay the establishment of checkpoints until an arbitrarily chosen time. In our case, we use a timer to announce when a processor should establish a checkpoint; the timer can set the maximum temporal interval between checkpoints, effectively setting the maximum time for roll-back recovery. Any interaction between an application process and the environment of the TCMP poses a special problem and requires that the processor of the application process must immediately establish a checkpoint.

#### 4.2. Prior Work

DRSM improves upon RSM, developed by Banatre [2]. Unlike a modern TCMP with multiple memory modules, a TCMP using RSM has a single memory module, and this configuration degrades the performance of the TCMP by, for example, increasing the likelihood of hot spots. To minimize the impact of such problems, we extend RSM to multiple memory modules to create DRSM.

In addition, DRSM differs from the scheme proposed by Janakiraman [6] in 2 important aspects. First, he assigns a checkpoint dependency of "Q <-> P" to the write-read interaction (in which a read by "Q" follows a write by "P"); this dependency is unnecessarily stronger than the actual checkpoint dependency of "Q -> P" that arises. Second, although Janakiraman claims that his approach works for a TCMP, he ignores the fact that caches experience conflict misses.

## 4.3. Background: Recoverable Shared Memory (RSM)

Before we describe DRSM, we first describe RSM. Figure 9 illustrates the configuration of a RSM module. We slightly modify the explanation by Banatre to present details that may not have appeared in the original description.

## 4.3.1. Dependency Matrix

The key element is the dependency matrix, which is an array of bits. This matrix, "DM[][]", sees all accesses that reach the RSM module and sets the bits according to the checkpoint dependencies listed in section 2.1.

## 4.3.2. Last-Writer Indicator

The RSM module contains an additional buffer for each block of memory. This buffer stores the last writer to the block.

### 4.3.3. Checkpoint Counters

The collection of global checkpoint counters contains 1 counter for each processor in the system. Each block in memory has an associated block checkpoint counter. When processor "P[2]", for example, writes into a block, the value of the global checkpoint counter for "P[2]" is copied into the block checkpoint counter. RSM updates the buffer for the last writer to "2". The purpose of the checkpoint counters is to accelerate the establishment of permanent checkpoints. They are explained in a later section.

## 4.3.4. Memory for Tentative Checkpoint

The working memory operates like the memory in a non-fault-tolerant system but also functions as the tentative-checkpoint memory. When the RSM begins a 2-phase checkpoint of dependent processors, they write their dirty cache data into the tentative-checkpoint memory in the 1st phase. The dirty blocks of memory form the tentative checkpoint, which is later converted into the permanent checkpoint in the 2nd phase.

## 4.3.5. Memory for Permanent Checkpoint

The RSM ultimately copies data saved during the tentative-checkpoint phase into the permanent-checkpoint memory. It always contains data comprising a consistent state of the system. The TCMP rolls back to this data after a failure occurs.

### 4.3.6. Establishing Checkpoints

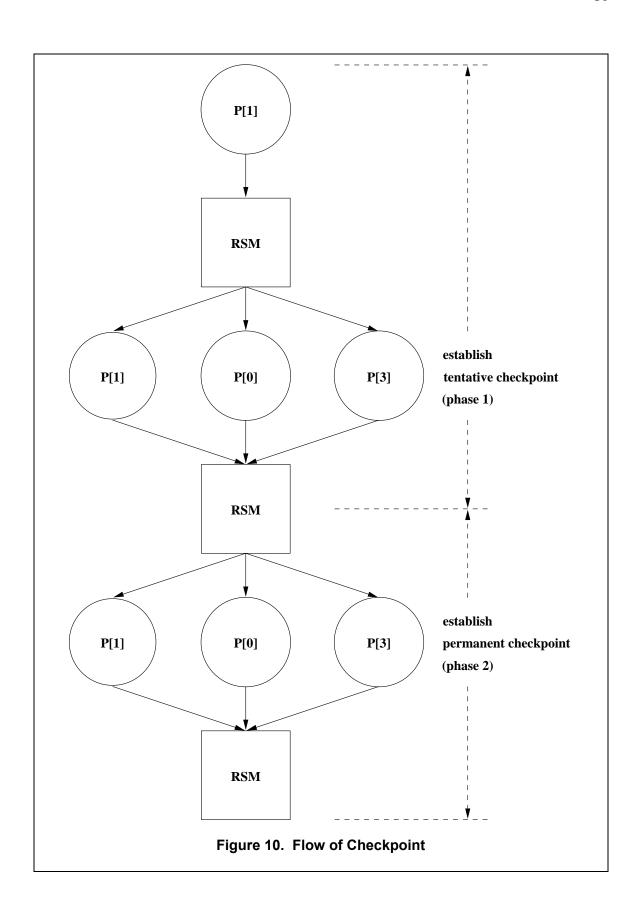

Figure 10 illustrates the establishment of a checkpoint for a 4-processor TCMP. A processor "P[1]" that wishes to establish a checkpoint submits a request to the RSM. The RSM then scans the dependency matrix for all other processors that must establish a checkpoint along with "P[1]". The RSM finds that both "P[0]" and "P[3]" must establish a checkpoint along with "P[1]" and hence submits a request to them to establish a checkpoint. They write their dirty cache data back into memory and send a copy of their internal states (i. e. data in the internal registers) to the RSM. This phase is the tentative-checkpoint phase. After it completes successfully, the RSM converts the tentative checkpoint into a permanent checkpoint.

After verifying that the establishment of the tentative checkpoint is successful, the RSM increments the global checkpoint counters for "P[0]", "P[1]", and "P[3]" and then requests those processors to resume execution of their normal processes. They send acknowledgments to the RSM, and it resumes its normal functions. The RSM does not immediately copy the blocks saved during the tentative-checkpoint phase into the permanent-checkpoint memory during the permanent-checkpoint phase. Rather, the RSM merely increments the global checkpoint counters for the processors involved in the checkpoint. After the RSM concludes the permanent checkpoint, if a write access occurs on a block (in the tentative-checkpoint memory) where the global checkpoint counter of the last writer is greater than the block counter, then the RSM knows that the current data in the block is part of a permanent checkpoint. Hence, the RSM first copies the data from the block in the tentative-checkpoint memory into the corresponding block in the permanent-checkpoint memory before the RSM writes the incoming new data into the block in the tentative-checkpoint memory. This copy-on-write technique accelerates the establishment of the permanent checkpoint by avoiding the copying of potentially millions of blocks of data from the tentative-checkpoint memory into the permanent-checkpoint memory during the permanentcheckpoint phase.

## 4.3.7. New Requests after Initiating Checkpoint

If processor "P[2]" submits a request to the RSM to establish a checkpoint and if the request arrives at the RSM before the start of the permanent-checkpoint phase for "P[0]", "P[1]", and "P[3]", then the RSM will combine "P[2]" into the group of processors that must establish a checkpoint together. In other words, the RSM grants the request from "P[2]" to establish a checkpoint and waits until "P[2]" has finished its tentative-checkpoint phase before the RSM begins the permanent-checkpoint phase of all processors in the group: "P[0]", "P[1]", "P[2]", and "P[3]". If the request arrives after the start of the permanent-checkpoint phase, then the RSM negatively acknowledges the request, and "P[2]" must re-submit its request.

### 4.4. Apparatus of DRSM

We extend RSM to multiple memory modules to create distributed recoverable shared memory (DRSM). The single memory module of RSM degrades the performance of the TCMP by, for example, increasing the likelihood of hot spots. Modern TCMPs distribute the shared memory among all the nodes in the system.

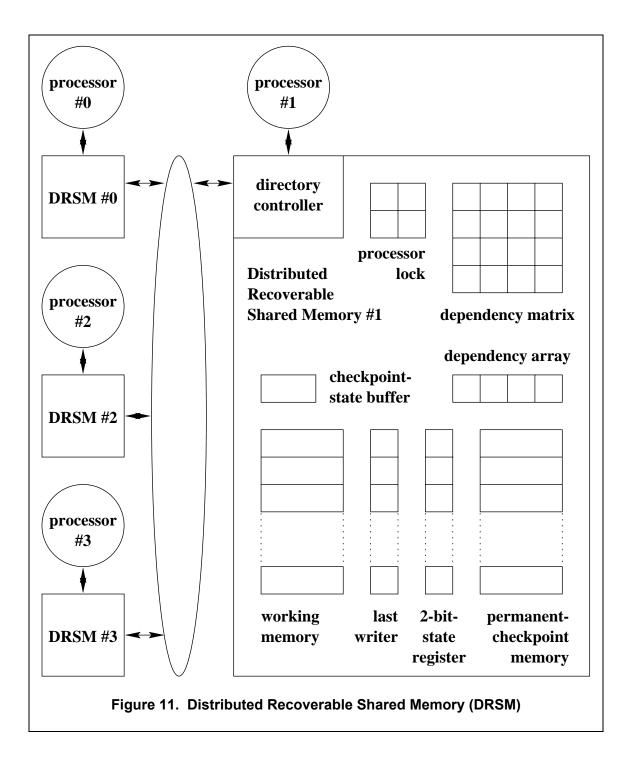

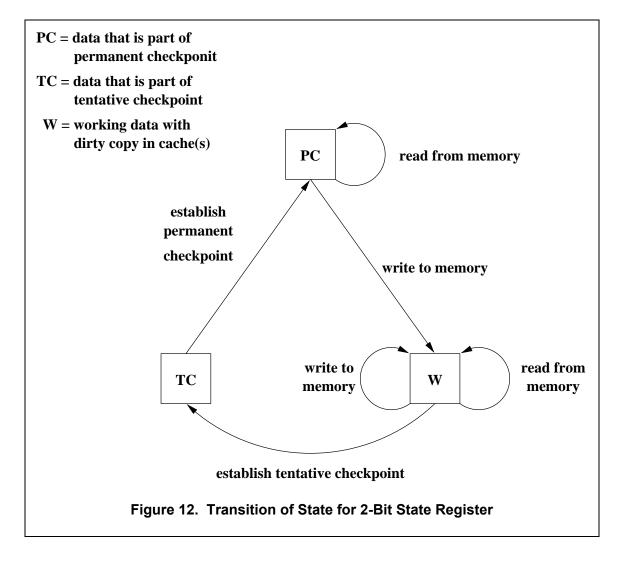

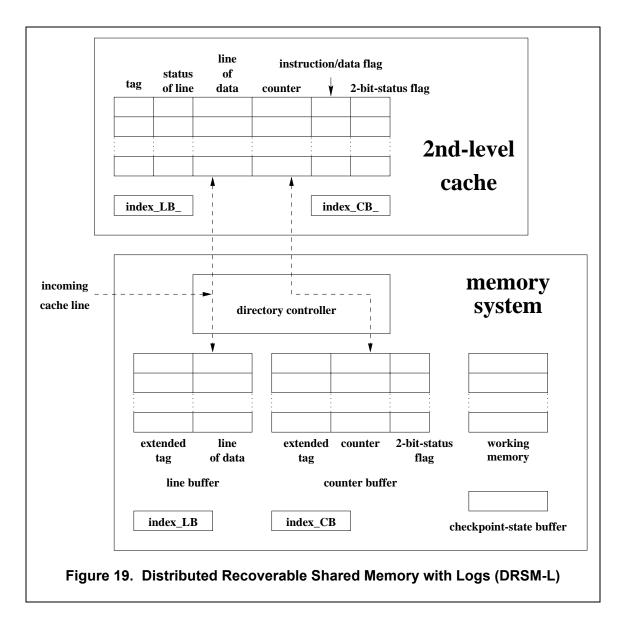

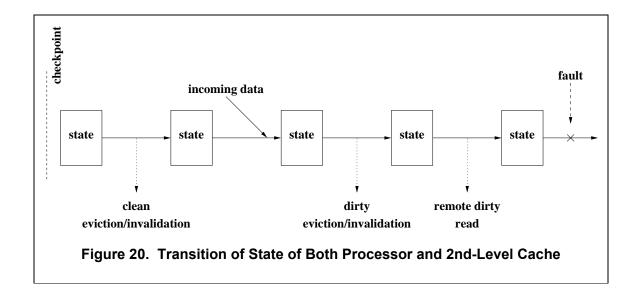

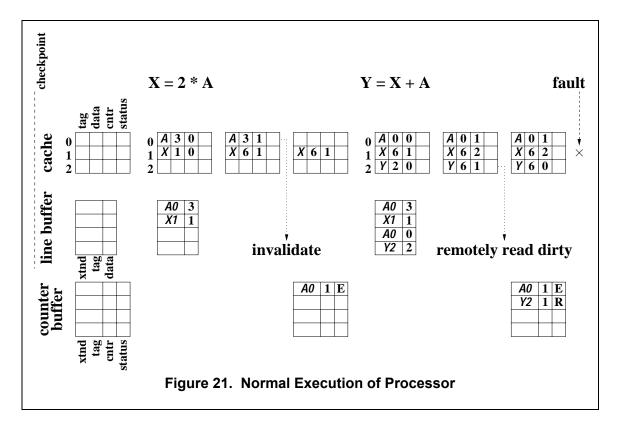

Figure 11 shows the new organization of the TCMP with DRSM. Each DRSM module no longer contains the checkpoint counter. We replace it with the 2-bit-state register, which indicates the state of its corresponding memory block. For each block, the 2-bit-state register transitions among the states indicated in figure 12. When a 2nd-level cache issues an EXCLUSIVE access to a block in the state of "PC", the 2-bit-state register transitions from "PC" to "W".

The DRSM module also has a checkpoint-state buffer. The checkpoint-state buffer contains 3 units (not shown in figure 11): the 2-bit checkpoint flag, the tentative-checkpoint area, and the permanent-checkpoint area. The checkpoint flag indicates the status of the local processor and holds 1 of 3 possible values: "CHECKPOINT\_IS\_NOT\_ACTIVE", "TENTATIVE\_CHECKPOINT\_IS\_ACTIVE", and "PERMANENT\_CHECKPOINT\_IS\_ACTIVE". The tentative-checkpoint area holds the internal state of the local processor for the tentative checkpoint, and the permanent-checkpoint area holds the internal state of the local processor for the permanent checkpoint.

The dependency array contains 1 entry for each processor in the TCMP. If a processor writes data into the memory module, then the directory controller sets the corresponding entry of the dependency array to 1. Also, if (1) a processor reads data and (2) this event causes a dependency to arise and, hence, to be recorded in the dependency matrix, then the directory controller sets the corresponding entry of the dependency array to 1.

In figure 11, the structure with the label of "processor lock" contains 1 lock per processor in the TCMP. The DRSM module sets the processor lock to "1" if a processor querying the memory module during the establishment of the tentative checkpoint has an entry of "1" in the dependency array; an entry of "1" in the dependency array indicates that the processor (1) is a writer of a dirty block in the memory module or (2) has dependent processors, according to the dependency matrix. During the establishment of the permanent checkpoint, if an incoming memory access originates from a processor with its processor lock being "1", the DRSM module negatively acknowledges that request. This action prevents a race from developing on the dependency matrix.

One example of a race is the following. Suppose that processor "P[1]" finishes its permanent checkpoint before a memory module "DRSM[2]" completes its permanent checkpoint and that "P[1]" has its processor lock being "1" in "DRSM[2]". Suppose that "P[3]" writes into a memory block (in "DRSM[2]") that is not part of the checkpoint which is just completing. Then, processor "P[1]" reads that same block before "DRSM[2]" completes its permanent checkpoint. The dependency "P[1]  $\rightarrow$  P[3]" will be lost when "DRSM[2]" completes its permanent checkpoint, clearing the row and column (of the dependency matrix) containing "P[1]".

### 4.5. Triggers of Checkpoint Establishment

Two events can trigger the establishment of a checkpoint.

- 1. timer-triggered checkpoint: A timer expires. When the timer for a processor expires, it establishes a checkpoint. The timer ensures a maximum bound on the time interval between checkpoints.

- 2. external-communication-triggered checkpoint: Communication occurs between a processor and the environment outside of the TCMP. When data leaves or enters a TCMP, the processor handling the data must establish a checkpoint. Communication includes interrupts.

#### 4.6. Establishing Tentative Checkpoints

#### 4.6.1. General Overview

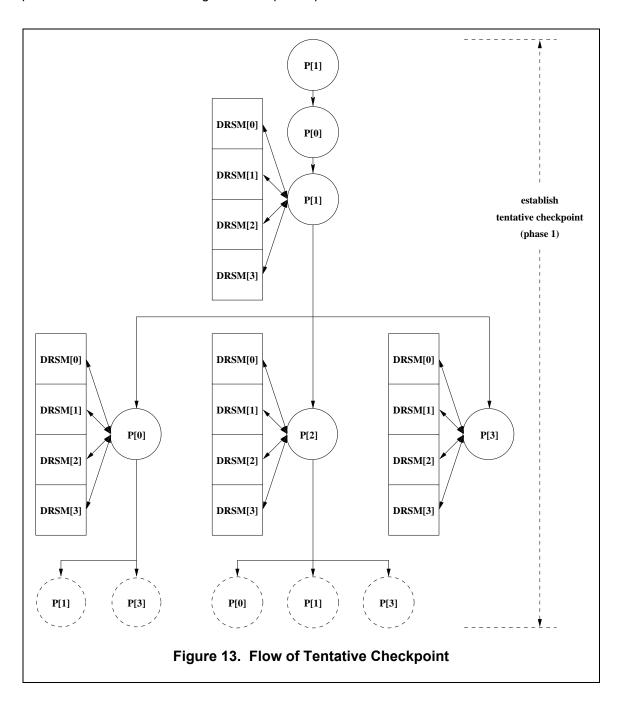

Unlike RSM, DRSM has several memory modules, so we must radically modify the algorithm for establishing a tentative checkpoint. Figure 13 shows the new algorithm. Its general strategy is that a processor wishing to establish a checkpoint must query all DRSM modules to determine all

dependent processors that must also establish a checkpoint. They, in turn, query all DRSM modules to determine additional dependent processors. The process proceeds in the fashion of an expanding tree of processors. The root of the tree is the processor that initially wished to establish a checkpoint, and the leaves of the tree are processors that either (1) have no checkpoint-dependent processors or (2) have already been identified higher up in the tree. Once the algorithm reaches the leaves of the tree, processors starting from the bottom of the tree and moving upwards toward the root send acknowledgment messages to the parent processor. A parent processor must first receive acknowledgments from all its children before that parent processor sends an acknowledgment to its parent processor.

#### 4.6.2. Details

As a specific example, we trace the flow in figure 13 for a 4-processor TCMP. We arbitrarily select processor "P[0]" to act as an arbiter to allow at most one tentative checkpoint to be established at any time. "P[1]" submits a request to "P[0]" to obtain permission to establish a checkpoint. "P[0]" grants the request, and "P[1]" proceeds to establish a tentative checkpoint (in the first phase).

"P[1]" queries all the DRSM modules. They search their dependency matrices to find all processors which must establish a checkpoint along with "P[1]". The DRSM modules send their replies back to "P[1]". From their replies, "P[1]" discovers that "P[0]", "P[2]", and "P[3]" must establish checkpoints. "P[1]" requests all of them to establish tentative checkpoints. In this example, "P[0]", "P[2]", and "P[3]" receive the request from "P[1]" at approximately the same time (although this situation need not always arise).

"P[0]" then queries all the DRSM modules to find that both "P[1]" and "P[3]" are dependent upon it. "P[0]" requests them to establish tentative checkpoints. Upon receiving this request from "P[0]", both "P[1]" and "P[3]" respond that they have already joined the checkpoint tree and are, hence, leaves in this tree.

After receiving the request from "P[1], "P[2]" then queries all the DRSM modules to find that "P[0]", "P[1]", and "P[3]" are dependent upon it. "P[2]" requests them to establish tentative checkpoints. Upon receiving this request from "P[2]", all 3 processors – "P[0]", "P[1]", and "P[3]" – respond that they have already joined the checkpoint tree and are, hence, leaves in this tree.

Finally, after receiving the request from "P[1]", "P[3]" then queries all the DRSM modules to find that no processors are dependent on it. Hence, "P[3]" is a leaf in this tree. After "P[3]" completes its tentative checkpoint, "P[3]" sends an acknowledgment back to "P[1]".

After "P[0]" completes its tentative checkpoint, "P[0]" sends an acknowledgment back to "P[1]". After "P[2]" completes its tentative checkpoint, "P[2]" sends an acknowledgment back to "P[1]". After "P[1]" receives acknowledgments from "P[0]", "P[2]", and "P[3]", "P[1]" concludes the establishment of the tentative checkpoint, which is phase #1.

Figure 13 shows the general flow in the process of establishing a tentative checkpoint but omits 6 important details. They are the following.

- Before a processor queries all DRSM modules (in order to determine dependent processors), it (1) waits until all its pending cache operations are finished or negatively acknowledged and (2) then writes all dirty cache data back into memory. The processor waits for the DRSM modules to acknowledge that all the write-backs are complete.

- 2. Each processor sends a copy of its state (i. e. data in the internal registers) to the checkpoint-state buffer of the DRSM module that is local to the processor.

- 3. A DRSM module that receives a query (to determine dependent processors) waits until all pending memory operations by the directory controller are finished before the DRSM module replies (with information about dependent processors) to the querying processor. During this waiting period, the DRSM module negatively acknowledges all requests that it receives.

- 4. Just before the DRSM module replies to the querying processor, the DRSM module scans for all memory blocks (in the working bank of memory) where (1) the state is "W" and (2) the last writer is the querying processor. If such memory blocks exist, then the DRSM module transitions the state from "W" to "TC". The DRSM module negatively acknowledges accesses to blocks for which the state is "TC". Locking out accesses to such blocks prevents changes in the checkpoint dependencies of the processors that have almost completed the tentative checkpoint.

- 5. In addition, the DRSM module sets the processor lock of the querying processor to "1" if the corresponding entry in the dependency array is "1". The DRSM module negatively acknowledges normal memory accesses originating from a processor with its processor lock being "1". The aim is to prevent a race condition from developing in the dependency matrix when the processor finishes its permanent checkpoint before the DRSM module finishes its own permanent checkpoint.

- 6. Just before the root processor of the checkpoint tree begins the establishment of the tentative checkpoint, that processor sets a 2-bit checkpoint flag in the checkpoint-state buffer of the local memory module to indicate that the establishment of the tentative checkpoint is active. The state of the checkpoint flag can be 1 of {CHECKPOINT\_IS\_NOT\_ACTIVE, TENTATIVE\_CHECKPOINT\_IS\_ACTIVE, PERMANENT\_CHECKPOINT\_IS\_ACTIVE}. In figure 13, processor "P[1]" sets the checkpoint flag to "TENTATIVE\_CHECKPOINT\_IS\_ACTIVE". The TCMP uses this state information to determine what to do in the event that a fault occurs during the establishment of a checkpoint.

## 4.6.3. Dependent Processors and Dependent DRSM Modules

The acknowledgments that are propagated from the leaves of the checkpoint tree up to the root in figure 13 lists the dependent processors. Each processor in the tree determines processors that are checkpoint dependent upon itself, packages this information along with all dependent-processor information from the child processors, and passes this package of information in an acknowledgment to the parent processor. In the end, the root processor is aware of all dependent processors in the entire tree.

The tree also propagates information about dependent DRSM modules to the root processors. A DRSM module is a dependent DRSM module if the entry for the querying processor in the dependency array is set to "1".

When the DRSM module replies (with information about the dependent processors) to the querying processor, the DRSM module also sends information (to the querying processor) indicating whether the module is a dependent memory module. The querying processor propagates this information about dependent DRSM modules back up to the root processor of the checkpoint tree.

#### 4.7. Establishing Permanent Checkpoints

#### 4.7.1. General Overview

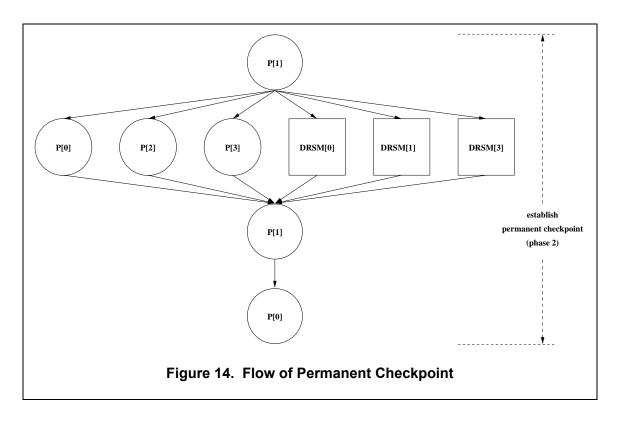

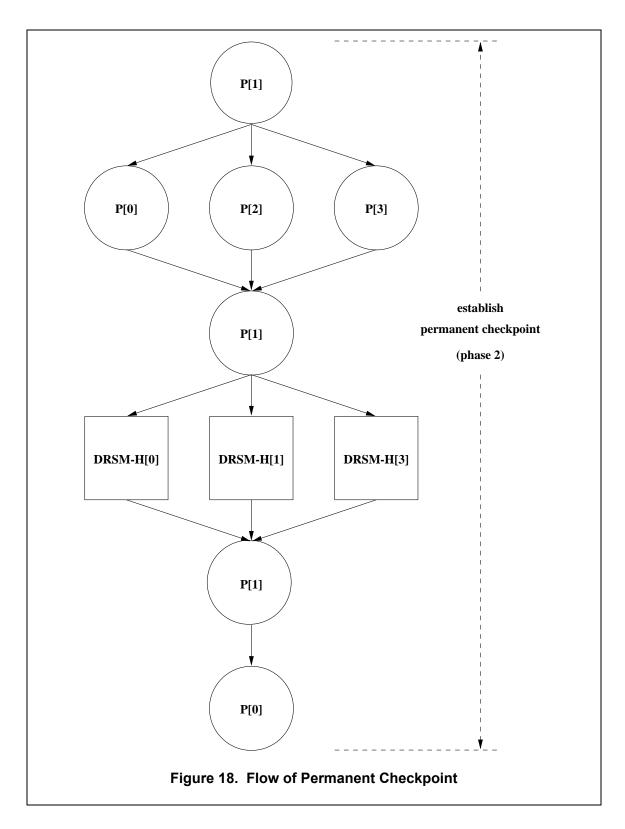

Figure 14 shows the new algorithm for establishing a permanent checkpoint for a 4-processor TCMP. The general strategy is that the root processor in the checkpoint tree for the tentative checkpoint guides the establishment of the permanent checkpoint. The root processor requests all dependent processors and all dependent DRSM modules to establish a permanent checkpoint. Once they complete their permanent checkpoint, they send acknowledgments to the root processor. It then completes its own permanent checkpoint and sends an acknowledgment to the arbiter processor. It removes the root processor from the queue.

## 4.7.2. Details

As a specific illustration, we trace the flow in figure 14. "P[1]" is the root processor of the checkpoint tree for the tentative checkpoint. From it, "P[1]" knows that "P[0]", "P[2]", and "P[3] are dependent processors and that "DRSM[0]", "DRSM[1]", and "DRSM[3]" are dependent DRSM modules. In this particular example, "DRSM[2]" is not a dependent DRSM module. "P[1]" tells all dependent processors and DRSM modules to establish a permanent checkpoint. Each of "DRSM[0]", "DRSM[1]", and "DRSM[3]" performs the following. The DRSM module resets (to 0) all columns and all rows (in the dependency matrix) containing any processor with its processor lock being "1". Next, the DRSM module identifies all blocks (in the working memory) for which their states are "TC". The DRSM module transitions their states to "PC" and copies the contents of the blocks from the working memory into the corresponding blocks in the permanent-checkpoint memory. Finally, the DRSM module sends an acknowledgment to the root processor.

After receiving the request to establish a permanent checkpoint, each of "P[0]", "P[2]", and "P[3]" sends an acknowledgment back to the root processor and resumes normal processing. After "P[1]" receives acknowledgments from all dependent processors and all dependent memory modules, "P[1]" itself sends an acknowledgment to the arbiter processor, "P[0]", and resumes normal processing. "P[0]" then grants the request from the next processor wishing to establish a checkpoint.

We should note the following additional details. "P[1]" sets the checkpoint flag to "PERMANENT\_ CHECKPOINT\_IS\_ACTIVE" just before "P[1]" begins the phase for the establishment of the permanent checkpoint. The dependent DRSM modules clear all the processor locks to "0" during phase 2. After the establishment of the permanent checkpoint is complete, "P[1]" sets the checkpoint flag to "CHECKPOINT\_IS\_NOT\_ACTIVE". Also, each processor tells its local memory module to designate the tentative checkpoint of the processor state in the checkpoint-state buffer as a permanent checkpoint. The processor does not wait for an acknowledgment from the local memory module before sending an acknowledgment to "P[1]" since the network is reliable.

## 4.8. Additional Features

## 4.8.1. Artificially Dependent Processors

If the establishment of a checkpoint is in progress, the arbiter queues requests from processors that request permission to establish a checkpoint. After the arbiter receives an acknowledgment that the establishment of the current checkpoint is complete, the arbiter grants the next processor (waiting in the checkpoint-request queue) permission to establish a checkpoint. There can be many processors waiting in the queue.

If more than 1 processor waits in the queue, the arbiter grants permission to the processor at the front of the queue but requests that processor, say "P[1]", to artificially treat all the other processors (in the queue) as being dependent on it. After "P[1]" finishes querying the DRSM modules to find the genuinely dependent processors, "P[1]" adds the artificially dependent processors to this group of genuinely dependent processors. Then, "P[1]" requests that all of them establish tentative checkpoints.

In this way, any processor that submits a request to establish a checkpoint to the arbiter processor needs to wait at most approximately the period for establishing one checkpoint. That one checkpoint is the one that is currently being established when the request arrives at the arbiter.

#### 4.8.2. Arbiter

The algorithm for the DRSM uses an arbiter, which is "P[0]" in our example. Although the arbiter appears to be a potential bottleneck in the TCMP, the arbiter actually does not cause a problem. The maximum number of requests (for the establishment of checkpoints) that can queue at the arbiter is "(number of processors in the TCMP) - 1". After the current establishment of a checkpoint completes, the arbiter requests the processor, say "P[2]", of the first request in the queue to begin the establishment of a checkpoint. If there are other requests in the queue, the arbiter requests "P[2]" to include their corresponding processors as artificially dependent processors. In other words, after the current establishment of a checkpoint completes, all processors with requests waiting in the queue participate in the next establishment of a checkpoint, clearing the entire queue. The maximum delay between (1) the arrival of a request at the arbiter and (2) the participation (in the establishment of a checkpoint) by the processor submitting the request is approximately the time required for the current establishment of a checkpoint to complete.

## 4.9. Recovery from a Fault

We consider the following simple scheme for rolling back from a fault experienced by a processor. We arrange for a special recovery-logic circuit on the memory module to periodically send "Are you alive?" messages to the local processor. If it does not respond within a specified timeout period, the recovery-logic circuit assumes that the processor experienced a fault. If the fault is permanent, the recovery-logic circuit replaces the failed processor with the spare processor. Then, the recovery-logic circuit resets the processor, say "P3", and directs it to begin the recovery activity. "P3" negatively acknowledges all cache-coherence messages from the directory controllers until recovery is complete.

"P3" requests the arbiter processor to disallow the establishment of any checkpoint until the recovery is complete. If a checkpoint is currently being established, then "P3" waits until the checkpoint is either completed or aborted. A checkpoint will be aborted if (1) "P3" is a member of the checkpoint tree and (2) the root processor (of the checkpoint tree) has its checkpoint flag being "TENTATIVE\_CHECKPOINT\_IS\_ACTIVE". Otherwise, the checkpoint will be completed. In particular, if (1) "P3" is a member of the checkpoint tree but (2) the root processor (of the checkpoint tree) has its checkpoint flag being "PERMANENT\_CHECKPOINT\_IS\_ACTIVE", then the checkpoint will be completed.

Then, "P3" checks the checkpoint flag of the local checkpoint-state buffer. Suppose that the state of the checkpoint flag is "CHECKPOINT\_IS\_NOT\_ACTIVE", meaning that "P3" did not fail during the establishment of a checkpoint. "P3" must query the dependency matrix of each DRSM module in order to determine all other processors that must also roll back to the last permanent checkpoint. "P3" spawns a recovery tree that is similar to the checkpoint tree (i. e. processor tree) generated during the establishment of a tentative checkpoint. Then, "P3" must perform the following activities. They apply as well to all other processors that are in the recovery tree. First, "P3" invalidates all entries in its cache and requests all the directory controllers to update their directories to indicate that "P3" does not have memory blocks in its cache. Then "P3" tells the memory modules (1) to transition the 2-bit-state registers from state "W" to state "PC" and (2) to copy data from the permanent-checkpoint memory into the working memory for all blocks where "P3" is the active writer. "P3" then loads the processor state stored in the permanent-checkpoint area of the checkpoint-state buffer and resumes execution.

Now, suppose that the state of the checkpoint flag is "PERMANENT\_CHECKPOINT\_IS\_ ACTIVE", meaning that "P3" failed during the establishment of a permanent checkpoint. Then "P3" completes the permanent checkpoint, telling the memory modules to transition the 2-bit-state registers from state "TC" to state "PC" for all blocks where "P3" is the active writer. "P3" tells the checkpoint-state buffer to designate the processor state saved in the tentative-checkpoint area as

the permanent checkpoint. "P3" invalidates all entries in its cache and requests all the directory controllers to update their directories to indicate that "P3" does not have memory blocks in its cache. "P3" then loads the processor state stored in the permanent-checkpoint area of the checkpoint-state buffer and resumes execution.

Finally, suppose that the state of the checkpoint flag is "TENTATIVE\_CHECKPOINT\_IS\_ ACTIVE", meaning that "P3" failed during the establishment of a tentative checkpoint. "P3" along with all the other processors in the checkpoint tree must discard this tentative checkpoint and roll back to their previous permanent checkpoint. The roll-back of each processor generates its own recovery tree of processors; all the recovery trees can be combined into 1 huge recovery tree where all participating processors can recover concurrently. Then, "P3" must perform the following activities. They apply as well to all other processors that are in the recovery tree. First, "P3" invalidates all entries in its cache and requests all the directory controllers to update their directories to indicate that "P3" does not have memory blocks in its cache. Then "P3" discards the tentative checkpoint, telling the memory modules (1) to transition the 2-bit-state registers from both state "W" and state "TC" to state "PC" and (2) to copy data from the permanent-checkpoint memory into the working memory for all blocks where "P3" is the active writer. "P3" tells the checkpoint-state buffer to invalidate the processor state saved in the tentative-checkpoint area. "P3" then loads the processor state stored in the permanent-checkpoint area of the checkpoint-state buffer and resumes execution.

# Chapter 5. Distributed Recoverable Shared Memory for Communication Checkpoints (DRSM-C)

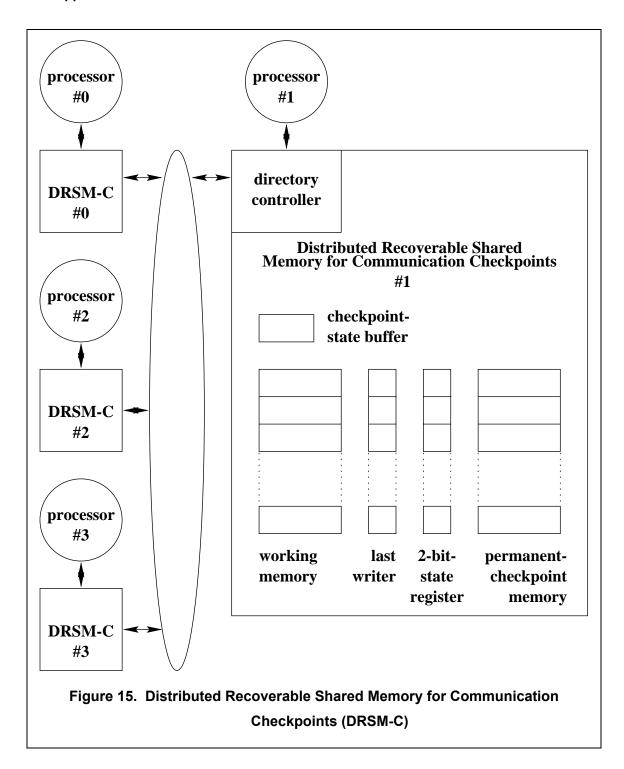

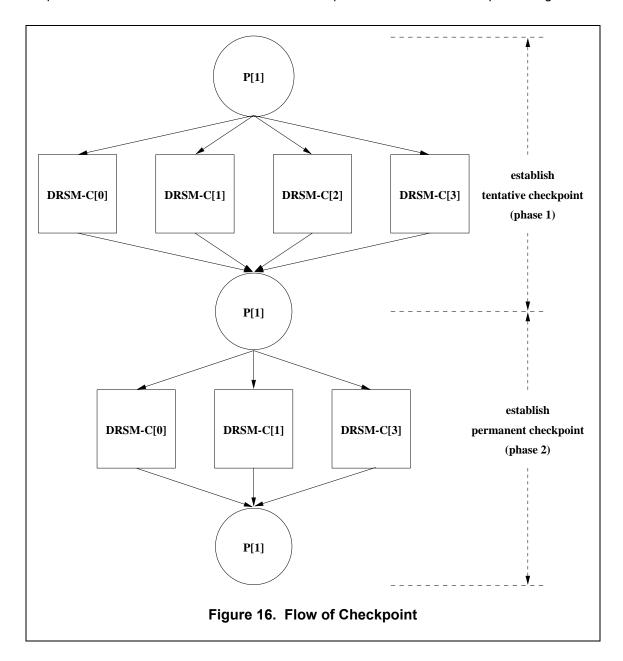

#### 5.1. Introduction

The distributed recoverable shared memory for communication checkpoints (DRSM-C) is our 2nd apparatus and algorithm for establishing checkpoints. The DRSM-C is a tightly synchronized method. Unlike the DRSM, the DRSM-C does not record dependencies that arise among processors as they access the same memory block. Hence, the DRSM-C requires that a processor immediately establishes a checkpoint if another processor reads or writes a block (of memory) to which the former processor wrote data. In addition, to establish a maximum bound on the temporal interval between the checkpoints for a processor, we use a timer to announce when the processor must establish a checkpoint. Any interaction between an application process and the environment of the TCMP also causes the establishment of a checkpoint.

## 5.2. Prior Work

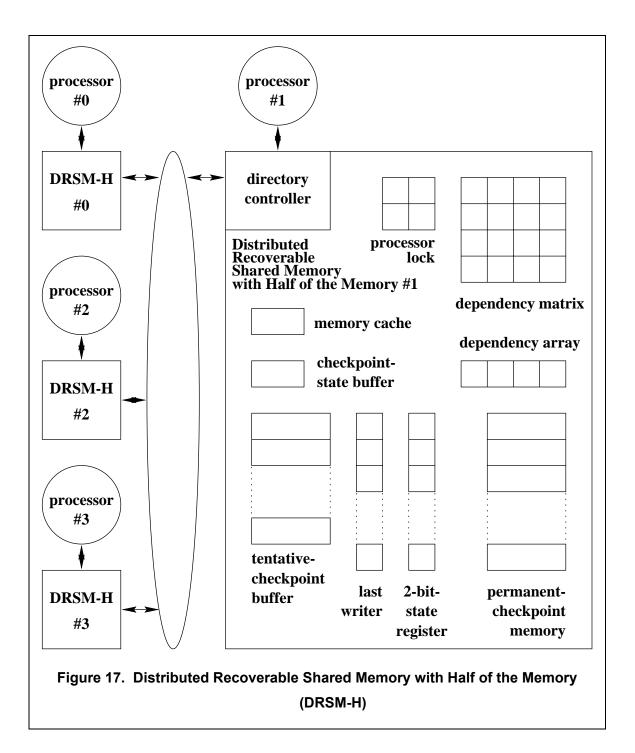

Wu also proposes an apparatus and algorithm in the class of the tightly synchronized method, but his scheme differs from DRSM-C in 2 aspects. First, Wu uses a TCMP with both fault-tolerant caches and exactly 1 bank of fault-tolerant memory [17]. By contrast, our TCMP has caches that are not fault-tolerant, but our system does have 2 banks of fault-tolerant memory.